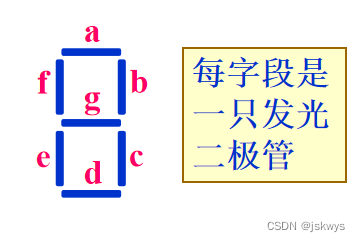

七段数码管常用于计时器、拨码开关输入、班级和学号等信息的显示,通过控制不同的段亮灭,可以实现各种数字和字符的显示。七段数码管通常由a-g七个段组成,每一段对应一个LED。为了显示不同的数字,需要控制这些LED的亮灭。

图1 七段数码管

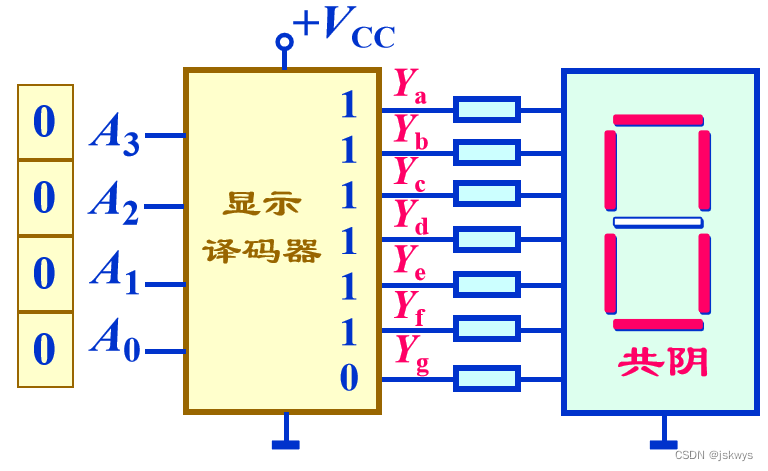

为了控制这些LED的亮灭,需要设计一个显示译码器。显示译码器的作用是将输入的编码数据转换为控制7段数码管LED亮灭状态的输出信号。译码器接收来自微控制器或其他电路的数字信号,并根据预设的逻辑规则将这些信号转换为对应的控制信号。这些控制信号随后被应用到7段数码管的LED段上,从而实现数字或字符的显示。

1. 定义输入输出:

输入:一个4位宽的二进制数,表示要显示的数字(0-9)。

输出:七个信号,分别控制七段数码管的a-g段。

2.编写Verilog代码:

创建一个Verilog模块,定义输入输出端口。

使用case语句或查找表(LUT)来实现译码逻辑。

对于每个输入值(0000到1001),指定对应的输出值(LED亮灭组合)。

3.编译与仿真:

使用Verilog编译器将代码编译成可在模拟器上运行的目标文件。

创建测试平台(testbench),生成输入信号并观察输出信号。

运行仿真,验证译码器的功能是否正确。

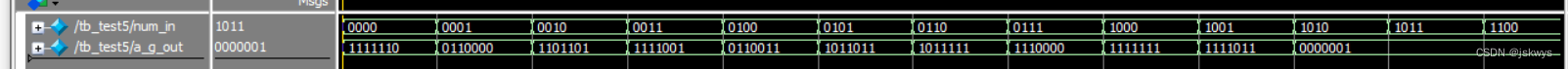

4.结果分析:

检查仿真结果,确保对于每个输入值,输出信号都正确对应了七段数码管的显示。

设计模块:

module test5(num,a_g);

input[3:0] num;

output[6:0] a_g; // a_g -->{a,b,c,d,e,f,g}

reg[6:0] a_g; // always赋值需要定义为reg变量

always@(num)begin // 敏感变量,需要变的量是输入num

case(num)

// 4'd0:4位宽的十进制('d),数值为0:0000,4'd8:4位宽的十进制('d),数值为8:1000

// 'b 二进制,'h十六进制,'d十进制。eg 10'd15,则表示十进制15, 0000001111。

4'd0: begin a_g <= 7'b111_1110; end // a-g7根管a-f亮,g不亮(0)

4'd1: begin a_g <= 7'b011_0000; end

4'd2: begin a_g <= 7'b110_1101; end

4'd3: begin a_g <= 7'b111_1001; end

4'd4: begin a_g <= 7'b011_0011; end

4'd5: begin a_g <= 7'b101_1011; end

4'd6: begin a_g <= 7'b101_1111; end

4'd7: begin a_g <= 7'b111_0000; end

4'd8: begin a_g <= 7'b111_1111; end

4'd9: begin a_g <= 7'b111_1011; end

default:begin a_g <= 7'b000_0001; end // 输入超过9,输出“中杠”

endcase

end

endmodule测试文件:

`timescale 1ns/10ps

module tb_test5;

reg[3:0] num_in;

wire[6:0] a_g_out;

test5 my_test5(.num(num_in),.a_g(a_g_out));

initial begin

num_in = 0; // 初始化输入

#3000 $stop; // 4位输入_ _ _ _,16种变化,10ns一个变化,200ns即可

end

always #10 num_in <= num_in+1; // 10ns变化一次

endmodule

仿真波形:

3192

3192

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?