1.ODT

ODT操作的原因(总结就是是为了让DQS、RDQS、DQ和DM信号在终结电阻处消耗完,防止这些信号在电路上形成反射,进而增强信号完整性。实际上如果在一些先进分装下,走线足够的近,这种情况下即使不打开ODT同样信号质量也不会有问题,当然关闭ODT最大的好处就是减少功耗):

DDR3中的ODT(On-die termination) - aerguqiuhui - 博客园 (cnblogs.com)

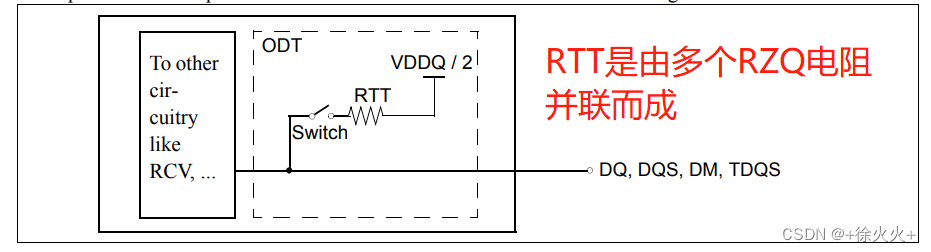

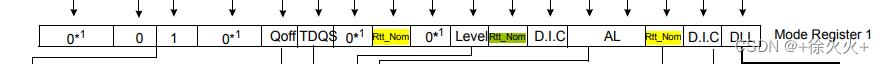

选择完这个电阻之后,可以通过每个rank的ODT信号线来将这个功能打开(如果这个电阻不选的化,即使ODT信号拉起,也相当于没有打开这个功能,一般来说,ODT电阻配置为60欧姆)。一个rank只会有一个ODT信号(pin),也就是说一个rank内部的多个memory颗粒共用这个ODT信号。在进入到自刷新的模式下,需要将ODT的功能关闭(自刷新模式本来就是一个低功耗的模式,将ODT打开之后会有大量电流走过RTT电阻,增加功耗)。

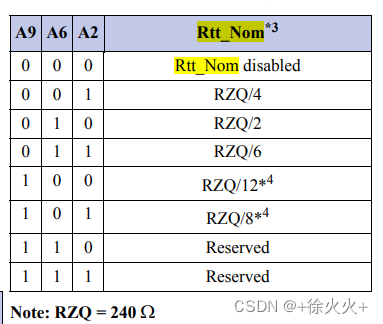

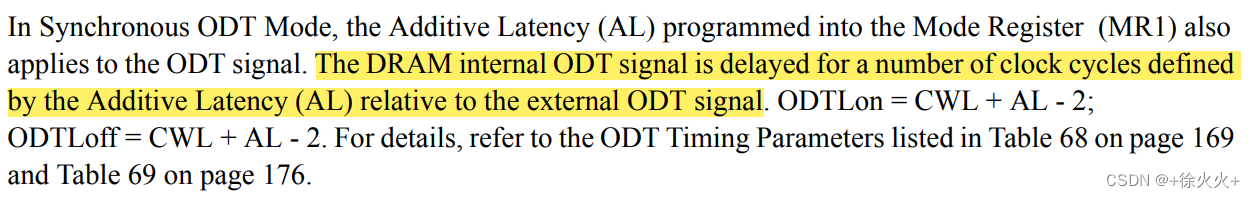

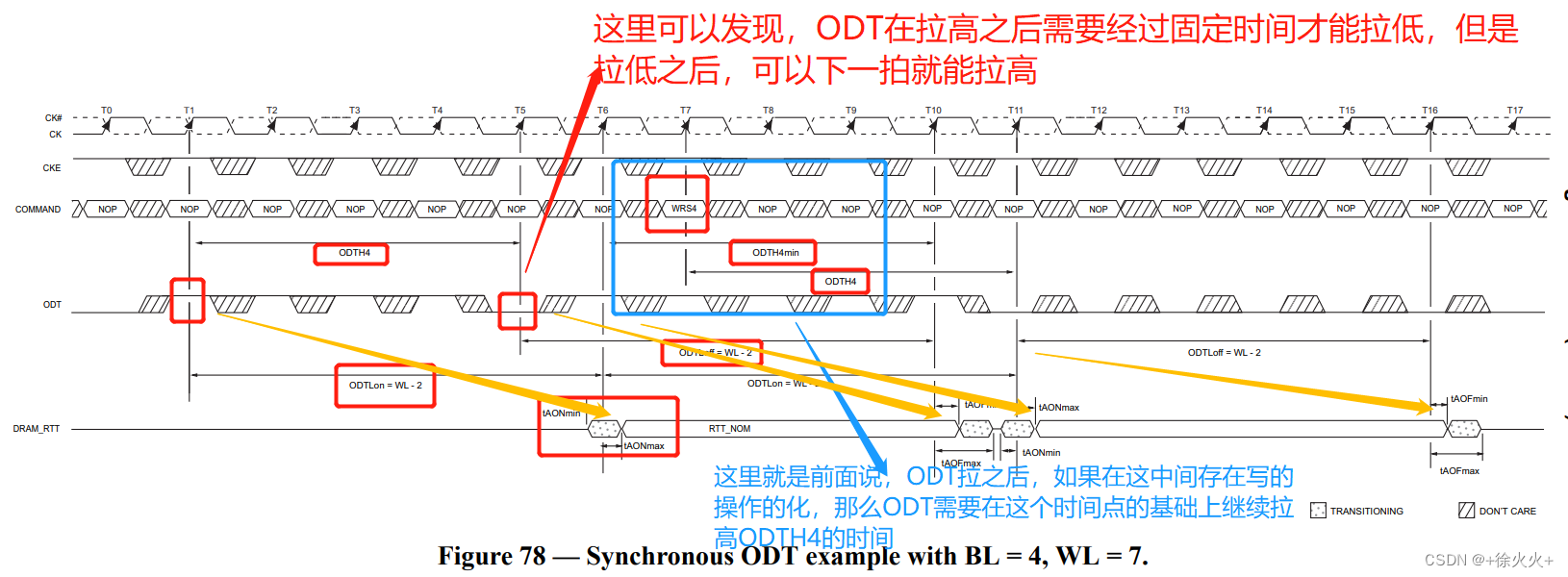

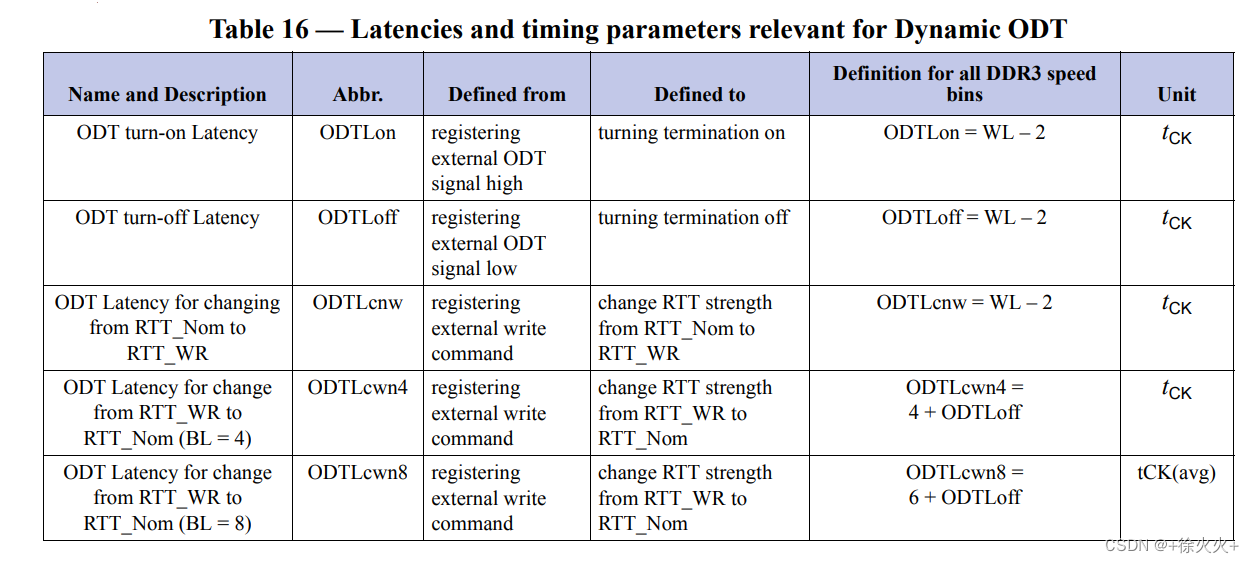

(1)同步ODT:RTT电阻的打开和关闭是通过clk去采样ODT信号,也就是打开和关闭过程完全是和clk同步的,在采样到ODT信号为高的情况下(上升沿),经过ODTLon时间(WL-2,write latency - 2)之后,RTT打开;如果采样到ODT信号为低(上升沿),经过ODTLof时间(WL-2,write latency - 2)之后,RTT关闭。

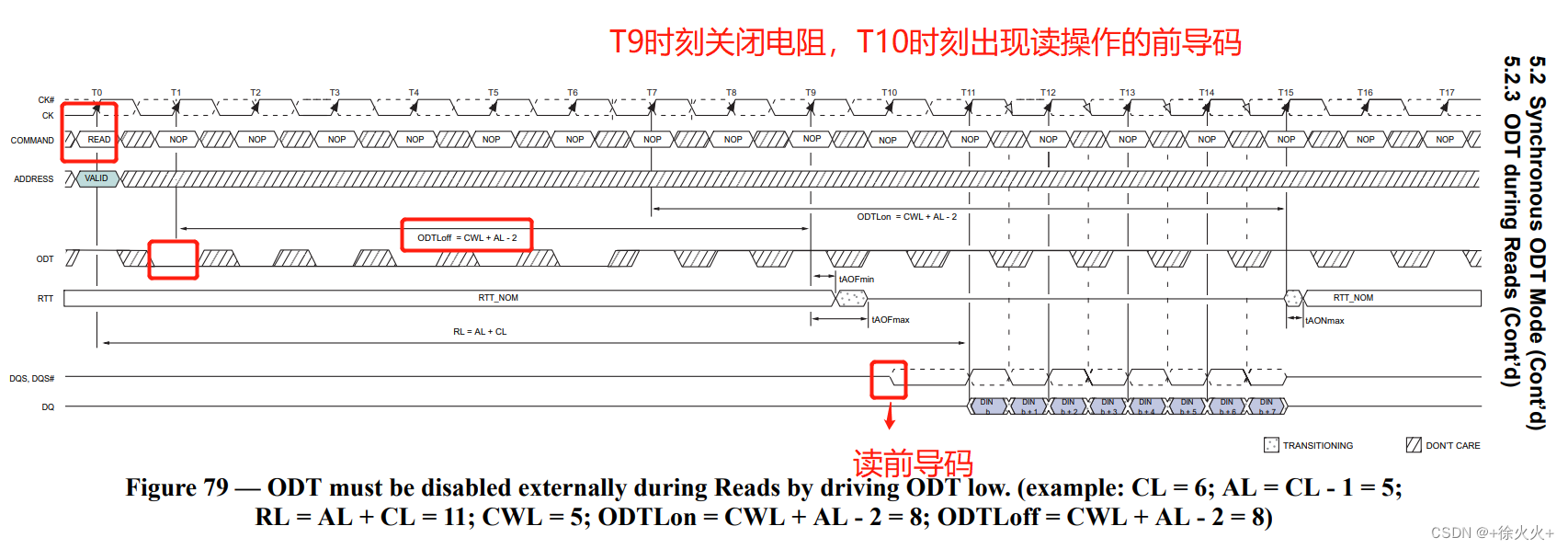

同步ODT操作的前提是需要DLL打开,并且是lock的。ODT操作是仅仅只在写操作的情况下会用到,读的情况下需要将其关闭,协议规定,至少需要在读前导码的前半个周期将ODT功能关闭(也就是将RTT电阻关闭)。

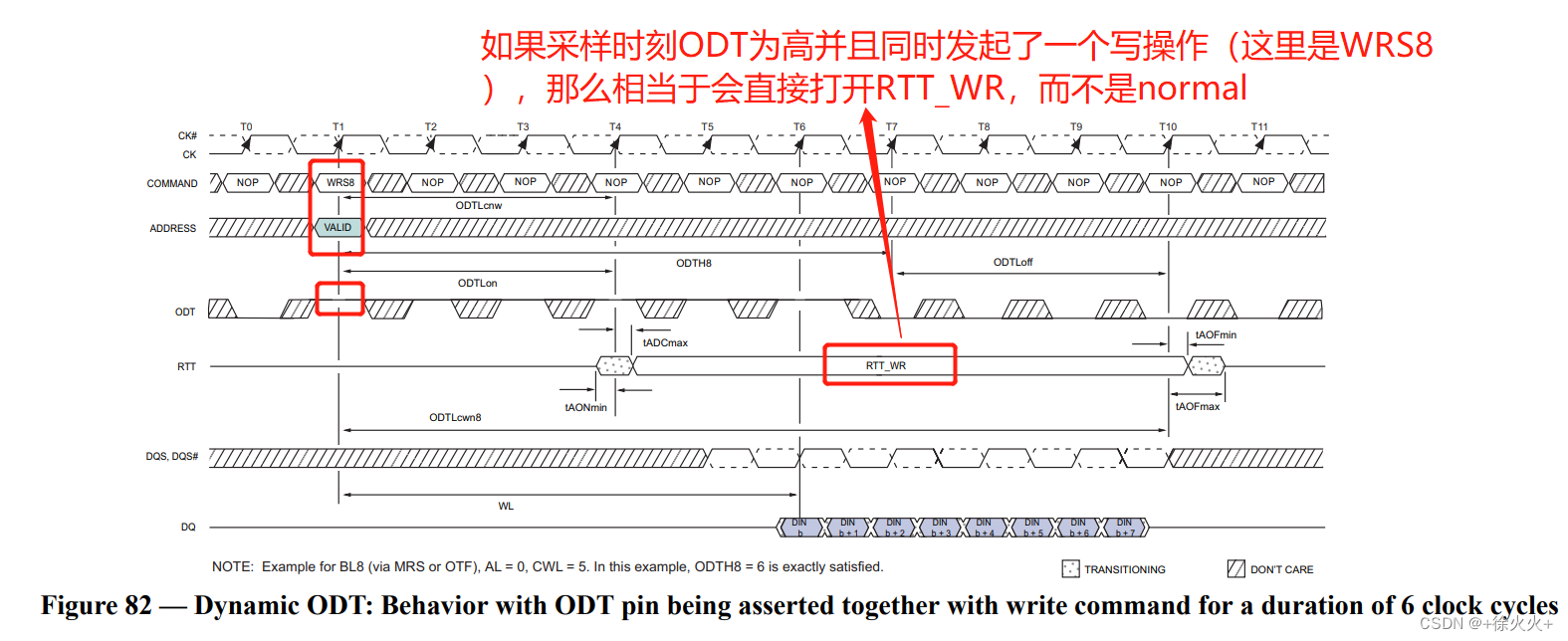

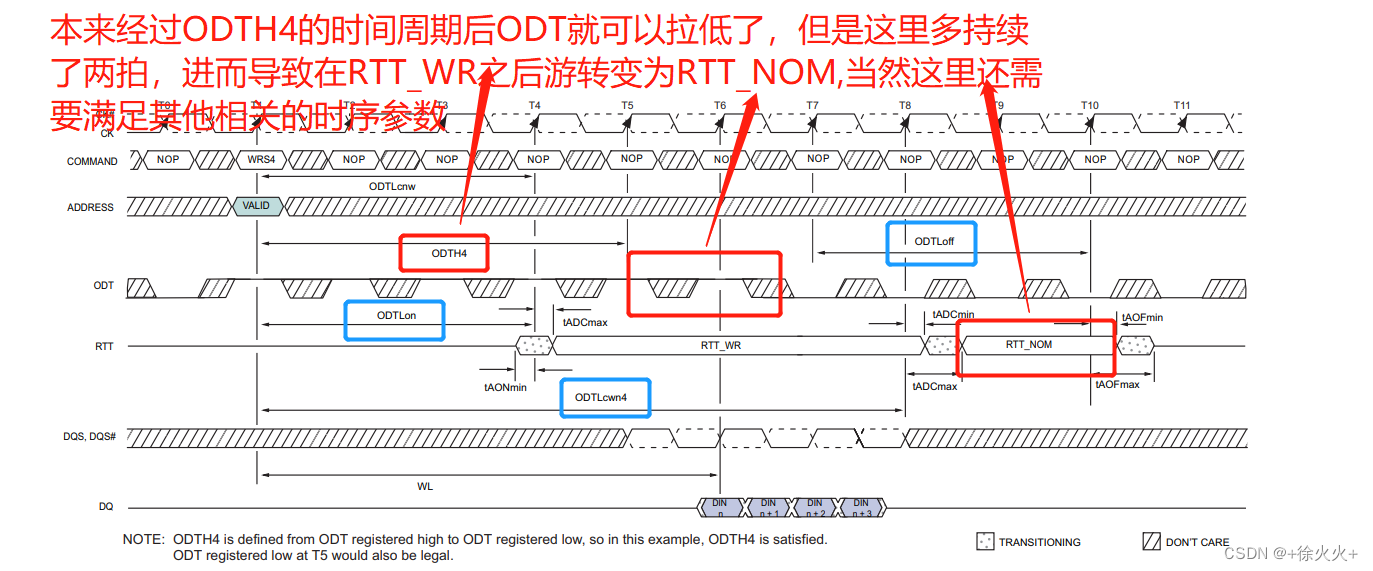

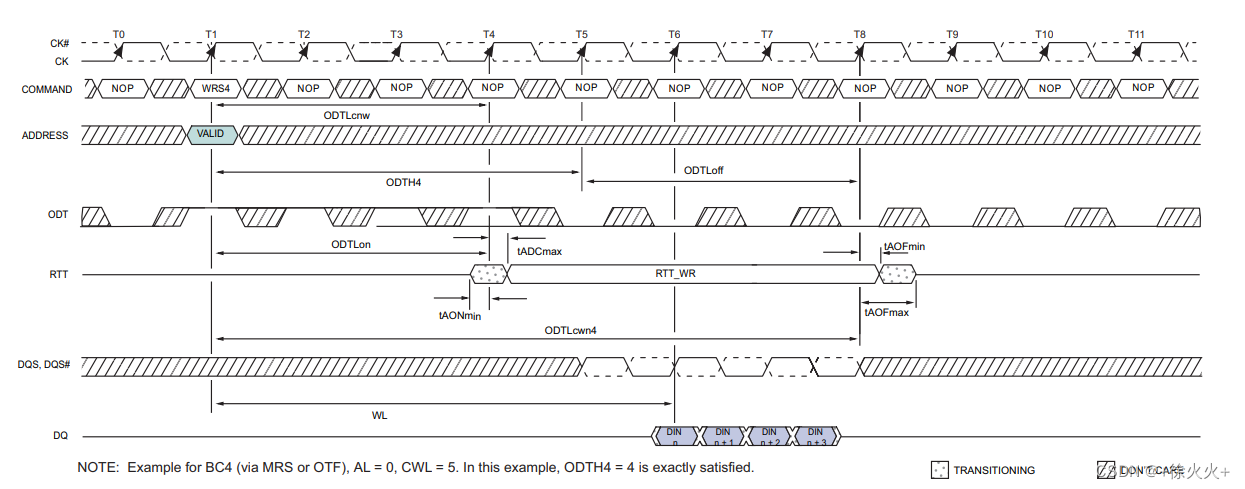

另外,需要注意的是,如果ODT为高的情况下发起了一个写的操作,那么ODT必须在写操作结束之后持续拉高一段时间,针对BL4(burst length为4)的写操作,ODT信号继续需要继续拉高ODTH4的时间,针对BL8的写操作,ODT信号需要继续拉高ODTH8的时间。

上图中不同于计算公式WL-2的原因在于存在additive latency。

这里有个问题,什么叫外部的ODT信号,什么叫内部的ODT信号???

读操作情况下的ODT:

由于在读操作下对ODT的限制,因此往往只会在写操作的情况去将ODT信号拉高,只要不是写操作了,就会把ODT信号拉低。

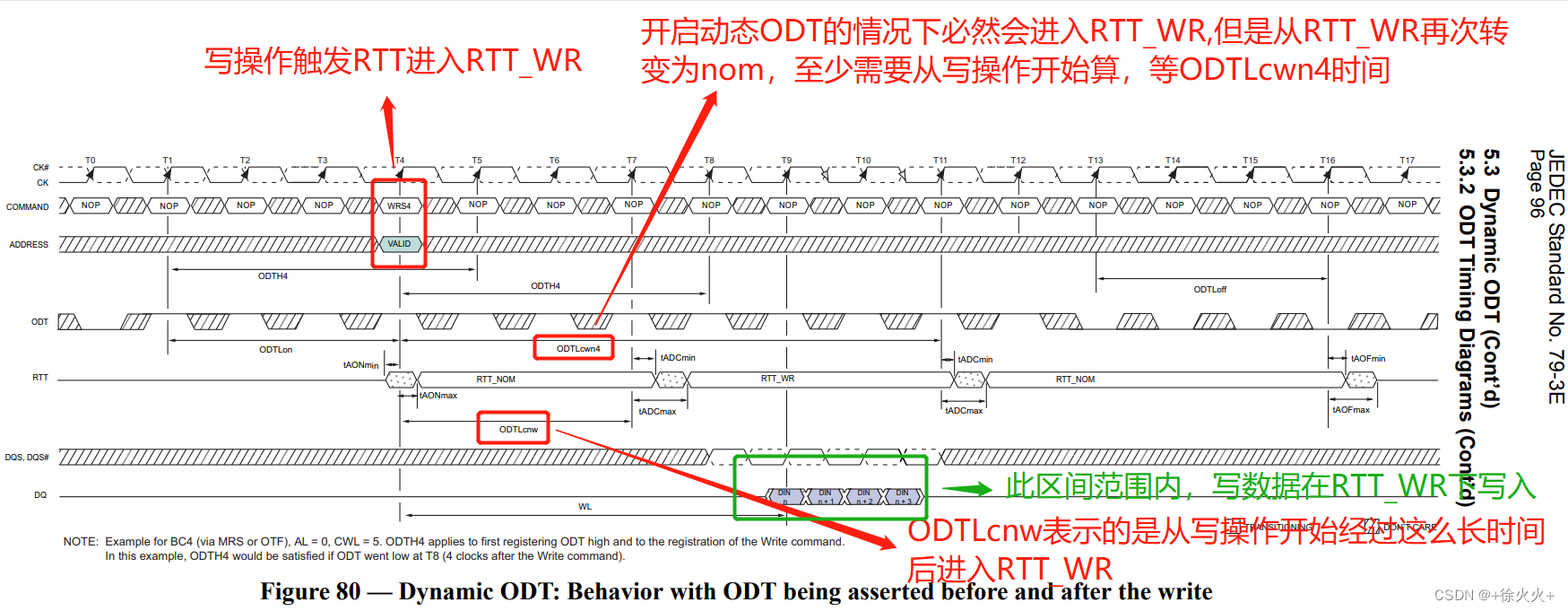

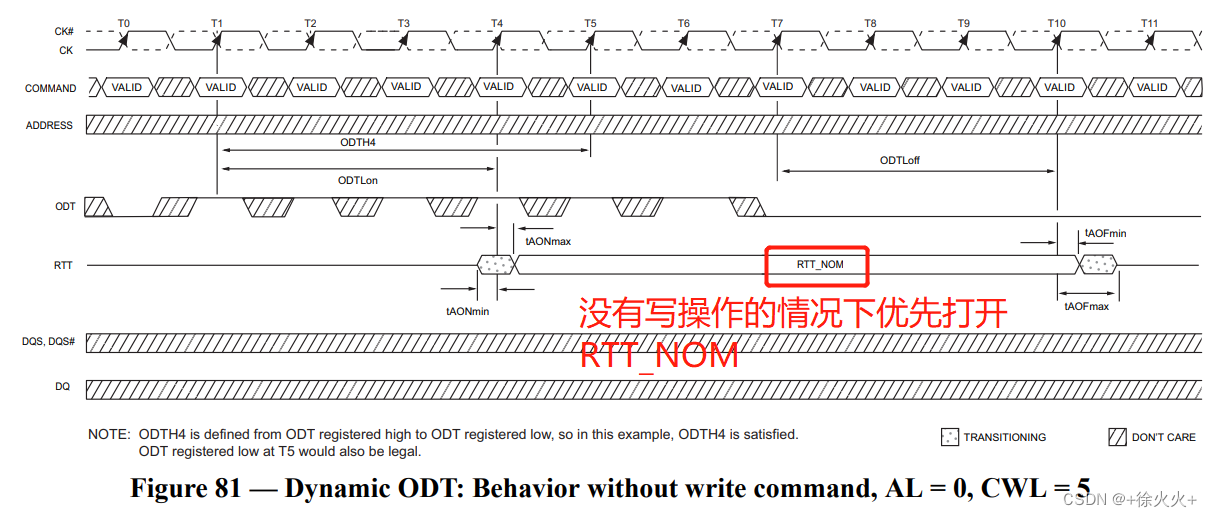

(2)动态ODT(也是同步ODT,属于同步ODT的一种):

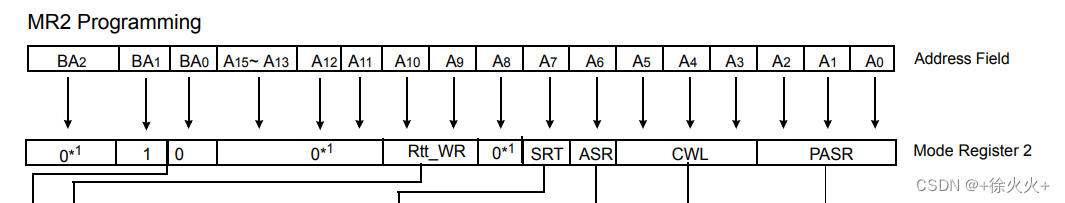

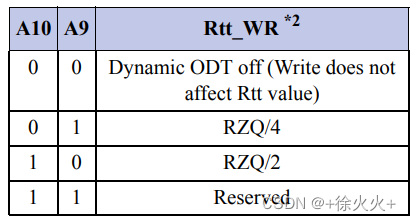

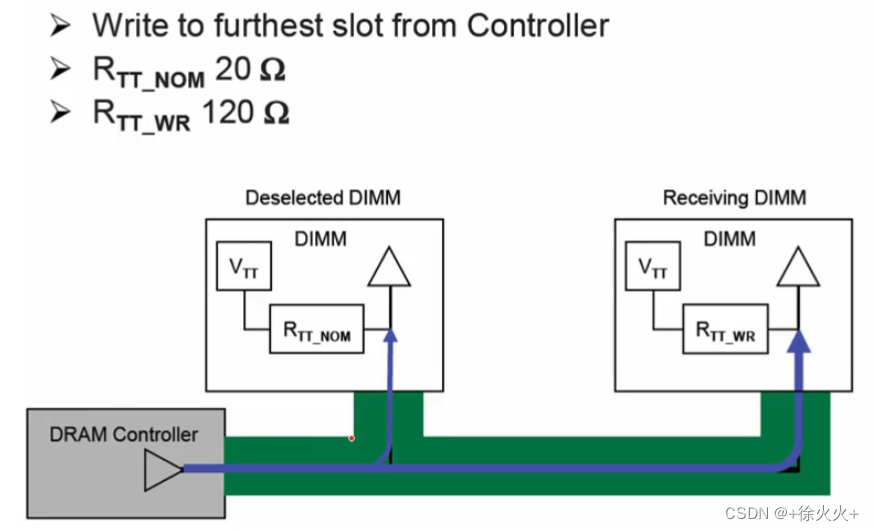

这个功能可以实现动态的去切换ODT,他是在memory颗粒中存在两套RTT组织,分别是RTT_nom和RTT_WR。一般RTT_nom可供选择的选项会多一些,在操作的过程中也可以将这两个RTT都去使能(这就存在一个哪个ODT优先级高的问题) 。Dynamic ODT主要是针对的是RTT_WR,在ODT打开,同时出现写操作的情况下,会打开RTT_WR;而只有ODT打开,灭有写操作的时候,首先打开的是RTT_nom。

打开方式:

这个图没懂什么意思??

注意,上面这张图实际上在第一个打开ODT操作的ODTH4时间周期内们只要发起了写,时序都是类似的。

注意,这里需要至少等待ODTH8的时间之后,才可以将ODT信号拉低。

类似与上面的时序,不同的地方在于T5时刻,上面的ODT是拉高的,而这里是拉低的,所以就导致经过ODToff时间之后,在T8时刻RTT组织关闭。

类似与上面的时序,不同的地方在于T5时刻,上面的ODT是拉高的,而这里是拉低的,所以就导致经过ODToff时间之后,在T8时刻RTT组织关闭。

上面各个时序图中的时序参数总结如下:

(3)异步ODT:

异步ODT应用在DRAM运行在DLL开启的模式下,但是在某种场景下DLL需要临时关闭(比如慢速的precharge power down,就需要将DLL关闭),此时ODT没有时钟参考了,那么此时打开ODT就和时钟没有关系了,也就是异步ODT。

2.DDR中的差分信号

本文介绍了DDR3内存中的ODT(On-DieTermination)技术,包括其作用、ODT电阻的选择、同步和异步操作、以及在写读操作中的时序管理。特别关注了RTT电阻的打开和关闭,以及动态ODT如何处理写操作优先级问题。

本文介绍了DDR3内存中的ODT(On-DieTermination)技术,包括其作用、ODT电阻的选择、同步和异步操作、以及在写读操作中的时序管理。特别关注了RTT电阻的打开和关闭,以及动态ODT如何处理写操作优先级问题。

1314

1314

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?