1.Fmt和Type有哪些组合?

---------------------------------------------------------------------------------------------------------------------------------

2.TC

参考virtual channel机制

---------------------------------------------------------------------------------------------------------------------------------

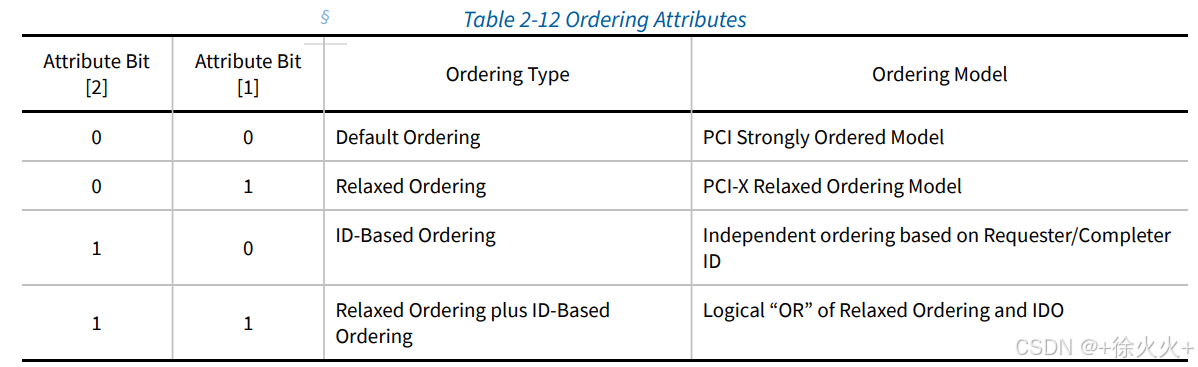

3.Attr

参考ordering机制和snoop相关内容

bit0:0表示当前TLP所传送的数据再通过FSB的时候需要和cache保持一致,由FSB通过总线监听自动完成而不需要软件干预;1表示FSB并不会将TLP中的数据与cache进行一致,这种情况下进行数据传输的时候需要软件保证cache一致性。在一些明确知道不会cache命中的操作,可以将该位置为1以减少FSB在进行总线监听带来的带宽损失。(当置为 1 时,Requester 的意思是这个 TLP 不会存在 host cache 一致性的问题(host cache coherency issues),因此系统硬件可以通过跳过普通处理器对这个请求的 cache 窥探,以此来节省时间。而当这一位被置为 0 时,需要进行 PCI-type 的 cache 窥探保护)

---------------------------------------------------------------------------------------------------------------------------------

4.TH

待补充

---------------------------------------------------------------------------------------------------------------------------------

5.TD

表示TLP中是否含有ECEC,PCIE中的校验机制有哪些?

(1)ECRC/LCRC (为什么需要ECRC?)

(3)PCRC(Plaintext CRC,纯文本 CRC):是 IDE TLP 中的概念,在大多数方面,PCRC的计算方法与ECRC相同,并且CRC多项式是相同的。IDE TLP上不允许使用ECRC,因此任何TLP都不能同时拥有PCRC和ECRC。

(4)FEC(Forward error correction,向前纠错):基于字典将要传输的内容重新编码,接收者再根据接收内容、字典、hamming distace接收这部分内容。

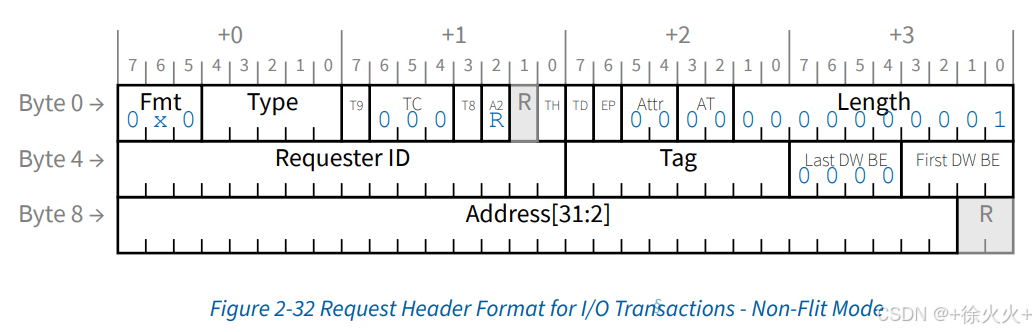

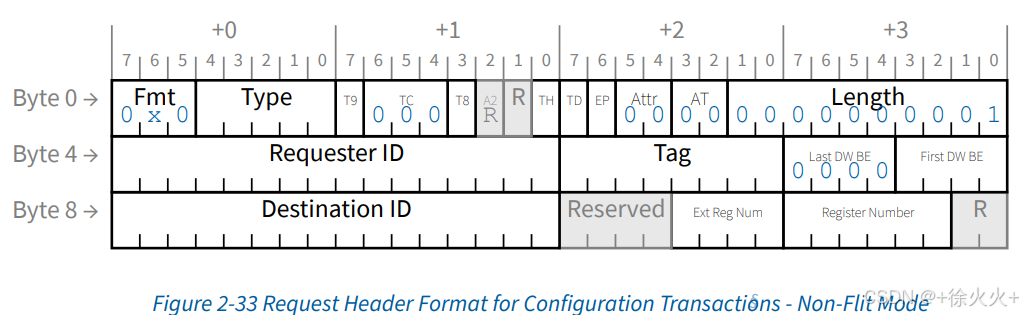

| LCRC(link CRC) | ECRC(End-toEnd CRC) | |

| 长度 | 32bit-TLP/16bit-DLLP | |

| 源/目的 | 用于检测两个连接的设备之间的链路上的错误,这些错误一般是由于物理层的信号质量问题引起的 | 用于检测Requester和completer之间的路径是否有损坏,ECRC是requester/initiaor的TL层生成的。 |

| 通过switch | 在入口被DLL层校验LCRC,在出口重新计算生产 | Switch不会修改内容 |

| Switch收到错误报文时 | 要求对端重发 | 记录错误,继续转发 |

| completer收到错误报文后 | 发送NAK报文给发送端,要求对端重发,重传过程不需要软件参与 | 发出一个不可修正的错误信息通知系统处理,没有重传机制,系统处理需要软件参与 |

| 是否可修正 | 可修正 | 不可修正 |

ECRC

多项式系数:04C11DB7(h)

Seed value(初始值):FFFFFFFF(h)

所有header field、End-End TLP Prefixes/OHC (如果有的话) 、data payload(如果有的话)都需要包含在ECRC计算中;

所有变化的域,在ECRC计算过程中都需要被认定为1:

(1)TLP header中type field中的bit 0;

(2)EP位

关于ECRC使用过程中的一些准则:

(1)一些基本准则;(2)针对switch的一些准则;

在NFM中,32位的ECRC值被放置在TLP的末尾的TLP Digest field字段中。在FM中,32位的ECRC值被放置在TLP Trailer中。

支持end-to-end data integrity检查的receiver收到包含ECRC的TLP该如何检查?

注意,计算出来的ECRC和32位TLP ECRC字段中对应的位置并不直接对应,存在一个对应关系:

---------------------------------------------------------------------------------------------------------------------------------

6.EP

data posioned,参考链接

---------------------------------------------------------------------------------------------------------------------------------

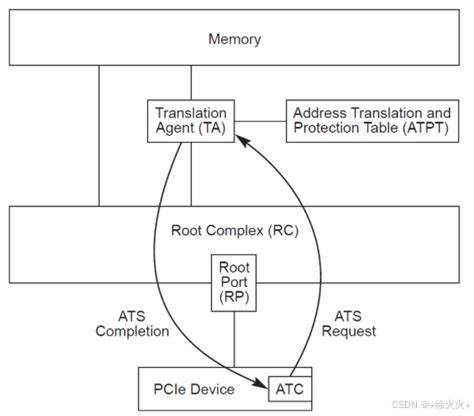

7.AT域是用来做什么的?

AT域是存储器读请求、AtomicOp及ATS地址转换请求的专属域,在其他事务中该域为Reserved预留。

AT=00,Untranslated:表示Translation Agent (TA) 可以将地址视为虚拟地址或物理地址;

AT=01,Translation Request:TA将返回转化的地址(包含request的Address字段)作为read completion, 此值仅对显式Translation Request有意义。 如果 TA 在Memory Read以外的Memory Request中收到 AT为 01b 的 TLP,则 TA 将发出Unsupported Request (UR) 信号;

AT=10,Translated:事务中的地址已由 ATC 转换。 如果允许与 SourceID 关联的Function向系统内存提供物理地址,则 TA 可能不会转换该地址。 如果Function不允许展现物理地址,则 TA 可以将其视为 UR;

AT=11,Reserved:如果 TA 收到一个Memory Request TLP,其中 AT 字段设置为 11b,则 TA 将发出Unsupported Request (UR) 信号。

---------------------------------------------------------------------------------------------------------------------------------

8.zero length表示什么?

关于zero-length:

Length长度为1,实现读刷新,为了确保之前使用posted方式所传输的数据最终达到目的地,与zero-length读对应的读完成报文中是不含有负载的,从而提高PCIE链路利用效率。另外,标准的存储器读同样可以完成刷新操作,但是这种读请求完成报文需要数据负载,链路利用效率可能不如zero-length。

应用:解决MSI报文使用的TC与数据传递使用的TC不一致导致的数据完整性问题(MSI报文的序问题)。

进行数据传递的TLP使用TC0,而MSI报文使用TC1,这两种TC使用的VC可能并不相同,不同的VC间的数据传递的时候并没有序的要求,虽然发送的时候是把传送数据的存储器写的TLP发送完以后在发送MSI报文,但是RC可能任然是优先收到MSI报文,此时如果立刻在中断处理服务程序中使用该PCIE设备写入的数据可能就会出现数据完整性的问题。

解决:PCIE完成DMA写操作的时候,再向目标地址发送一个zero-length存储器读的请求报文,当PCIE设备收到与这个存储器读请求对应的完成报文以后在发送MSI报文。因为存储器读请求TLP不能超越存储器写报文。

---------------------------------------------------------------------------------------------------------------------------------

9.PCIE中的BDF是什么?为什么cfg中还有个bus num?PCIE中的hirechary ID是什么?completer ID是什么?AIR机制是什么?

---------------------------------------------------------------------------------------------------------------------------------

10.PCIE中的tag机制是什么?

---------------------------------------------------------------------------------------------------------------------------------

11.byte enable机制是什么样的?

---------------------------------------------------------------------------------------------------------------------------------

12. 哪些操作是通过地址进行路由的,那些操作是通过ID进行路由的?

---------------------------------------------------------------------------------------------------------------------------------

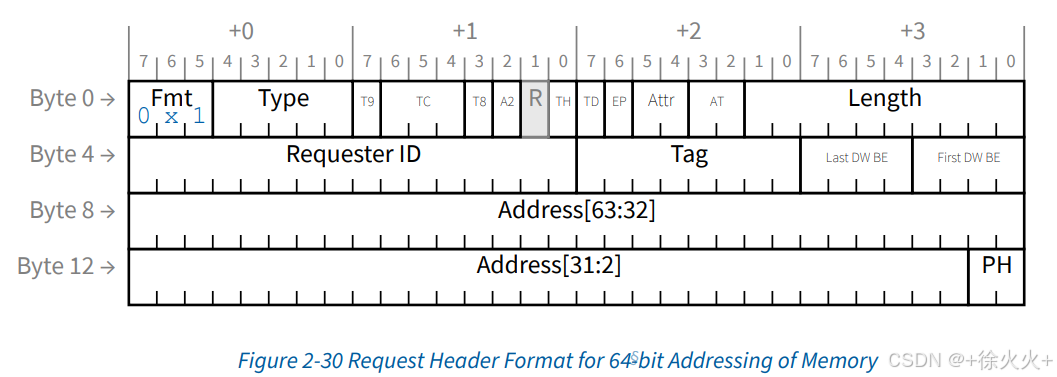

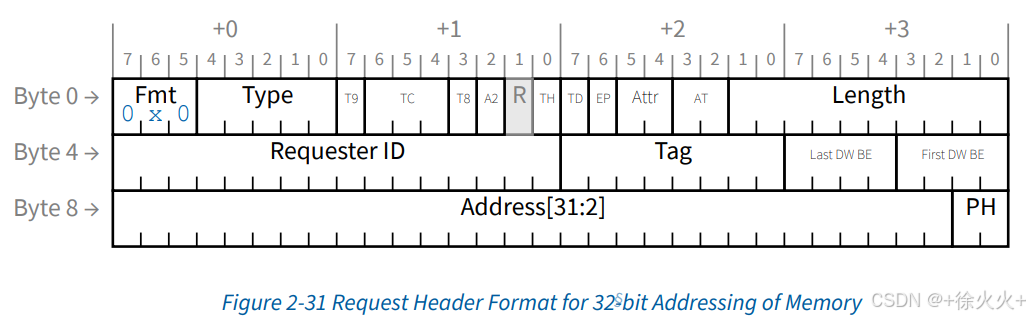

13.PH是什么?

待补充

---------------------------------------------------------------------------------------------------------------------------------

14.cpl中的status有哪些?UR,CA等待源头有哪些?

---------------------------------------------------------------------------------------------------------------------------------

15.BCM及byte count是什么?

---------------------------------------------------------------------------------------------------------------------------------

16.lower address是什么?

---------------------------------------------------------------------------------------------------------------------------------

17.各种包的格式是什么样的?

---------------------------------------------------------------------------------------------------------------------------------

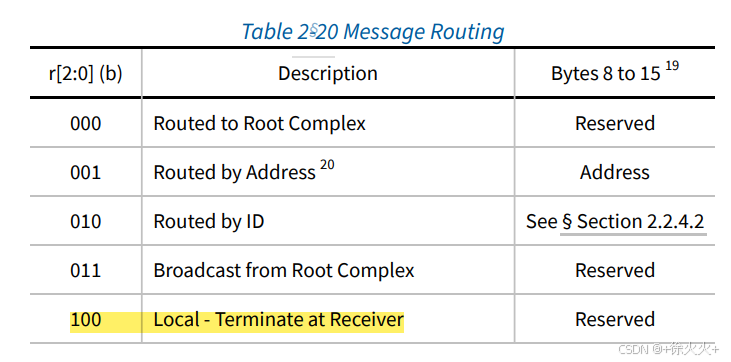

18 message中的route字段表示什么意思,和type字段有什么关系?

fmt+type[4:3]决定了这个TLP是message类型,fmt=001+type[4:3]=10 -> msg;fmt=011+type[4:3]=10-> msgd;

而type的剩余字段表示route,代表隐式路由,具体方式如下:

3747

3747

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?