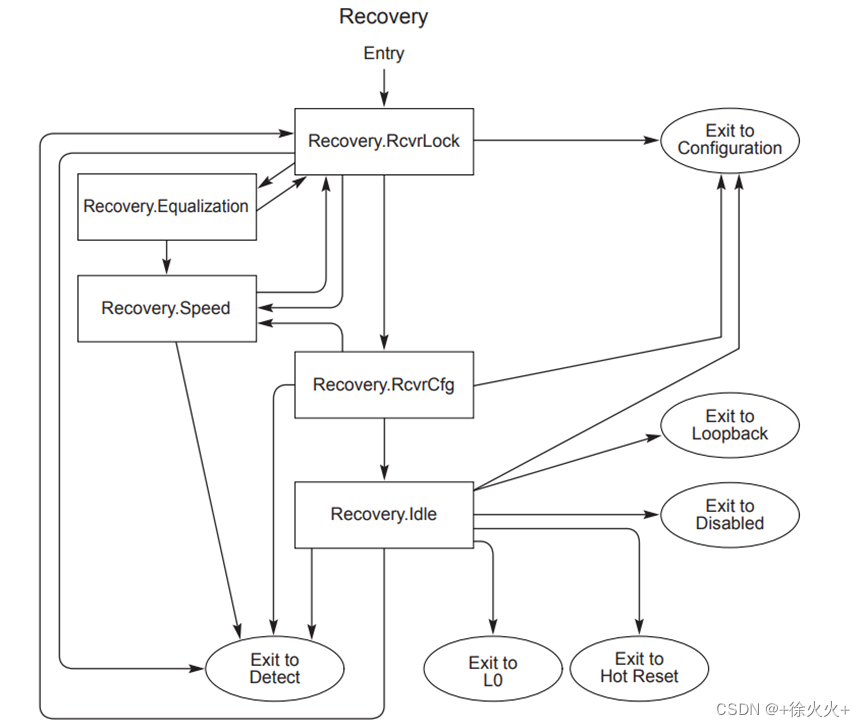

Recovery

**************************************************************************************************************

Recovery.RcvrLock

**************************************************************************************************************

Recovery.RcvrLock

(1)如果link是在8.0GT/s或以上的速率工作,那么rx只会认为当前lane获得Block alignment之后收到的TS0,TS1,TS2是有效的。如果进入当前状态是从L1或recovery.speed或L0s,获取Block alignment的过程必须在发生退出Electrical Idle的条件之后;如果当前状态是从L0状态进入的,那么Block alignment的过程必须在获取last data stream的end之后。

(2)如果link是在8.0GT/s或以上的速率工作,且start_equalization_w_preset为1:

针对使用preset value的情况:

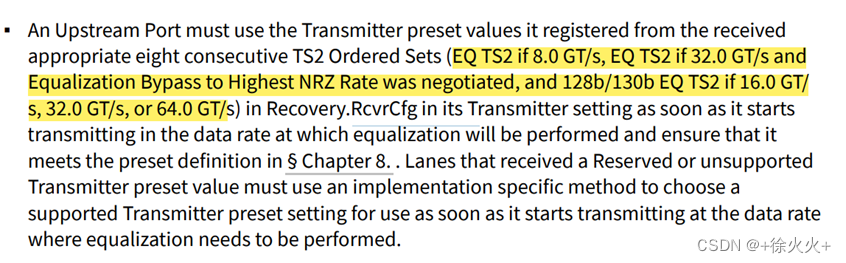

a:一旦开始了数据传输,并且要求执行equalization,Usp必须在tx使用rx收到的连续8个TS2中的preset value(黄色字体???)。lane上如果收到了不持的或者是reserve的preset value,那么可以根据实现具体使用一种方式来处理tx端发送的preset value。

b:如果需要执行equalization,dsp根据如下准则在tx端执行preset value:

如果当前数据传输速率是16.0GT/s或32.0GT/s,那么会在最近从Recovery.Rcvrcfg状态转变到当前状态过程中收到的八个连续的EQ TS2(针对equalization bypass to 32.0 GT/s is to be performed)或者128b/130b EQ TS2中收到的支持的tx preset value。否则的话,如果tx preset value在Lane Equalization Control Register Entry中的Downstream Port Transmitter Preset field中有定义,可以使用其中的值。

针对8.0GT/s -> tx preset value定义在每一个lane中的Lane Equalization Control Register Entry。如果当前寄存器中的值不是reserved的话,那么8.0GT/s下的dsp receiver可以使用lane Equalization Control Register Entry中的preset hint field。

针对16.0GT/s、32.0GT/s、64.0GT/s,dsp在16.0GT/s、32.0GT/s、64.0GT/s速率下的tx preset value分别在16.0GT/s、32.0GT/s、64.0GT/s Equalization Control Register Entry中。

注意不采用a、b两种方式的话,需要根据具体的实现决定一种决定tx preset value的方式,下个状态是Recovery.Equalization。

针对使用pre-cursor,cursor,post-cursor来说:

a:如果当前状态是从recovery.equalization状态进入的,在发送的TS1中,dsp必须要设置pre-cursor,cursor,post-cursor域,注意如果在recovery.equalization状态下收到的最后一个请求是含有preset的request,那么tx必须在将Transmitter Preset bits设为收到的request中的preset值。

b:建议的做法是在发送的TS1中把pre-cursor,cursor,post-cursor均设置为当前的cursor设置,将Transmitter Preset bits设置为最近的tx preset设置。

c:Recovery.RcvrLock 状态满足下述条件后,转移至 Recovery.RcvrCfg 状态。如果双方接收到 8 个连续的 TS1 或者 TS2 序列,其中链路与通道编号与发送的数值一致,并且序列中的 speed_change 比特为0;收到8个连续的TS0,并且是从Recovery.speed状态下进入当前状态;收到了8个连续的TS1,其中EC位为0;

d:如果dsp的当前状态不是从configuration.idle状态或者recovery.idle状态下进入,并且link control3寄存器中的perform equalization位设为1,那么下个状态时Recovery.Equaliztion状态;

e:如果当前速率是8.0GT/s,16.0GT/s,32.0GT/s,那么当前port必须确保在recovery.rcvlock状态下在在发送TS1(这个TS1是进入recovery.equalization状态需要的TS1)前不能发送超过两个EC为0的TS1;

f:如果当前速率是64.0GT/s,那么当前port必须确保在recovery.rcvlock状态下在在发送TS0(这个TS0是进入recovery.equalization状态需要的TS0)前不能发送超过两个EC为0的TS0;

(3)在离开configuration状态后,tx在所有的配置lane上发送link num和lane num均相同的TS1。如果directed_speed_change设为1,那么speed_change 位(bit 7 of the Data Rate Identifier Symbol in TS1 Ordered Set)必须设为1。如果接收到8个连续的 speed_change 比特为 1 的 TS1 序列后,也会同样将其内部变量 directed_speed_change 设置为 1。Non-flit mode下,TS1中的N_FTS值反应了当前操作下的速率。设备在进入当前状态时允许改变其advertise的data rate。

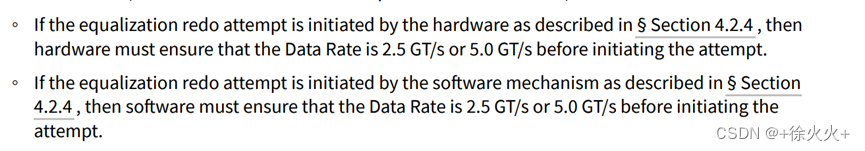

Dsp如果是从2.5GT/s或5.0GT/s转化到8.0GT/s或者32.0GT/s并且Equalization Bypass to Highest NRZ Rate是支持的,那么dsp准备重做equalization过程。整个过程如下:a:发送EQ TS1,其中speed_change为1,并且根据转变的目标速率在Data Rate Identifier上设定相应的值;b:如果硬件发起的equalization的重做过程,那么硬件必须确定2.5GT/s或5.0GT/s的data rate;c:如果软件发起的equalization的重做过程,那么软件必须确定2.5GT/s或5.0GT/s的data rate??;

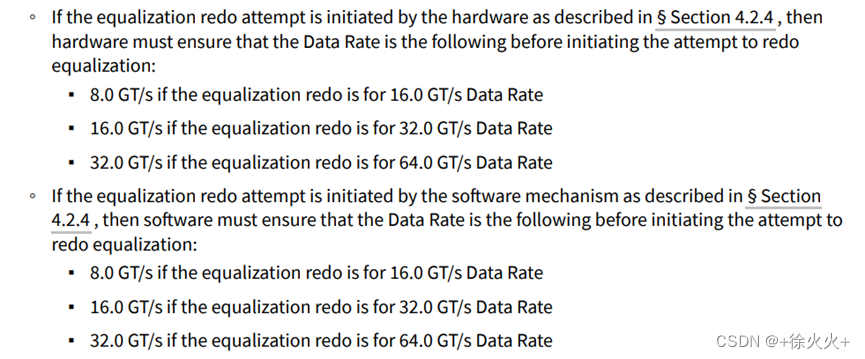

(4)如果dsp是从8.0GT/s到16.0GT/s,或者16.0GT/s到32.0GT/s或者32.0GT/s到64.0GT/s的速率变化引起的重做equalization过程,那么需要执行如下步骤:a:发送TS1,Equalization Redo为1,speed_change为1,并且根据转变的目标速率在Data Rate Identifier上设定相应的值;b:如果硬件发起的equalization的重做过程,那么硬件必须确定16GT/s或32GT/s或64GT/s的data rate;c:如果软件发起的equalization的重做过程,那么软件必须确定16GT/s或32GT/s或64GT/s的data rate??;

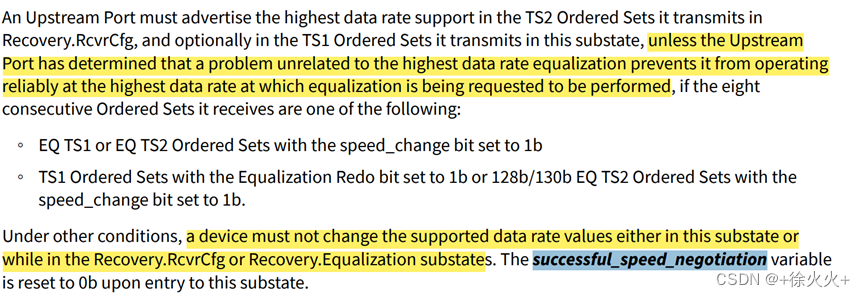

(5)Usp需要在recovery.rcvrcfg中发送的TS2中advertise最高的支持速率,而在TS1中是否advertise是一个可选项。除非usp确认在该速率下存在可靠性问题,并且无法靠均衡解决,如果一个usp:

a:连续接收到 8 个 speed_change 比特置为1的EQ TS1/EQ TS2,

b:或者收到的TS1/TS2的Equalization Redo bit为1或128b/130b EQ TS2 Ordered Sets中的speed_change为1.收到两个条件之一能改变支持的速率 在其他条件下,设备不能改变在此状态下(或者Recovery.RcvrCfg 或 Recovery.Equalization)支持的速率。进入此状态后successful_speed_negotiation清为0。

注意,以下几点:

a:DSP 如果想将速率切换到 8GT/s 并且重新进行均衡的话,需要发送 speed_change 比特置为 1,并且速率声明为 8GT/s 的 EQ TS1 序列。如果一个 USP 连续接收到 8 个 speed_change 比特置为 1,并且速率声明支持 8GT/s 的EQ TS1 或者 EQ TS2 序列后,USP 也会宣告支持使用 8GT/s 速率,除非 USP 确认在该速率下存在可靠性问题,并且无法靠均衡解决。值得注意的是,任意端口可以在进入 Recovery 状态时,改变其通告支持的速率,但需要确保自身可以稳定可靠地支持这一速率。除了上述这种情形外,端口在 Recovery.RcvrLock 状态,Recovery.RcvrCfg 状态以及 Recovery.Equalization 状态中,不得改变自己通告的支持速率。

b:在 Recovery.RcvrLock 状态中,USP可以指定DSP在 5GT/s 速率下使用的去加重等级系数(de-emphasis level)。USP 通过 TS1 序列中的Selectable De-emphasis bit (bit 6 of Symbol 4),来指定 DSP 的数值设置。但是 DSP 有可能会因为链路上的比特错误,无法接收到 USP 发送的这一信息,所以 USP 可以在因为速率切换进入 Recovery 状态后,可以再次指定 DSP 的去加重等级。如果 DSP 打算采用 USP 所要求的的数值,那么 DSP 必须在 Recovery.RcvrLock 状态中记录接收到的Selectable De-emphasis bit数值。

c:在进入 Recovery.RcvrLock 状态时,TS1 序列接收方也可以被指定新的发送电压数值。接收方会在进入该状态时采样一次链路控制寄存器2( Link Control 2 register)中的 Transmit Margin 比特,并且保持该数值有效,直到下一次从 L0, L0s, 或者 L1 进入到 Recovery 状态,采样到新的数值为止。

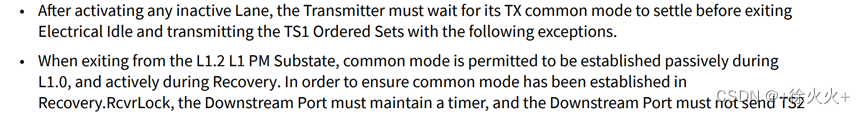

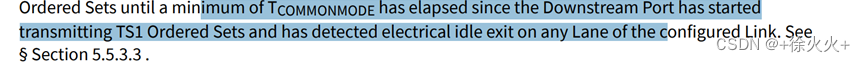

(6)在将inactive的lane进行activating之后,tx需要在exiting Electrical Idle和发送TS1之前等待其tx端的共模电压稳定(除了退出L1.2,L1的pm状态,此时PCIe链路可以在L1.0期间被动地尝试重新建立同步,并在recovery期间主动地尝试恢复同步。为了确保common mode在recovery.rcvrlock状态下已经建立,dsp需要做一个timer,dsp只有在自从在任意的配置lane上检测到electrical idle exit之后timer达到最小的TCOMMONMODE值之后才可以发送TS1)。

需要注意的是,在上述192ns之内、对端进入Recovery.Rcvrlock之后,在一个新的Transmit Margin field变为有效之前,bit lock和symbol/block alignment执行完之后电压水平可能会发生变化。在这情况下rx需要重新获取bit lock和symbol/block alignment。

注意:a:针对发起速率变化的那一侧,在L0或L1状态下directed_speed_change变量设为1。针对没有主动发起速率变化的那一侧,如果收到了TS中的speed change位设为1,那么directed_speed_change变量也设为1,如果进入recovery.speed状态下,directed_speed_change变量设为0;b:如果是收到第一个TS之前就进入到L0,设备需要接收所有正确的TLP和DLP。如果是在128/130b的模式下,收到的TLP/DLP遵循128b/130b解码规则。

(7)Recovery.RcvrLock 状态满足下述条件后,转移至 Recovery.RcvrCfg 状态:如果双方接收到 8 个连续的 TS1 或者 TS2 序列,其中链路与通道编号与发送的数值一致,并且序列中的 speed_change 比特与本地变量 directed_speed_change 一致,并且 EC 域数值为 00b (即无需进行均衡训练),并且当前速率是8.0GT/s或者更高的速率。

a:如果设置了 Extended Synch 比特,那么在进入 Recovery.RcvrCfg 状态之前,必须最少发送 1024 个连续的 TS1 序列。

b:如果原先是从 Recovery.Equalization 状态进入当前次状态,那么 USP 需要比较所有通道上接收的equalization coefficients或者 preset值,将他们和均衡的 Phase2 中所接收的最终系数集(final set of coefficient)或者 preset 进行比较。如果他们数值不一致,那么 USP 会将其发送的 TS2 序列中的 Request Equalization 比特设置为 1。

24ms 超时后,根据下列条件进行状态跳转:

(8)转移至 Recovery.RcvrCfg 状态

如果同时满足下述两个条件,那么接下来转为 Recovery.RcvrCfg 状态:

a:接收到 8 个连续的 TS1 或者 TS2 序列,其中链路与通道编号与发送的数值一致,并且序列中的 speed_change 比特为 1。

b:当前速率高于 2.5 GT/s,或者 TS1/TS2 中表示还支持至少一种更高的速率设置,也就是发送的TS1中的data rate identifiers或者接收的8个连续的TS1/TS2中支持高于2.5GT/s的速率。

(9)转移至 Recovery.Speed 状态

如果满足下述两个条件中的一个,那么接下来转为 Recovery.Speed 状态:

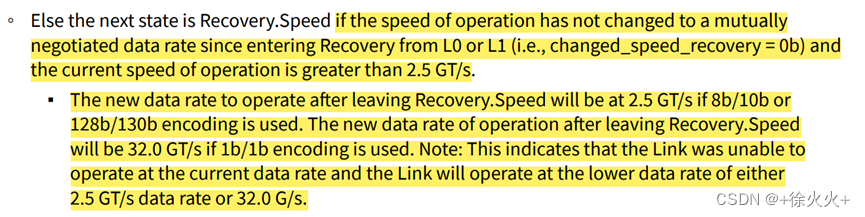

a:如果当前速率设置高于 2.5 GT/s,但是自从进入 Recovery 状态后,从来没能在该速率下正常工作过,(变量 changed_speed_recovery 被清除为 0 揭示了这种现象)。此时,待离开 Recovery.Speed 状态后,速率会重新降低为 2.5 GT/s(针对8b/10b或128b/130b是2.5 GT/s,针对1b/1b是32 GT/s)。

b:如果变量 changed_speed_recovery 被设置为 1,表示某个高于 2.5 GT/s 的速率已经能够正常工作,但是在切换到新的协商速率后,链路不能工作,这种情况下速率会被恢复为由 L0 或者 L1 进入 Recovery 状态前的数值。

(10)转移至 Configuration 状态(下列条件满足的情况下directed_speed_change设为0)

a:如果没有发起速率改变请求,(即自从进入Recovery 状态之后directed_speed_change 变量为 0,并且 TS1/2 中的 speed_change 比特也为 0),并且任何配置的lane上收到了至少一个TS1或TS2,并且受到的TS1/TS2的link num和lane num和tx在这些所对应的lane上发送的一致。

b:双方协商后发现彼此同时支持的最高速率只是 2.5 GT/s(根据受到的TS1或TS2),并且directed_speed_change变量为0,收到的TS1/TS2中的speed_change为0;

(11)转移至 Detect 状态

如果上述条件都没能满足,那么接下来转移至 Detect 状态

(12)转移至 Recovery.Equalization 状态

对于运行在 8GT/s 速率的链路来说,他们并不是每次进入 Recovery 状态时,都需要经过 Recovery.Equalization 次状态。链路只会在满足下述情况时,才会进入 Recovery.Equalization 状态:

如果内部变量 start_equalization_w_preset 设置为 1,那么:

a:USP 需要在转为 8.0 GT/s 速率之前,采样其接收的连续 8 个 TS2 中的 preset 数值。USP 必须采用其中的发送端 preset,可以选择是否采用其中的接收端 preset。

b:DSP 进入 8.0 GT/s 速率后,必须采用其通道均衡控制寄存器( Lane Equalization Control register )中的发送端 preset,可以选择是否采用其中的接收端 preset。

否则(即该变量不为 1),发送端必须采用在上一次均衡过程中协商一致的参数(coefficient)设置。

a:如果 USP 接收到 8 个连续的 TS1 序列,其中链路与通道编号与发送的数值一致,并且序列中的 speed_change 比特为 0,但是 EC 域数值不为零时,下一个状态为 Recovery.Equalization。因为接收到上述 TS1 序列表示 DSP 希望重新进行均衡中的部分流程。协议中提到,DSP 可以在上层软件要求,或者其他具体实现决定的情况下,发起该请求。当然,DSP 必须保证进行该操作的时间,不能导致该传输超时,也就是说,DSP 需要保证发起该请求前,链路上没有正在进行中的传输。

b:在上层协议要求后,DSP 即进入 Recovery.Equalization 状态,但是不能由 Configuration.Idle 或者 Recovery.Idle 状态直接进入 Recovery.Equalization 状态。(译注:需要通过 Recovery.RcvrLock 次状态进入)协议规定在 DSP 通过发送 EC 不为 0 的 TS1 要求对端重新进行均衡过程之前,不能发送超过两个 EC=00b 的 TS1 序列。

**************************************************************************************************************

Recovery.equalization

**************************************************************************************************************

TODO:待补充

**************************************************************************************************************

Recovery.Rcvrcfg

**************************************************************************************************************

TODO:待补充

**************************************************************************************************************

Recovery.speed

**************************************************************************************************************

tx进入Electrical Idle,并且等待rx也进入Electrical Idle,并且需要等待额外的一定时间(successful_speed_negotiation = 1,成功的进行了速率协商的情况下,等待至少800ns;successful_speed_negotiation = 0,没有成功进行速率协商,等待至少6us,但是无论哪种都不应该等待超过1ms时间)

如果不在需要tx处于Electrical Idle状态(满足如下条件),下个状态是Recovery.RcvrLock,

(1)如果当前状态是从Recovery.RcvrCfg状态进入的,并且link的两侧均切速成功的话(successful_speed_negotiation = 1),新的速率是两侧config lane上协商的最高公共速率。changed_speed_recovery被设为1;

(2)没有速率成功切换的情况下,如果当前子状态是自从L0/L1进入recovery状态下第二次进入该状态(changed_speed_recovery = 1b),那么速率将会切到最初的从L0/L1进入recovery状态下的速率,changed_speed_recovery被设为0;

(3)否则其他情况下新的工作速率将是2.5GT/s,changed_speed_recovery被设为0;

48ms超时后,进入detect状态;

在Link bandwidth改变的情况下,如果successful_speed_negotiation是1,在recovery.rcvrcfg阶段收到的8个连续的TS2中的Autonomous Change bit(symbol4中的bit6)设为1,并且speed change是由于dsp发起的,并且这个过程不是由于链路质量可靠性导致的,那么link status寄存器中的Link Autonomous Bandwidth Status bit将设为1;

其他情况下,在Link bandwidth改变的情况下,link status寄存器中的Link Bandwidth Management Status设为1;

**************************************************************************************************************

Recovery.idle

**************************************************************************************************************

下个状态时config状态:

如果在任意config的lane上收到两个连续的TS1,其中lane num设为pad;

下个状态时L0:

对于8b/10b来说,8个连续的Symbol Times of Idle data在所有的config的lane上收到并且在收到一个Idle data Symbol已经发送了16个Symbol Times of Idle data;

对于128b/130b来说,8个连续的Symbol Times of Idle data在所有的config的lane上收到并且在收到一个Idle data Symbol已经发送了16个Symbol Times of Idle data,并且此状态不是从Recovery.RcvrCfg由于timeout进入当前状态;

使用8b/10b encoding时,tx发送Idle data Symbols在所有config的lane上;

使用128b/130b encoding时:

(1)如果当前速率时8.0GT/s时,tx在所有config的lane上发送SDS来开启data stream,随后在所有config的lane上发送idle data symbol;

(2)如果当前速率大于等于16GT/s,tx发送skp在SDS之后来开启数据流,随后发送idle data symbol;

(3)

其他情况下,2ms timeout后:

(1)如果idle_to_rlock_transitioned小于'hff,下个状态是Recovery.RcvrLock.

注意,如果速率是8.0GT/s或者更高的速率,idle_to_rlock_transitioned在每次进入Recovery.RcvrLock状态下增加1;如果速率是5.0GT/s,idle_to_rlock_transitioned在进入Recovery.RcvrLock状态下变为'hff;

(2)其他情况下进入detect状态;

1093

1093

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?