VIP使用场景

配置$DESIGNWARE_HOME后

dw_vip_setup -i home查看VIP和example;

dw_vip_setup -path pcie_dev -e pcie_svt/tb_pcie_svt_uvm_unified_vip_sys 生成PCIE VIP example;

example中提供了VIP适用的各类DUT验证场景:

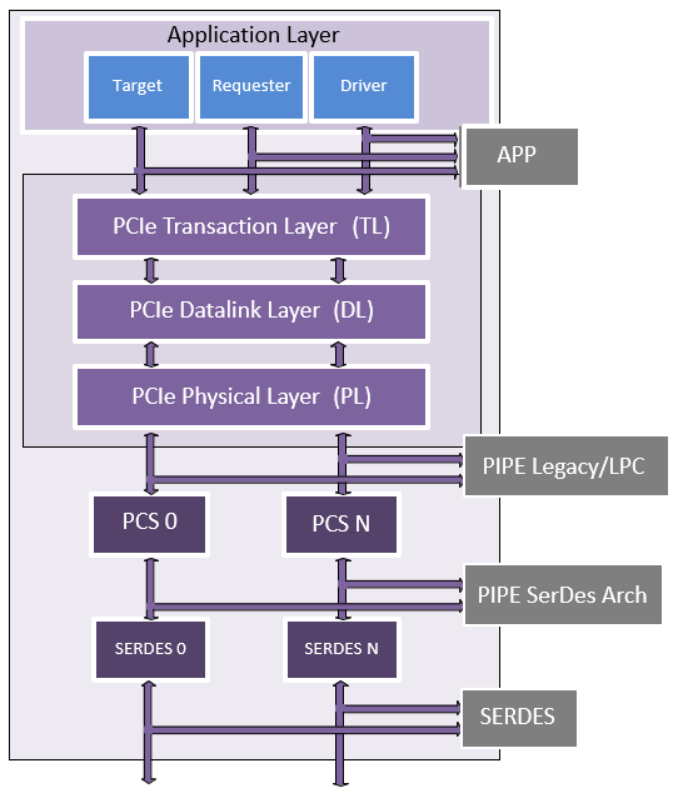

支持多种接口,MAC层的PIPE,PCS并行接口,PMA串行接口;

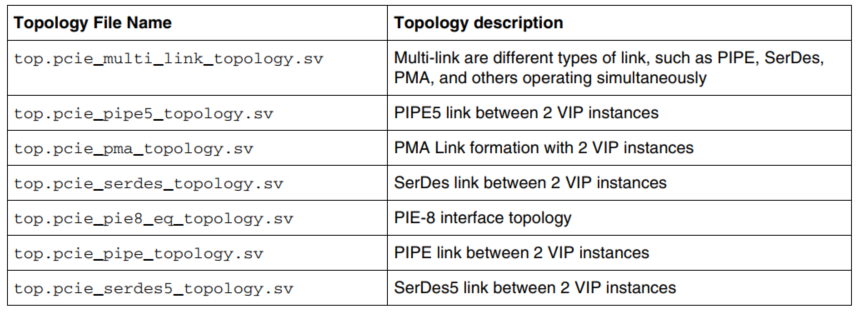

场景如下:

DUT(RC/EP) - - serdes link - - VIP (EP/RC)

VIP(RC) - - PIPE link - - DUT(PHY(PCS+PMA)) - - serdes link - - VIP(EP)

VIP(RC/EP) - - PIPE link - - DUT(RC/EP)

本系列参考ts.base_serdes_test.sv用例集成VIP,VIP模拟RC,DUT为EP类型,serdes接口连接。

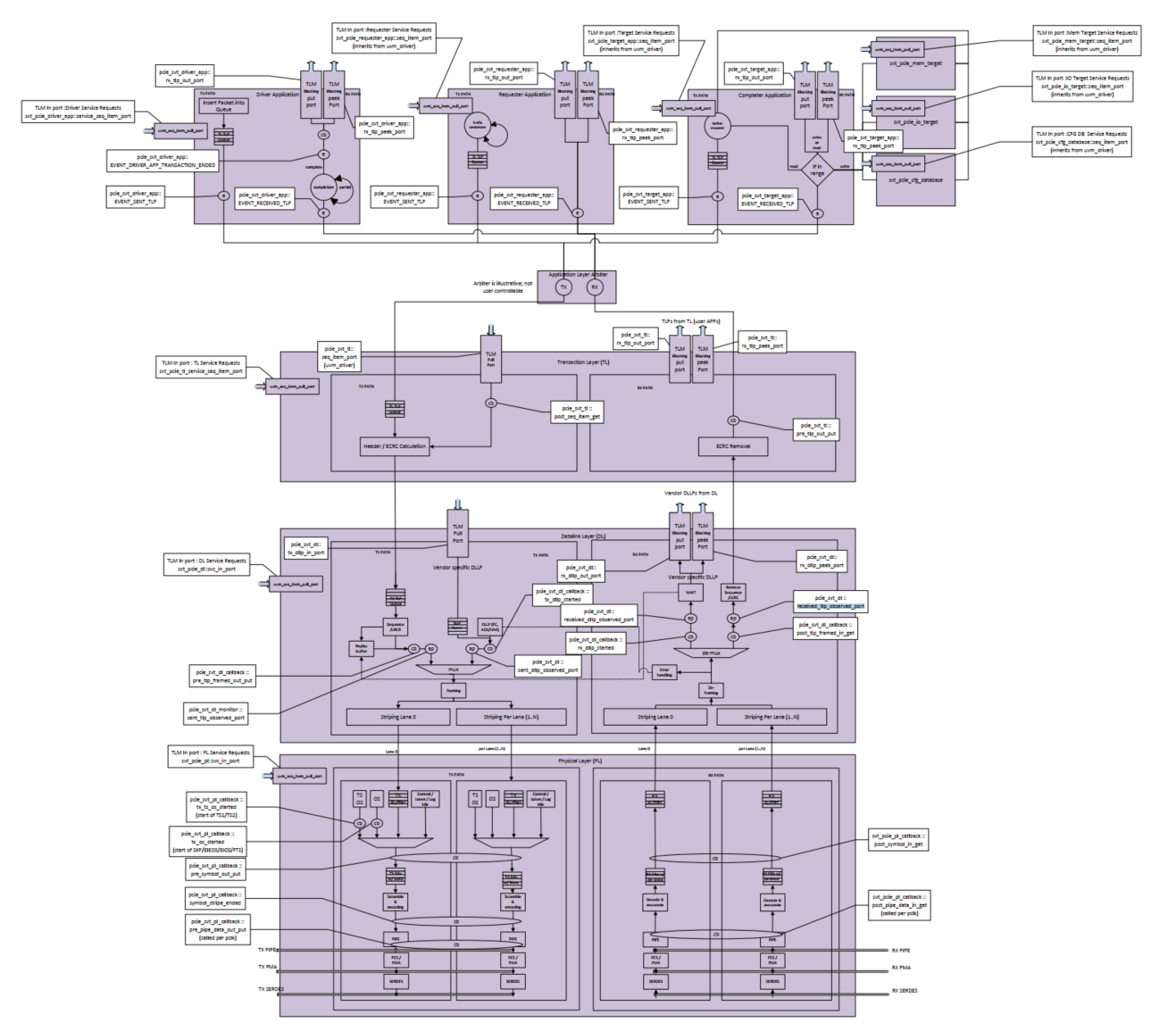

VIP分层结构

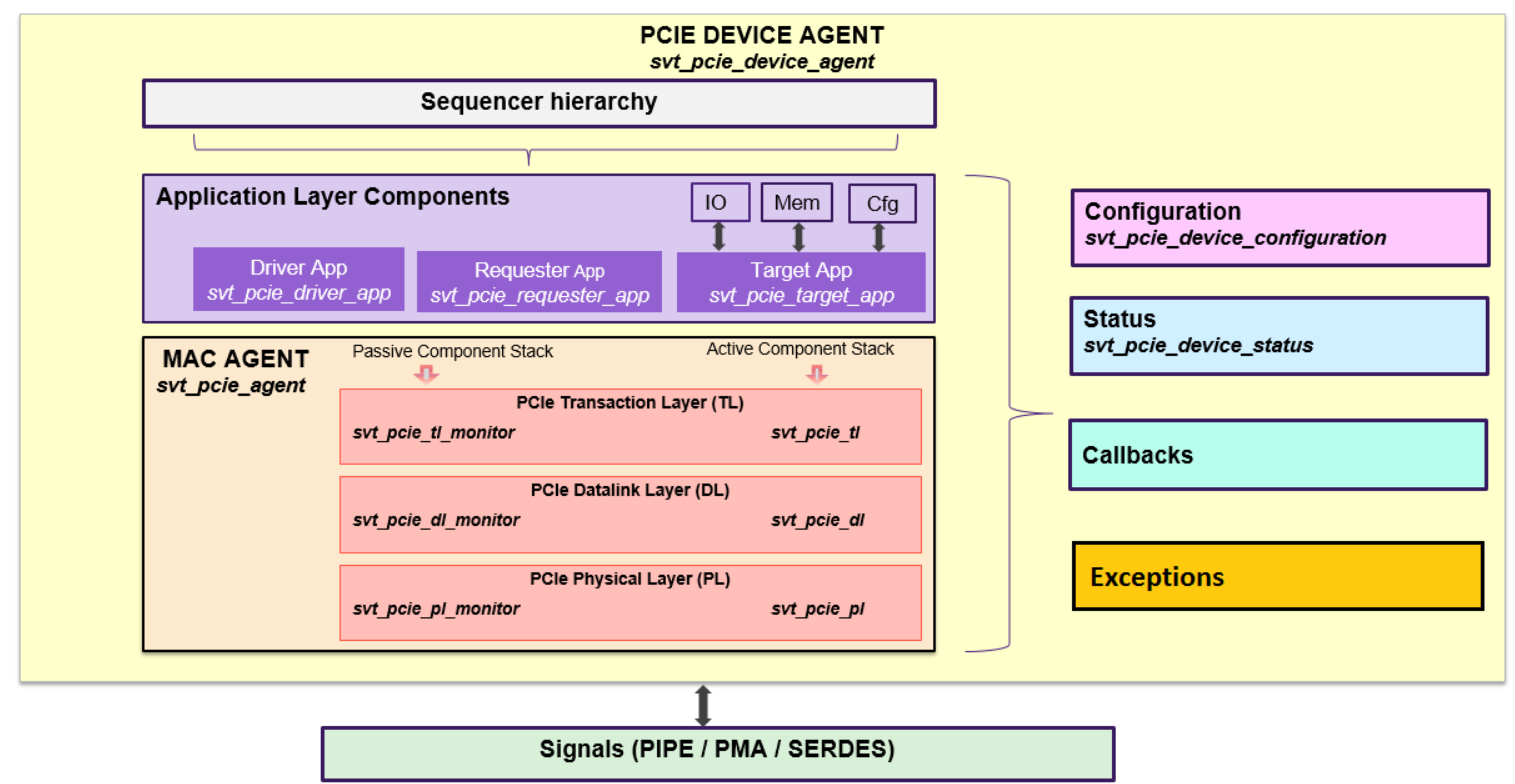

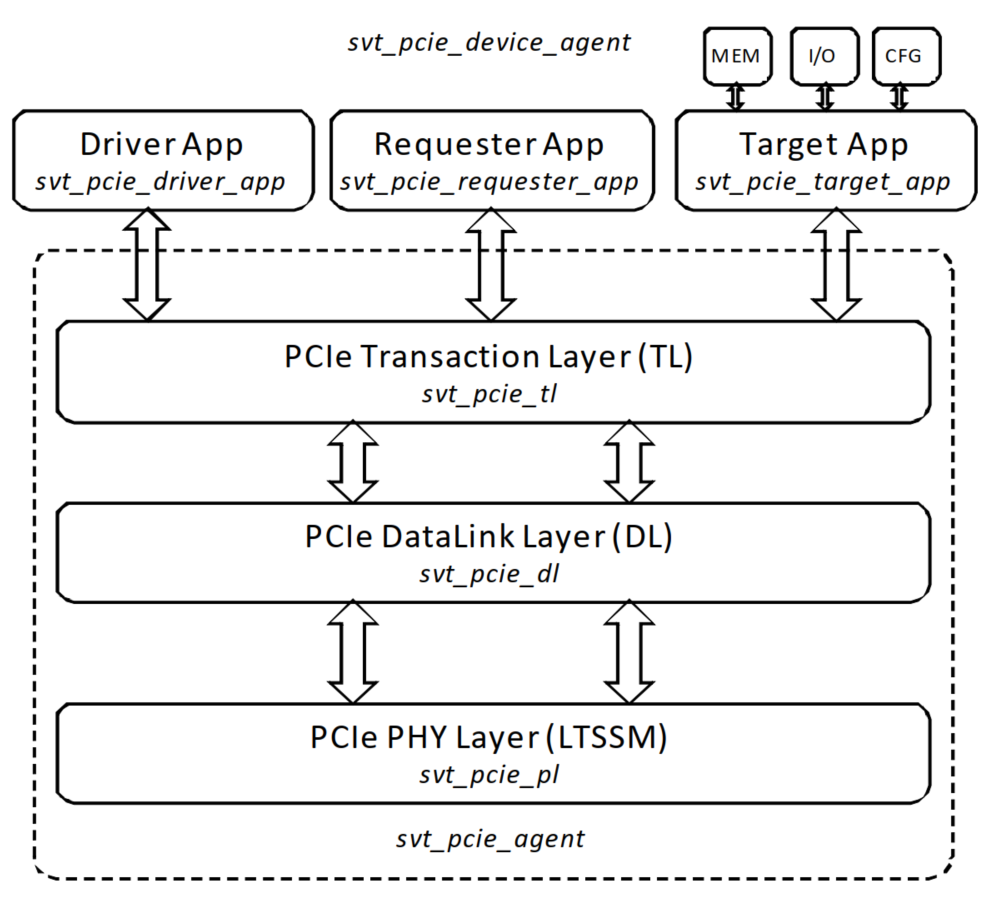

VIP结构,模拟PCIE协议实现,也是分层结构;每层都可以看成一个单独的Agent,具备对应的seq;采用layering sequence的方式,像其他分层协议如USB,USF等,也是相同的结构;可参考:🔗UVM layering sequence for layered protocol 🔗layering sequence in VC USB VIP

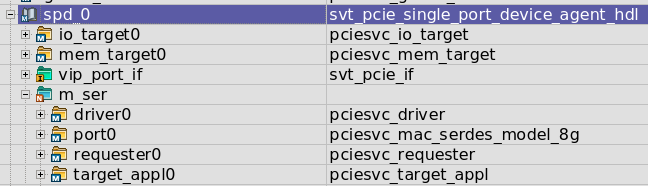

svt_pcie_device_agent中包含Application Layer和PCIe Agent

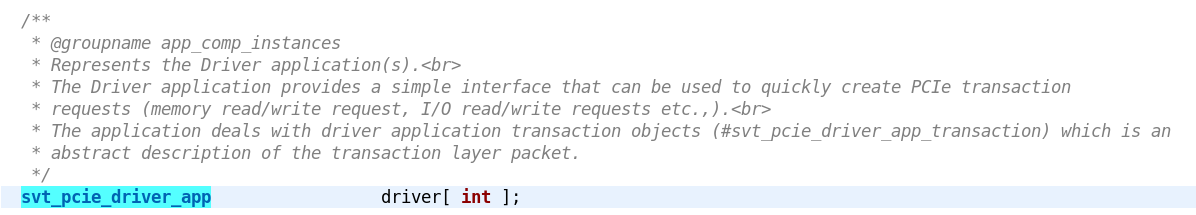

svt_pcie_driver_app 负责发送PCIe事物层请求包,如memory read/write request, I/O read/write requests etc.

svt_pcie_requester_app 和svt_pcie_driver_app类似,但requester_app只能发送memory访问的包,适合构造大量memory访问的场景。

svt_pcie_target_app 负责接收对端发送的事物包,并作出响应;根据不同类型的包(IO/Mem/Cfg),分别有

svt_pcie_cfg_database,svt_pcie_mem_target,svt_pcie_io_target来模拟mem model;可通过后门的方式访问对应mem_model.

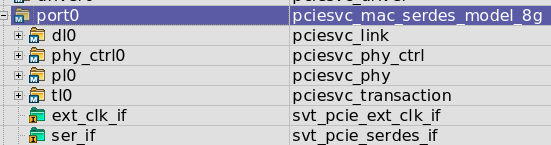

svt_pcie_agent 模拟PCIe协议栈;包含The Transaction Layer(svt_pcie_tl);The Data-link Layer (svt_pcie_dl);The Physical Layer (svt_pcie_pl);

上述的每一个组件,都有对应的status,config,sequencer,seq_item与之相对应;

详细的各类成员总结如下:

| name | members |

|---|---|

| svt_pcie_driver_app | svt_pcie_driver_app_service_sequencer svt_pcie_driver_app_transaction_sequencer svt_pcie_driver_app_configuration svt_pcie_driver_app_status |

| svt_pcie_requester_app | svt_pcie_requester_app_service_sequencer svt_pcie_requester_app_configuration svt_pcie_requester_app_status |

| svt_pcie_io_target | svt_pcie_io_target_service_sequencer svt_pcie_target_app_configuration svt_pcie_io_target_status |

| svt_pcie_mem_target | svt_pcie_mem_target_service_sequencer svt_pcie_target_app_configuration svt_pcie_mem_target_status |

| svt_pcie_cfg_database | svt_pcie_cfg_database_service_sequencer svt_pcie_target_app_configuration |

| svt_pcie_tl | svt_pcie_tl_service_sequencer svt_pcie_tlp_sequencer svt_pcie_tl_configuration svt_pcie_tl_status |

| svt_pcie_dl | svt_pcie_dl_service_sequencer svt_pcie_dllp_sequencer svt_pcie_dl_configuration svt_pcie_dl_status |

| svt_pcie_pl | svt_pcie_pl_service_sequencer svt_pcie_pl_configuration svt_pcie_pl_status |

sequencer分为transaction_sequencer和service_sequencer;

service_sequencer处理service transactions,控制driver的行为;如svt_pcie_driver_app_service_sequencer对应的service transaction:svt_pcie_driver_app_service

transaction_sequencer处理data transactions,生成PCIE总线事物;如svt_pcie_driver_app_transaction_sequencer对应的data transaction:svt_pcie_driver_app_transaction;查看源码内容是TLP报文的各类定义;

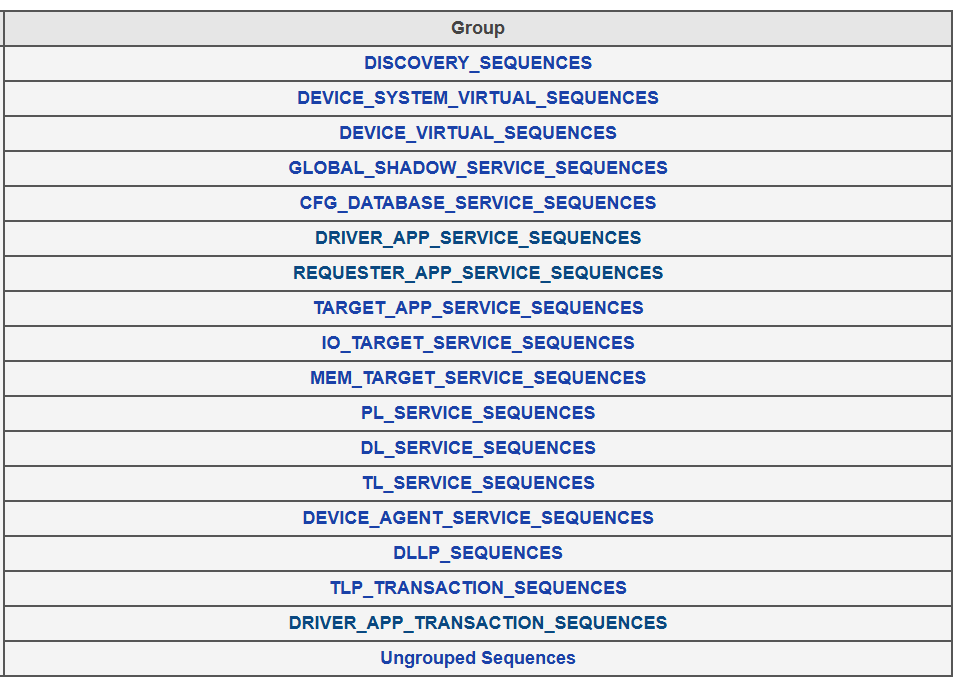

VIP提供的sequence都放在sequence_collection文件中,归类如下:

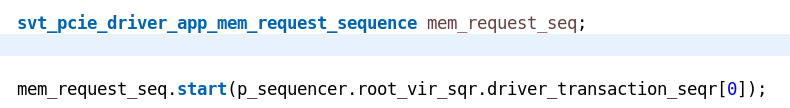

常用的如svt_pcie_driver_app_mem_request_sequence发送mem类型TLP,svt_pcie_driver_app_cfg_request_sequence发送Cfg类型TLP,都放svt_pcie_driver_app_transaction_sequence_collection.svp文件下。

callback and TLM port

VIP在各个节点都提供了callback函数供用户重写,方便注错,覆盖率收集等操作;相应的,也提供TLM port,可将一些中间transaction连接到scoreboard,做数据对比。

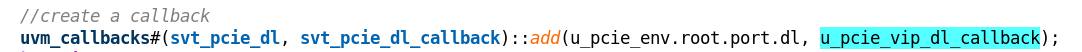

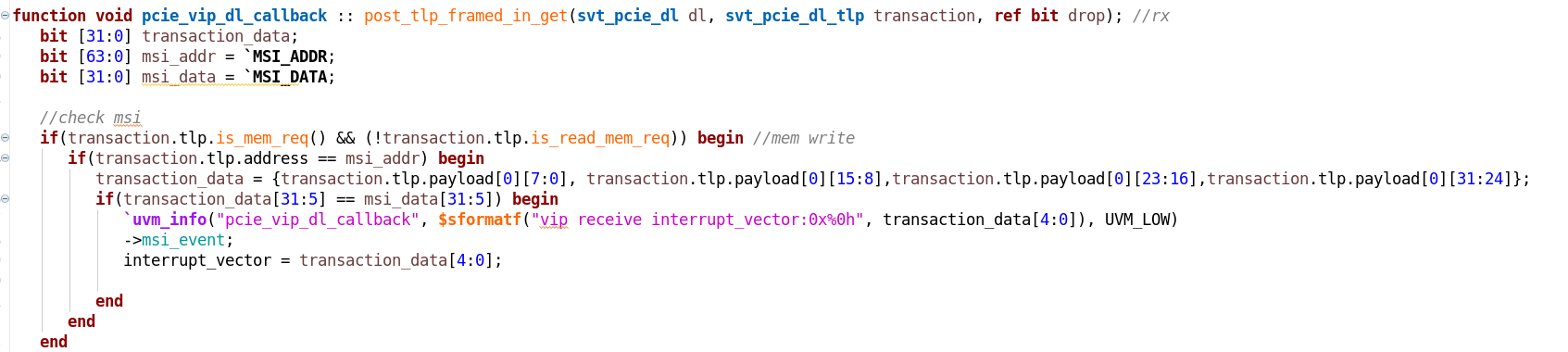

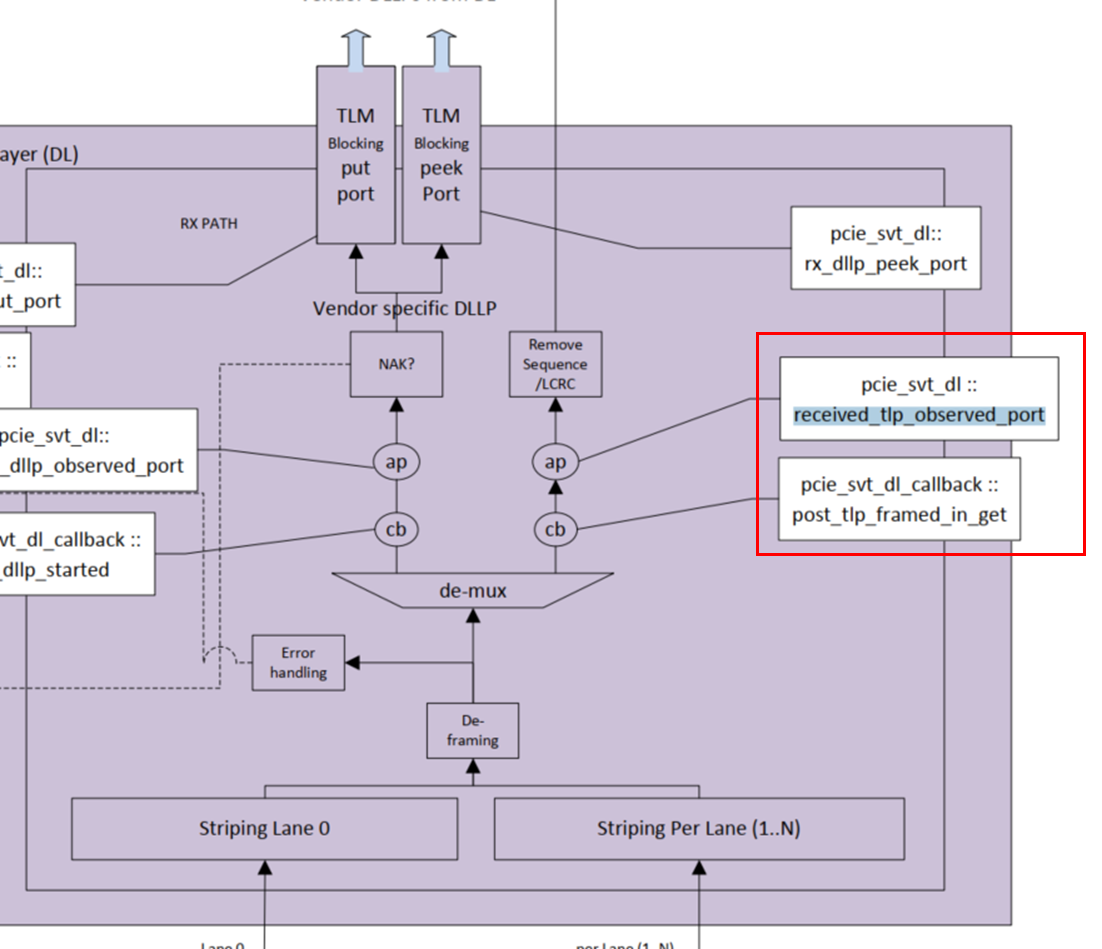

例如当EP发送MSI中断时,VIP作为RC会收到MEM_WR TLP,如何判断该MEM_WR TLP是否符合预期,可以重写callback funciton post_tlp_framed_in_get或者利用received_tlp_observed_port将dl_tlp类型的tr送往scoreboard做处理

完整的callback和TLM port图可参考pcie_layer.pdf

debug 方式

debug方式总结如下:

-

查看simulation log,

+UVM_VERBOSITY控制log显示内容; -

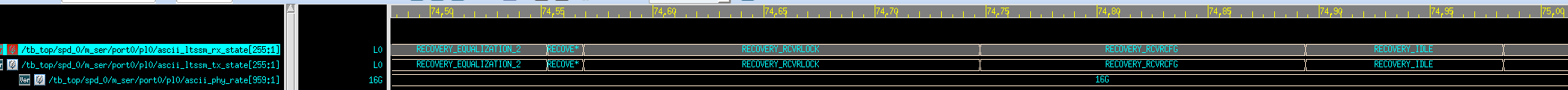

ASCII码形式的debug信号

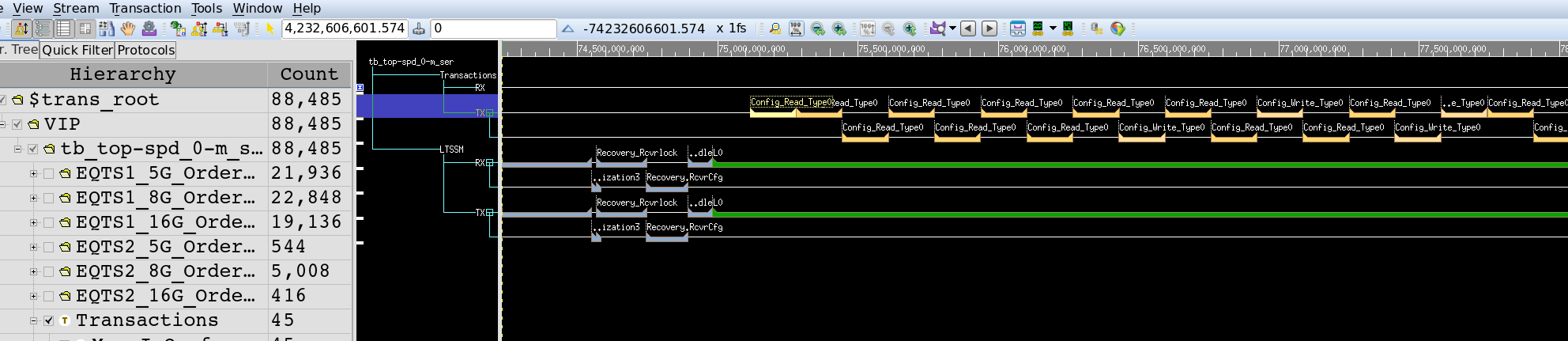

在/tb_top/spd_0/mser/port0/pl0(dl0/tl0)下有以ascii_*开头的信号,可以在波形中查看;如ltssm状态的跳转:

-

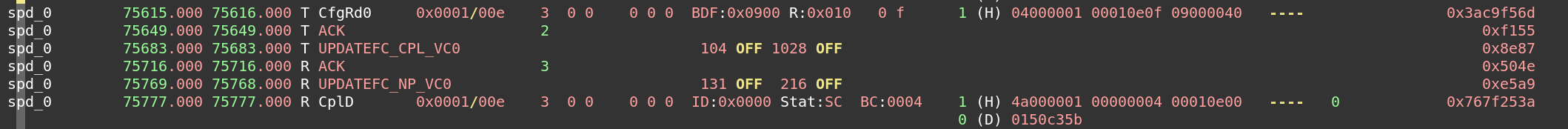

transaction.log显示TLP信息;symbold log显示symbol信息;

一个CfgRd0的TLP:

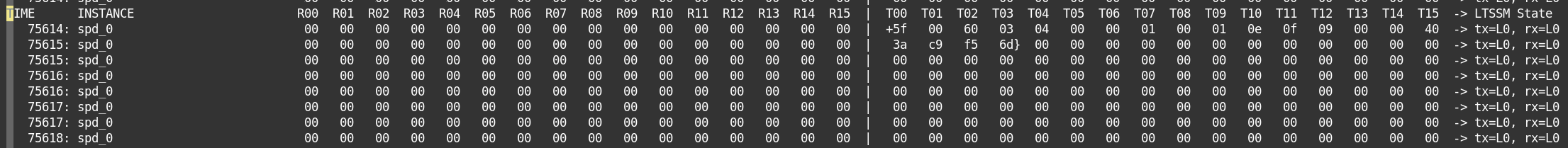

与之相对应的每条lane上的传输内容:

-

PA(Protocol Analyzer)显示PCIe传输包,可参考🔗Verdi Protocol Analyzer Debug 简单使用

激励流程

以发送Mem_Wr TLP为例,VIP内部实现:(VIP也是按照PCIE协议分层实现的,可参考:🔗layering sequence)

-

svt_pcie_driver_app_mem_request_sequence在driver_transaction_seqr[0]上启动

-

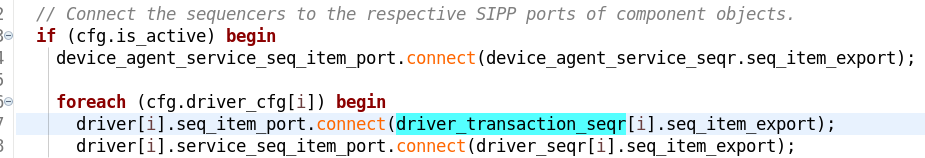

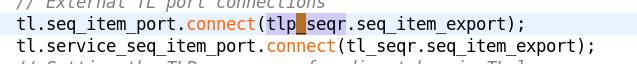

svt_pcie_device_agent中driver_transaction_seqr与svt_pcie_driver_appTLM连接;tr传输到svt_pcie_driver_app;

-

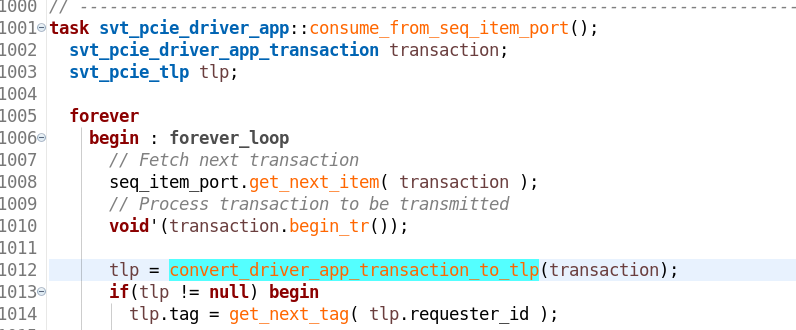

driver中

convert_driver_app_transaction_to_tlp将svt_pcie_driver_app_transaction类型的tr转换成svt_pcie_tlp类型的tr

-

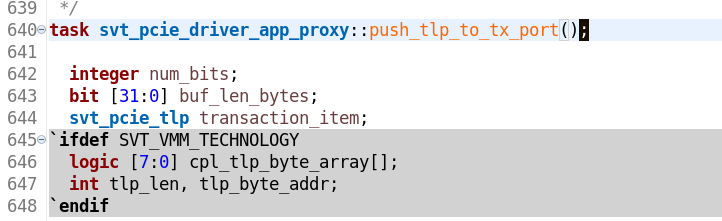

svt_pcie_dirver_app中的run_phase会调用push_tlp_to_tx_port,将tr送到tx发送端;

push_tlp_to_tx_port被svt_pcie_dirver_app的子类svt_pcie_driver_proxy实现;这个子类会override掉父类;

-

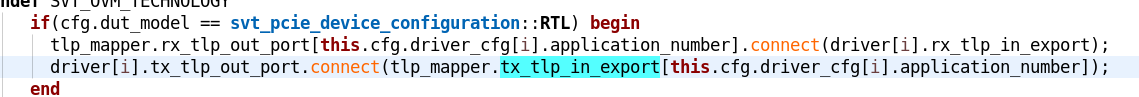

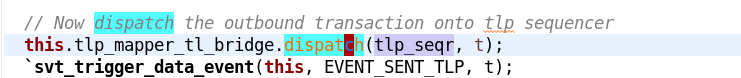

driver的port和tlp_mapper连接;tlp_mapper对tx,rx方向的TLP起到分发的作用;

-

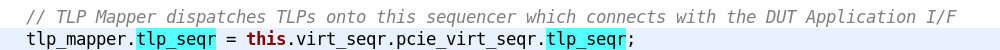

tlp_mapper将tr分发到

tlp_seqr上

-

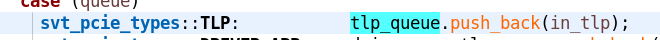

tlp_seqr和svt_pcie_tlTLM连接,接收到 tr; 将tr放入tlp_queue队列中;

-

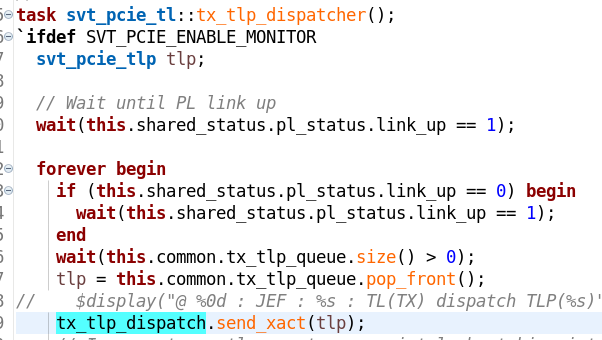

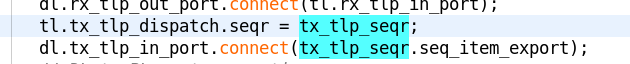

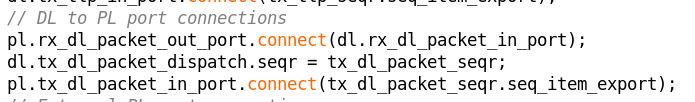

svt_pcie_tl会调用tx_tlp_dispatcher分发tr;tl的export和dl的port相连,接收tr;

-

类似的,dl层处理tr后,会将

svt_pcie_tlp转换成svt_pcie_dl_tlp的tr,送给pl层;

-

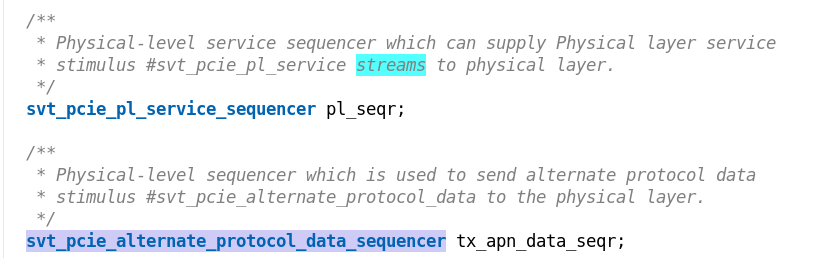

pl层的

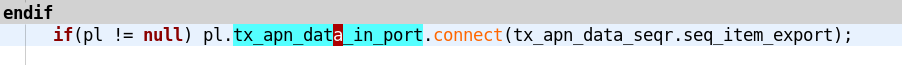

svt_pcie_pl_service_sequencer负责service tr,svt_pcie_alternate_protocol_data_sequencer负责data tr;

-

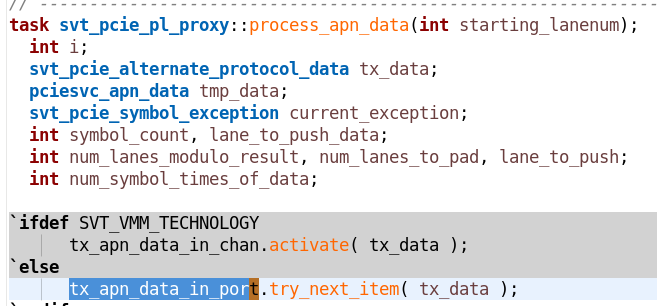

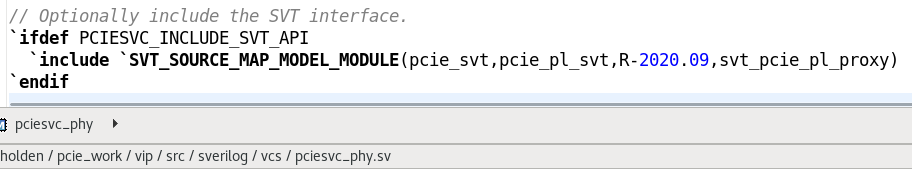

svt_pcie_pl_proxy集成于svt_cpie_pl,但是include到pciesvc_phy.sv文件中;

-

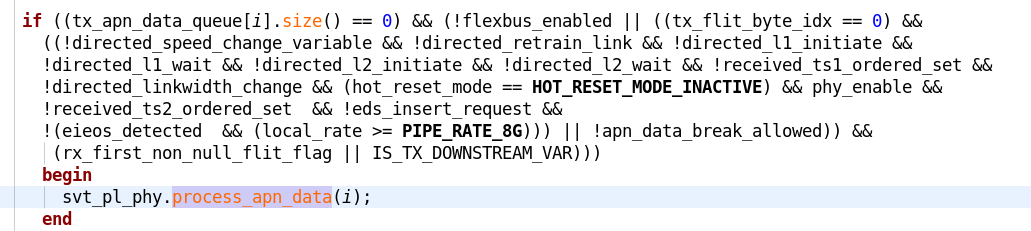

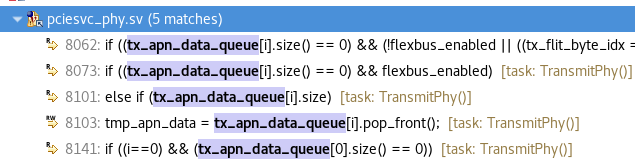

pciesvc_phy.sv中调用process_apn_data,将data放入tx_apn_data_queue,然后以serdes时序发送出去;

上述是一个Mem_Wr tr的传播流程,具体的VIP实现非常复杂;VIP支持基于SV语言的UVM环境和基于Verilog语言Tb两种方式;基于UVM的集成平台,VIP上层是UVM框架,底层仍然是通过verilog语言实现整个PCIE协议;pciesvc_xxx都是verilog代码;因为都是基于module实现的model,所以内部信号和instance都可以在verdi中打开显示:

svt_pcie_single_port_device_agent_hdl为module model顶层

port0下分别有tl,dl,pl

93

93

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?