参考文章:https://blog.csdn.net/wd12306/article/details/131454967

文章目录

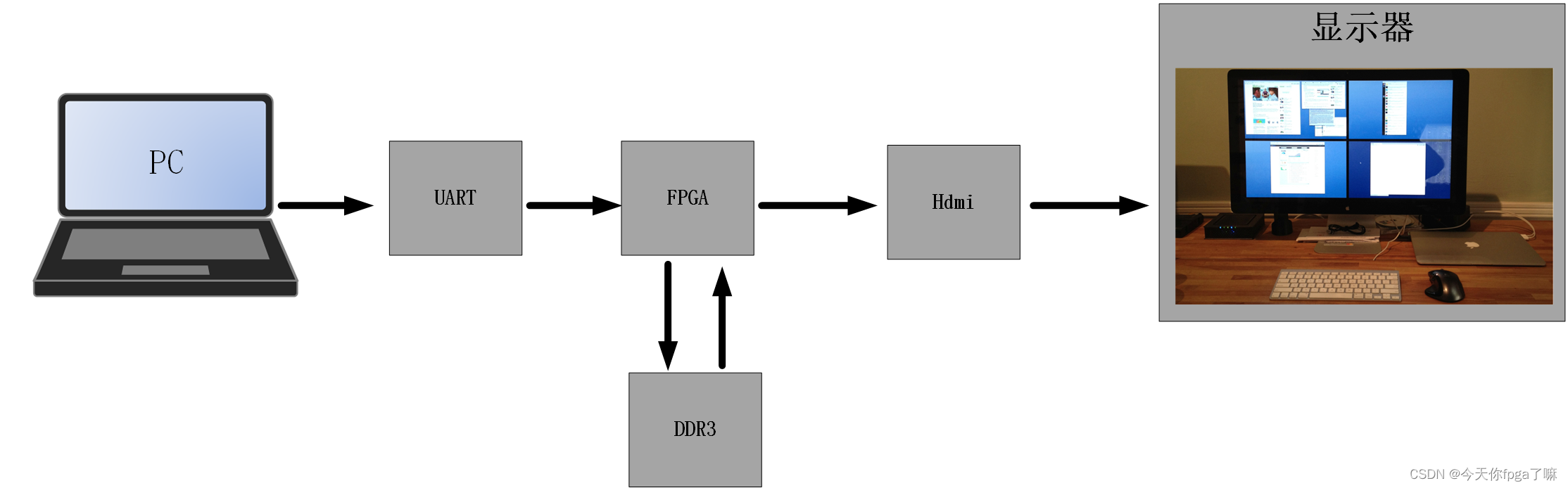

一、 整体项目简介:

本项目基于xilinxA7系列开发板实现:使用pc机将分辨率为1024*768的图像数据通过uart接口下发给fpga,存储到DDR3中,hdmi将ddr3中数据读出来显示到显示器上。

二、 过程描述:

用户将一幅1024768像素的图像通过uart接口下发到fpga开发板上【原图1pixel=24bit,其中为了满足图像像素数和ddr3用户端数据位宽相匹配,需要先将原图通过MATLAB进行处理,变成1024768(1pixel=16bit)】,数据下发到fpga后存储到DDR3中,当hdmi需要显示时,将图像数据从DDR3中读出显示到显示器上。

三、设计步骤:

1.DDR3控制器ip核–MIG ip核的使用(本篇内容)

2.使用MIG核进行fpga设计需要知道的一些基础知识

3.MIG核的初始化

4.基于A7的DDR3 SDRAM IP的写控制、读控制与读写仲裁(突发一次)

5.用户端实现DDR3 SDRAM读、写控制

6.基于 A7 的 DDR3 与 HDMI 连接器(直接从ddr3中读出数据在hdmi显示)

7.UART+DDR3+HDMI(实现完整的从下发数据到接受数据并显示)

三、DDR3控制器ip核–MIG ip核的调用

1. Ip catalog →memory interface generators (MIG)调用ip核

这里使用DDR3,下面进行具体的相关配置

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1048

1048

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?