使用Verdi dump waveform经常会遇到部分信号无法打开,可尝试一下办法:

1. 查看filelist中是否加入-v ,如果加入-v 则把他删除;

-v filename

Specifies a Verilog library file. VCS looks in this file for definitions of the module and UDP instances that VCS found in your source code, but for which it did not find the corresponding module or UDP definitions in your source code.

注:指定一个库文件,VCS会来这个文件中找源代码中例化的但在源代码中找不到的module,这里一个文件可以里面包含很多module。

-y directory

Specifies a Verilog library directory. VCS looks in the source files in this directory for definitions of the module and UDP instances that VCS found in your source code, but for which it did not find the corresponding module or UDP definitions in your source code. VCS looks in this directory for a file with the same name as the module or UDP identifier in the instance (not the instance name). If it finds this file, VCS looks in the file for the module or UDP definition to resolve the instance.

注:指定一个库文件目录,目录下的文件名和module名要一致,且要用+libext+来指定文件类型,这里的.v文件里面就只能放一个和文件名同名的module,VCS会来这个目录下找源代码中例化的但在源代码中找不到的module。

2. 如果去掉-v 后仍然无法打开信号:

- 编译选项加入 -debug_access,-debug_region=cell+lib;

- 如果有编译选项 -debug_access+all则换成 -debug_all;

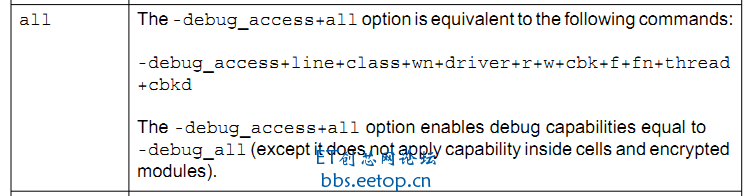

两者的区别如下:

两者基本等效除了debug_access+all 不能作用与cells 和加密模块。

-debug_access+all does not apply capability inside cells and encrypted modules.

- 查看是否存在+nocelldefinepli+,如果有则删除;

+nocelldefinepli+编译选项使用时需要加一个数字,例如+nocelldefinepli+1,+nocelldefinepli+2。

它的功能是,禁止仿真器对含有`cell_define编译原语的模块的波形转储和PLI访问。它有时也需要和+nolibcell一起使用。

由于后仿使用的库单元很多,触发器内部实现又有些复杂,所以使用+nocelldefinepli+对Dump波形的大小和仿真性能有极大的提升。波形大小通常可以下降到未使用该选项的1/10,仿真速度也接近于不dump波形时的速度。(即dump波形的开销基本可忽略)但是如果要定位库单元内部的波形则必须去除该选项。

本文介绍了解决Verdi Dumpwaveform中信号无法打开的问题,提供了检查和修改编译选项的方法,包括调整-v参数、使用-debug_access选项、检查+nocelldefinepli+参数,并解释了这些参数的功能和作用。

本文介绍了解决Verdi Dumpwaveform中信号无法打开的问题,提供了检查和修改编译选项的方法,包括调整-v参数、使用-debug_access选项、检查+nocelldefinepli+参数,并解释了这些参数的功能和作用。

2726

2726

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?