学习目标:clocking wrizard IP核

提示:clocking wrizard属于非常常用的IP核,可用于时钟的分频、倍频,在工程中需要多个时钟时,通常选用IP核由主时钟产生其他时钟。

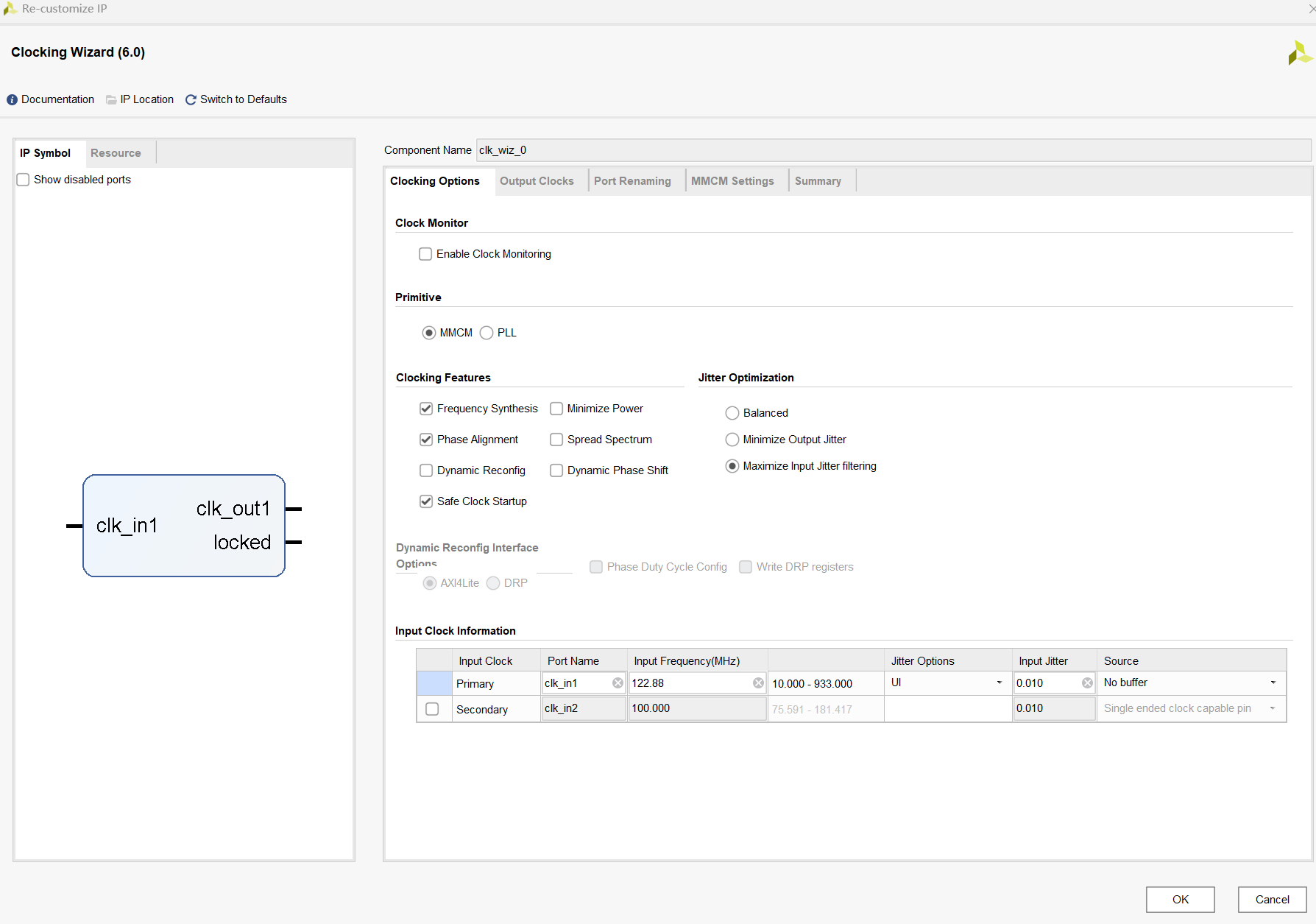

一、Clocking Options

1、Clock Monitor选项是时钟监控,一般情况下不勾选。

2、该IP核具有两种结构:mixed-mode clock manager (MMCM) 和 phase-locked loop (PLL)

这两种primitive架构不同,MMCM实现更复杂一些,具有更多的features。

MMCM可以实现Spread Spectrum和差分输出,最多可以出7个clock,PLL最多6个。倍频分频的方式也不同。

一般选择MMCM结构。

3、Clocking Features

Frequency Synthesis选项是允许输出时钟具有不同频率,就是输入和输出的频率可以不同;

Phase Alignment是相位锁定,即输出时钟的相位被锁定到一个时钟参考点,一般是指与输入时钟同步;

Minimize Power是低功耗,减少资源,但是是以频率、相位偏移或占空比精度为代价的(不建议,除非有要求);

Dynamic Recomfig是动态配置,其允许你更改原语的编程设备配置(一般用不到);

Dynamic Phase Shift是动态相移,允许你更改输出的相位关系时钟;

Safe Clock Startup是安全时钟启动,一般用于模块需要一个接一个的系统操作很有用;

Jitter Optimization一般情况选择Balanced。

(1)balanced:在抖动优化时选择比较均衡的正确带宽。

(2)minimize output jitter:使输出时钟抖动最小,但是可能会增加功耗或资源,可能导致输出相位错误。

(3)maximize input jitter filtering:该选项表示可使输入时钟抖动变大,但是可能会导致输出时钟抖动变大。

4、Input Clock Information

Primary:主参考时钟输入,input jitter 一般根据实际时钟质量选择,如果为正常内部时钟,可选0.010;最后面source选项根据输入时钟的实际情况选择,包含Single ended clock capable pin(单端时钟)和 Differential clock capable pin(差分时钟);

Secondry:副参考时钟输入。Secondry时钟工作时,会导致输出时钟的质量变差(频率、相位、抖动)。

二、Output Clocks

1、Requested是需求输出频率,Actual是实际输出频率,Duty Cycle是占空比,Drives是输出信号的时钟类型(根据实际情况选择,如果资源允许,一般情况下选BUFG)。

2、Clocking Feedback

Source:如果之前有选相位校准,该选项框为相位校准的反馈控制,一般情况下选择automatic control on-chip,在反馈信号为我们自己控制的时候可以选择user-controlled feedback。其中on-chip和off-chip为反馈路径是否在片内,一般情况下选automatic control on-chip:反馈自动控制在片内。

Signaling:选择反馈信号的类型是单端还是差分,如果选择antomatic on-chip就会默认,其他选择想根据用户实际反馈信号的类型选择。

3、Enable Optional Inputs/ Outputs for MMCM/PLL

一般情况下只选择locked,可以作为复位信号使用,或监测分频器是否输出时钟。当该分频器不产生时钟时 locked = 0,产生时钟时 locked = 1。

三、The Others

MMCM Setting可以不用改,其是由前面的设置自动生成最优的。如果需要更改,可以勾选Allow Mverride Mode。

Summaru是自己的设置摘要,无参数设置。

四、Clocking Wizard使用注意事项

1、当将主时钟选作分频器的输入时钟后,工程中其他部分还需用到该主时钟时,最好由分频器输出一个同样频率的主时钟,而不是继续用原本的主时钟。因为此时该主时钟和其他分出来的时钟”对齐“,避免出现错误。

2、输出端口数越靠后,误差越大

时钟选项如上图,Primitive选项里面:

1、MMCM:混合模式时钟管理器

2、PLL:锁相环

PLL和MMCM区别 :最大的区别MMCM可以实现动态调整,PLL没有办法实现动态调整

- 一

- 一

- 一 https://www.cnblogs.com/Ivan0506/p/16142844.html

- [ ]

学习内容:

Clocking Wizard IP:

Clocking Wizard IP 是 Xilinx Vivado 工具中的核心时钟管理模块,用于在 FPGA 中生成高精度、低抖动的多路时钟信号,其核心功能与配置要点如下:

⚙️ 一、核心功能与架构

时钟生成机制

基于 FPGA 内部的 MMCM(混合模式时钟管理器)或 PLL(锁相环)硬件资源,支持输入时钟的倍频、分频、相位偏移及占空比调整。

MMCM 相比 PLL 功能更强:

支持动态相位/频率重配置(运行时调整)

占空比可编程

相位调整精度更高(1/56 VCO 周期 vs PLL 的 1/8 VCO 周期)。

二、动态重配置能力

接口类型

AXI4-Lite 接口:通过处理器(如 Zynq PS 或 MicroBlaze)动态修改寄存器,实时调整输出时钟频率、相位)。

DRP 接口:硬件直接访问配置寄存器,无需处理器介入。

应用场景

扫频信号生成(如 88MHz–108MHz 以 0.1MHz 步进调整)、低功耗模式切换。

三、配置流程(Vivado 环境)

基础配置

在 IP Catalog 添加 “Clocking Wizard”,选择 MMCM/PLL 类型。

设置输入时钟参数(频率、源类型如差分/单端)。

输出时钟定义

添加多路输出时钟,独立配置频率、相位及占空比(例如 CLK_OUT1=200MHz/0°、CLK_OUT2=50MHz/90°)。

启用动态功能

勾选 “Enable Dynamic Reconfiguration” 并选择接口类型(AXI4-Lite 或 DRP)。

四、代码例化示例

Copy Code

clk_wiz_0 clk_gen_inst (

.clk_in1 (sys_clk), // 输入时钟(如 100MHz)

.reset (reset), // 异步复位

.clk_out1 (clk_200m), // 输出时钟 1(200MHz)

.clk_out2 (clk_50m), // 输出时钟 2(50MHz)

.locked (clk_locked) // 时钟稳定标志

);

动态调整相位示例(AXI4-Lite 接口):

always @(posedge clk) begin

if (phase_inc) begin

clk_gen_inst.mmcm_psclk = 1’b1;

clk_gen_inst.mmcm_psen = 1’b1; // 使能相位调整

clk_gen_inst.mmcm_psincdec = 1’b1; // 增加相位

end

end

五、关键注意事项

时序约束

必须在 XDC 文件中约束生成时钟,避免跨时钟域冲突。

资源与抖动

每个 Clocking Wizard 消耗 1 个 MMCM/PLL 资源,需评估 FPGA 剩余量)。

优先选择 MMCM 以实现更低抖动(尤其适用于高速接口如 PCIe/DDR)。

锁定信号(locked)

必须监控此信号,仅在 locked=1 时使用输出时钟,避免系统不稳定。

六、典型应用场景

多时钟域设计:为逻辑模块、存储器接口提供独立时钟。

高速通信:驱动 GTP/GTX 收发器、以太网 MAC。

信号采集系统:精密控制 ADC/DAC 采样时钟相位。

提示:动态重配置时,需严格遵循寄存器映射规则(参考 XAPP888 手册)。

例如:

- 搭建 Java 开发环境

- 掌握 Java 基本语法

- 掌握条件语句

学习时间:

提示:这里可以添加计划学习的时间

例如:

- 周一至周五晚上 7

- 点—晚上9点

- 周六上午 9 点-上午 11 点

- 周日下午 3 点-下午 6 点

学习产出:

提示:这里统计学习计划的总量

//例化 PLL IP 核

clk_wiz_0 clk_wiz_0(

//clock out ports

.clk_out1 (clk_50m ), //output clk_out1

.clk_out2 (clk_100m ), //output clk_out2

// Status and control signal

.locked (locked ), //output locked

//clock in port

.clk_in1 (sys_clk ) //input clk_in1

);

例如:

- 技术笔记 2 遍

- CSDN 技术博客 3 篇

- 习的 vlog 视频 1 个

- https://blog.csdn.net/2301_76707170/article/details/140875187

提示:如果文章对你有帮助,请记得关注CSDN号。本公众号将持续更新相关的技术话题,谢谢。

提示:如果文章对你有帮助,请记得关注CSDN号。本公众号将持续更新相关的技术话题,谢谢。

2612

2612

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?