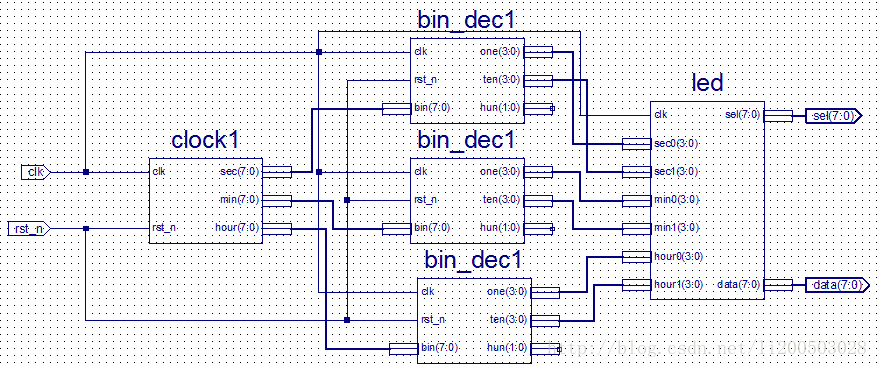

基于FPGA的可显示数字时钟,设计思路为自底向上,包括三个子模块:时钟模块,进制转换模块,led显示模块。所用到的FPGA晶振频率为50Mhz,首先利用它得到1hz的时钟然后然后得到时钟模块,把时钟模块输出的时、分、秒输入到进制转换模块后得到十进制的值再输入到led显示模块,该工程已经在FPGA开发板上亲测可用。

下图为模块示意图(实际工程中并没有采用原理图的输入方法,这里仅作示意)。

下面分模块说明:

clk1: 时钟模块,设计思路为首先根据50M晶振得到1hz的时钟,然后通过时分秒的关系得到时钟模块(具体见代码)。

输入 clk:系统时钟信号 50Mhz rst_n:低电平异步复位

输出 sec: 8bit位宽的秒位 min: 8bit位宽的分位 hour: 8bit位宽的时位

bin_dec1: 进制转换模块,设计思路完全按照之前的博文《利用verilo

本文介绍了一种基于FPGA的数字时钟设计方案,通过时钟模块、进制转换模块和LED显示模块,实现了从50Mhz晶振频率到1Hz时钟的转换,并在FPGA开发板上验证成功。时钟模块根据时分秒关系产生时钟信号,进制转换模块将二进制转换为十进制BCD码,LED显示模块则负责显示时钟数值。

本文介绍了一种基于FPGA的数字时钟设计方案,通过时钟模块、进制转换模块和LED显示模块,实现了从50Mhz晶振频率到1Hz时钟的转换,并在FPGA开发板上验证成功。时钟模块根据时分秒关系产生时钟信号,进制转换模块将二进制转换为十进制BCD码,LED显示模块则负责显示时钟数值。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?