第一讲

0 概述目标

1.掌握ASIC设计流程

* 设计、验证、中端、后端主要解决哪些问题

* 主流的EDA工具

* 验证工程师的基本技能需求

2. 掌握ASIC验证的基本概念

* Verilog Testbench和testcase

3. 掌握ASIC验证策略

* 随机化策略

* 覆盖率驱动

4.如何验证一个加法器–lab01

预学知识:数字电路+Verilog/VHDL语法基础

问题1:验证为什么使用验证方法学,有什么好处?

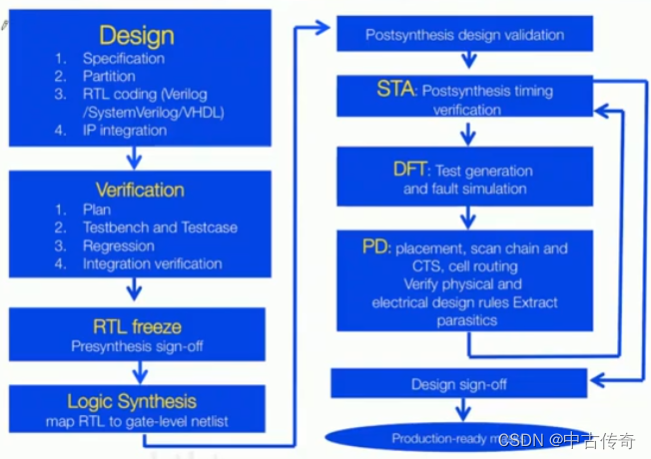

1 芯片设计流程

设计和验证基本是同步的。

DE:规格书–>分层—>RTL coding(基本是Verilog)–>IP设计集成;

DV:Plan(验证计划:测试功能点,输入 预期)–>Testbench和Testcase(两者之间区别是什么)–>Regression(回归测试)–>Intergration Verification.

RTL freeze:sign-off 定好了,不能再动了;

Logic Synthesis:Map RTL to gate-level netlist.

STA:静态时序分析

DFT:测试

PD:布局布线

1.1 相关设计技能

DE:Verilog Synthesis SoC/IP

DV:SystrmVerilog UVM

STA/DFT:

PD: CTS P&R

环境:Linux+DEA+FPGA

1.2 主流EDA

DE:逻辑仿真工具:VCS/IUS/QuestaSim

代码产看/规则检查:Verdi Spyglass

DV: 逻辑仿真工具:VCS/IUS/QuestaSim

查看波形:Verdi DVE

STA/DFT:Tessent,DesignCompiler, PrimerTime,Formaily

PD:IC compiler,SOC encounter, Olympus Calobre,StarRC

1.3 对应的要求

DV:UVM,Verilog/SV C++ Perl makefile ;AMBA总线;IP(I2C UART);PCI-E

DE:

2 Verilog TestBench

- 产生激励Generate stimulus

- 将激励输入到待测设计:DUT

- 获取响应

- 检查响应的正确性

- 根据验证目标评估项目进度(覆盖率)

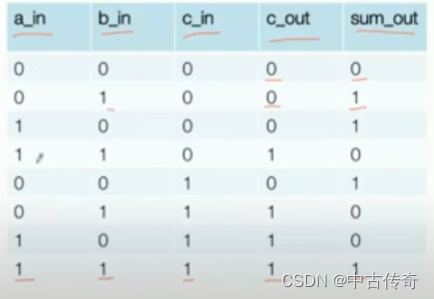

2.1 lab01-全加器

功能:真值表表示

验证:a. 功能完整性 b.穷举法 c.代码覆盖率

lab01: 编译 仿真 GUI

assign 等价于always中的组合逻辑,两者可互相重写。

如何写一个testbench:

S1. 顶层文件 fu_adder_tb,在tb中例化module,进行连线

S2:产生时钟和复位信号

S3:产生驱动,并把输出拉出来

自动化编译makefile–直接在Linux terminal中输入make run即可做仿真。

永远切记:EDA工具书永远都是用来查阅的,而不是从头读到尾的

1361

1361

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?