1. 前言

2. 整体架构

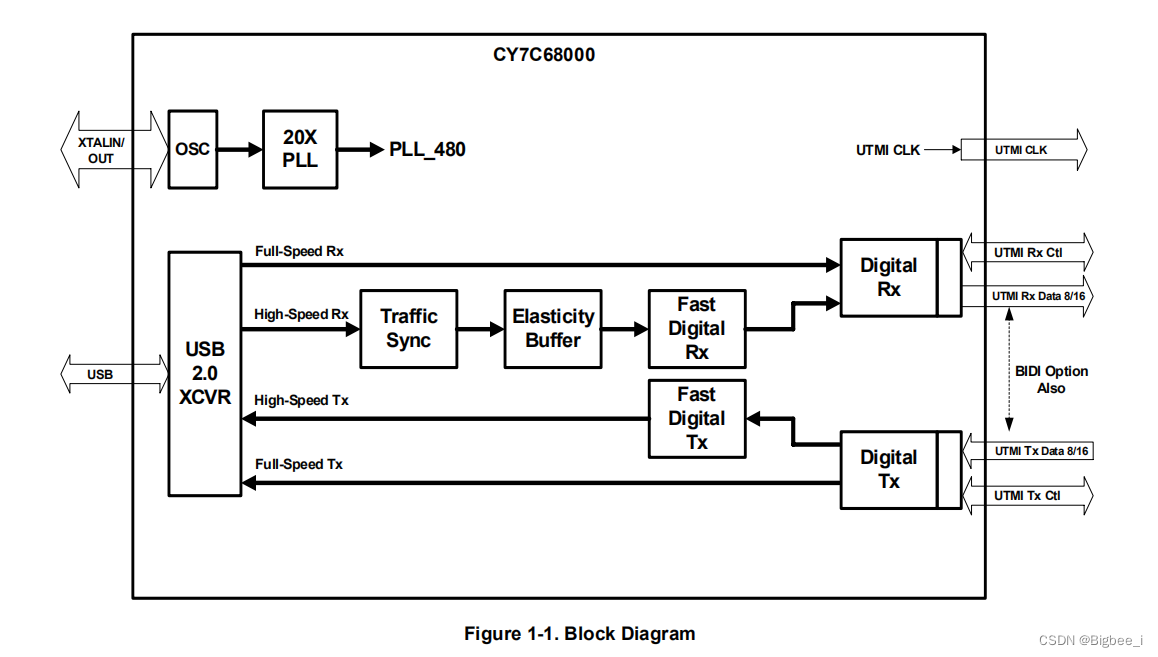

下图为CY7C68000的整体架构,左为与USB物理层相连的接口,右边为UTMI接口。

3. 功能概述

3.1 USB信号速度

- Full speed, with a signaling bit rate of 12 Mbps

- High speed, with a signaling bit rate of 480 Mbps

不支持Low speed

3.2 收发器时钟频率

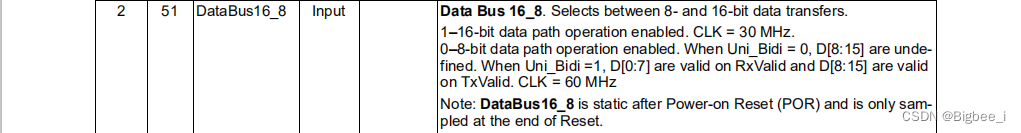

根据收发器并行数据总线的要求,片上锁相环(PLL)将24MHz振荡器乘以30/60MHz。默认的UTMI接口时钟(CLK)频率由DataBus16_8引脚决定。

3.3 复位

外部输入复位信号,能够重置芯片。

4. 管脚

4.1 管脚分布

两种形式的管脚分布图

56-pin QFN

56-pin SSOP

4.2 管脚说明

- 电源脚

- USB物理层传输dp,dm脚

- 数据脚 8或者16bit inout类型

- 时钟脚 PHY芯片输出

- 复位脚 输入

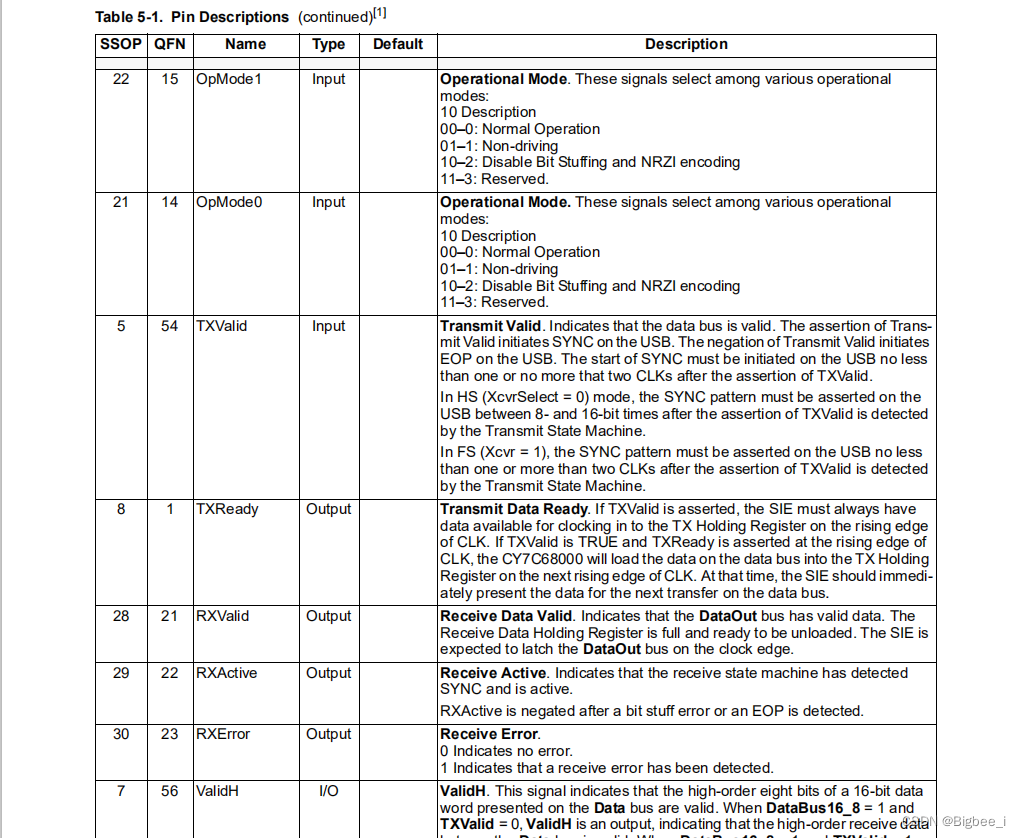

- UTMI的模式选择脚 XcvrSelect TermSelect

- Suspend 挂起控制脚

- LineState 输出状态

- OpMode 一般设置为Normal Operation

- 状态信号

- Data Bus16_8,有两种模式

- 1-16bit模式,时钟为30MHz

- 当0-8bit 模式时,当Uni_Bidi为0时,D[8:15]不使能,当Uni_Bidi为1时,D[0:7]为收数,D[8:15]为发数。

- Uni_Bidi 当HIGH为高时,设置为8-bit

5. 说明

不同芯片的UTMI物理接口不同,但是在实现逻辑是必须满足UTMI技术协议要求。

151

151

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?