1. 前言

协议原文连接:

PCIe5.0协议链接:

链接: https://pan.baidu.com/s/1lm2-PzlUaGDQdiEWNak8Vg?pwd=zuug 提取码: zuug

PCIe6.0协议链接

链接: https://pan.baidu.com/s/1mv5ca0VSS6L7t_vjAdd3mA?pwd=2f3x 提取码: 2f3x

觉得有帮助的朋友们可以点个赞!!

2. 背景

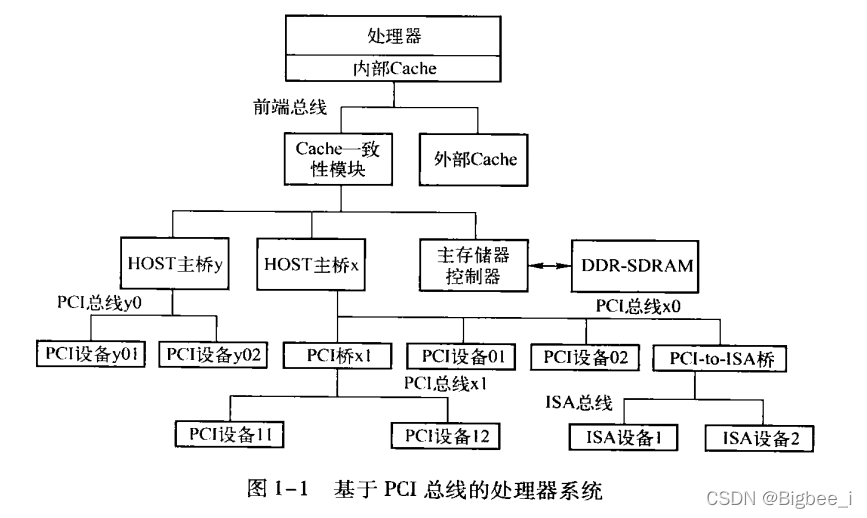

下图为PCI总线的架构图,与PCIe类似。

PCIe总线是从PCI基础上发展而来的,所以本文会存在PCI的概念,基本上都是公用的。由于PCI的带宽捉襟见肘,流量控制和数据传输质量等原因,发展出了PCIe。

分析PCI被替代原因也能得到PCIe的一些优点:

- PCI为共享总线,所有的设备使用总线带宽,使得数据带宽的利用率很低。

- PCI采取的是提高总线宽度和频率的方法提高的传输带宽,这样并不是最优的。当然自己在简单设计时,也可以考虑使用这样的方法提高传输带宽

- 提高频率后负载的驱动能力变得更差,33Mhz可以驱动10个,66Mhz只能驱动4个了。

- 并未考虑数据质量的问题,实时设备只能轮流使用总线,当一个设备长期占用总线时,其他的设备无法传输。

- 并行总线

所以,PCIe应运而生,PCIe几个关键特点:

- 采用虚通路的方式进行连接,计算机网络的内容,可以百度一下,相较于固定通路能够更加灵活,可以解决服务质量问题。

- PCIe总线由若干层次组成,事务层,数据链路层,物理层。类似于互联网使用的TCP/IP协议。对于IC设计开发者,最需要关心的是事务层的设计。分层设计会带来延时。

- PCIe 总线在系统软件级与 PCI 总线兼容,基于 PCI 总线的系统软件几乎可以不经修改直接移植到 PCIe 总线中。绝大多数 PCI/PCI-X 总线使用的总线事务都被 PCIe 总线保留,而PCI 设备使用的配置空间也被 PCIe 总线继承。基于 PCI 体系结构的系统编程模型,几乎可以在没有本质变化的前提下,直接在 PCIe 体系结构中使用

- Root Complex (RC) 从Host主桥的基础上发展而来的,相比Host主桥多了更多的功能。

- 端到端的高速差分串行总线,使能能够支持更高的时钟频率和更少的数据线。但是在数据的接收和发送端都要进行串并转换,这样会带来较大的延时。

- 无单独的时钟线,通过CDR(Clock Data Recovery)在数据报文中提取本地参考时钟。

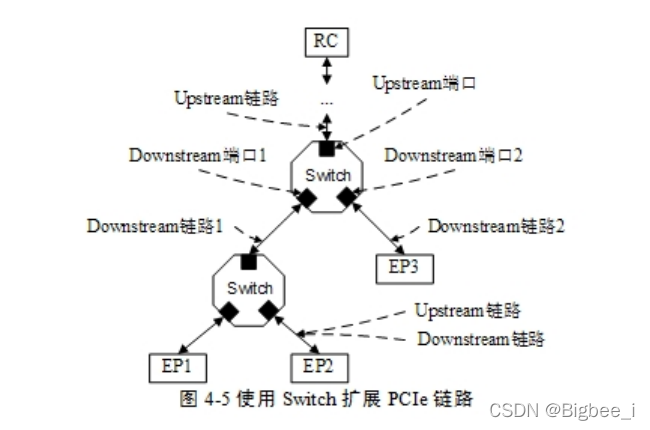

由于端到端方式的连接,在总线拓扑结构上,PCIe略有不同:

设计时的难度 RC>Switch>EP

3. 重要概念

3.1 通用处理器结构

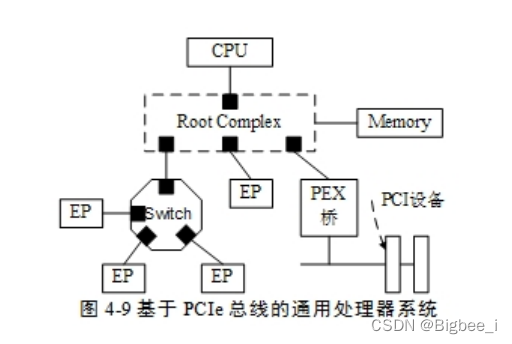

PCIe 总线规范并没有规定 RC 的实现细则。在有些处理器系统中,RC 相当于 PCIe 主桥,也有的处理器系统也将 PCIe 主桥称为 PCIe总线控制器。而在 x86处理器系统中,RC 除了包含 PCIe 总线控制器之外,还包含一些其他组成部件,因此 RC 并不等同于 PCIe 总线控制器。处理器需要连接更多 EP 时,需要使用 Switch 进行链路扩展。

3.2 RC

在 x86处理器系统中,RC 内部集成了一些 PCI 设备、RCRB(RC Register Block)和 Event Collector 等组成部件。其中RCRB 由一系列“管理存储器系统”的寄存器组成,而仅存在于 x86处理器中;而 Event Collector 用来处理来自 PCIe 设备的错误消息报文和 PME 消息报文。RCRB 寄存器组属于 PCI 总线域地址空间,x86处理器访问 RCRB 的方法与访问 PCI 设备的配置寄存器相同。在有些 x86处理器系统中,RCRB 在 PCI 总线0的设备0中。

RC还能完成存储器域到 PCI 总线域的地址转换。类似于PCI中的HOST主桥

3.3 Switch

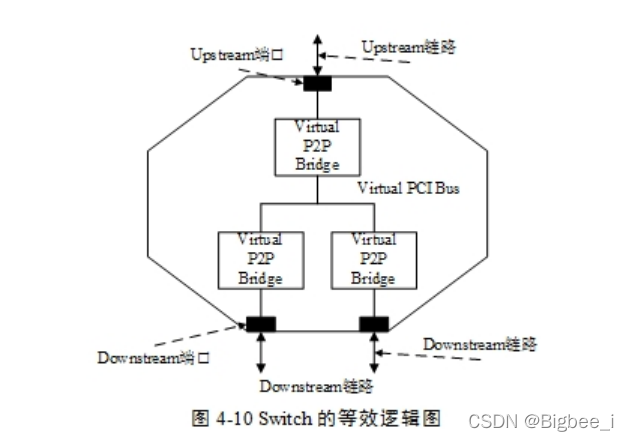

一个 PCIe 链路需要挂接多个 EP 时,需要使用 Switch 进行链路扩展。一个标准 Switch具有一个上游端口和多个下游端口。上游端口与 RC 或者其他 Switch 的下游端口相连,而下游端口可以与 EP、PCIe-to-PCI-X/PCI 桥或者下游 Switch 的上游端口相连。

但是还有一种特殊的连接方式Crosslink,运行Switch的下游端口与其他的Switch的下游端口相连。上游端口与上游端口相连。

3.4 端到端

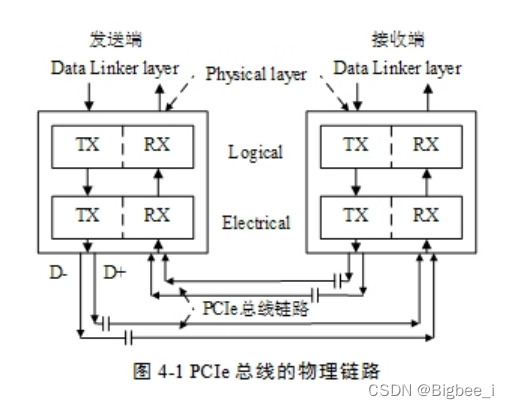

下图是PCIe总线的物理链路的一个数据通路(lane),由两组差分信号,共四根信号线组成。一个设备的TX与另一个设备的RX相连,一个PCIe链路可以由多个Lane组成。

目前 PCIe 链路可以支持1、2、4、8、12、16和32个Lane,即×1、×2、×4、×8、×12、×16和×32宽度的 PCIe 链路。每一个 Lane 上使用的总线频率与 PCIe 总线使用的版本相关。

3.5 BAR空间

- 为了完成地址域的转换

Base Address Register,字面意思,基地址寄存器,这个基地址指的就是PCI总线对应的地址空间,与PC设备无关。在 PCI 设备的配置空间中,共有6个 BAR 寄存器。每一个 BAR 寄存器都与 PCI 设备使用的一组 PCI 总线地址空间对应,BAR 寄存器记录这组地址空间的基地址。在 BAR 空间中可以存放 I/O 地址空间,也可以存放存储器地址空间。

3.6 Posted / Non-Posted

Posted总线事务是指PCI主设备向目标设备进行数据传输时,数据到达PCI桥后,由PCI桥接管来自上游总线的总线事务,并将其转发到下游总线,此时上游总线可释放。 使用这种数据传输方式,数据请求在通过PCI总线后,就可以逐级释放总线资源。

Non-Posted总线事务是指PCI主设备向目标设备进行数据传输时,数据必须到达最终目的地后才能结束当前事务总线的传输方式。 PCI总线在没有结束当前总线事务时必须等待传输完成,不会释放总线资源。这种等待将严重阻塞当前的PCI总线的其他数据传送。因此在PCI总线中使用Delayed方式完成Non-Posted,在PCIe总线中使用Split方式完成 Non-Posted总线事务。

Split传输可以看成是将请求和完成分开,分别使用Posted方式进行的传输。先传输请求,请求传输完成,设备准备好后重新申请总线。

具体可以查看这篇博客。

Posted and Non-Posted 详解

4. 层次结构

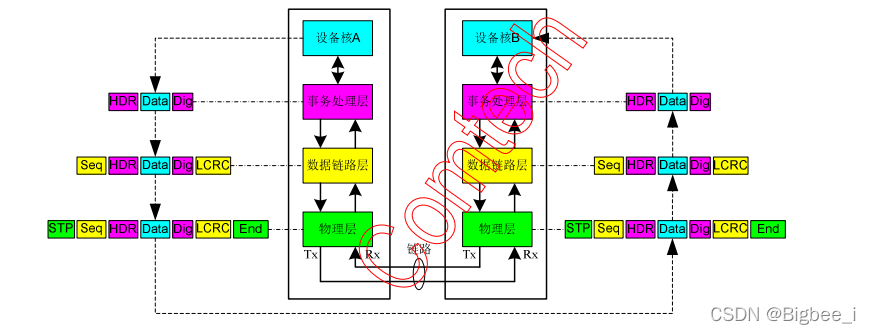

对于常见协议来说,几乎都是由三层结构组成:物理层,数据链路层,事务层,三层结构各司其职。

事务层包(TLP),数据链路层包(DLLP),物理层(PLP)产生于各自所在层,最后通过电或光等介质和另一方通讯。这其中数据链路层包(DLLP),物理层(PLP)的包平常不需要关心,在 IP 核中封装好了。在 FPGA 上做 PCIe 的功能,变成完成事务层包(TLP)的处理。

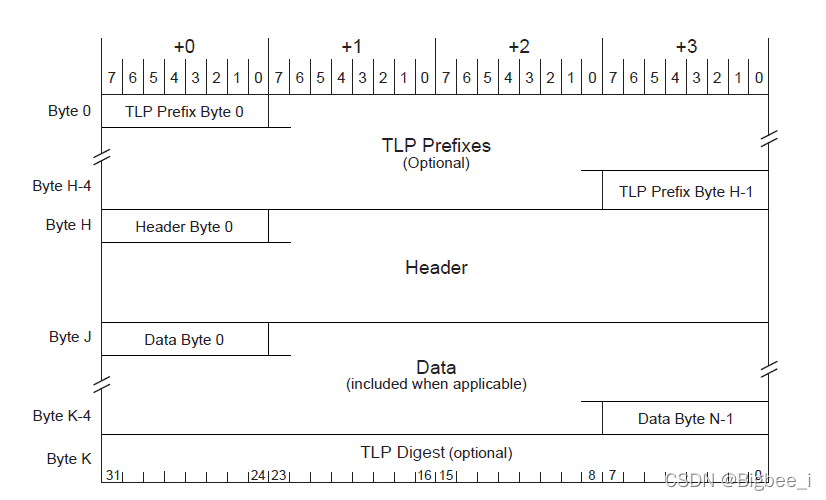

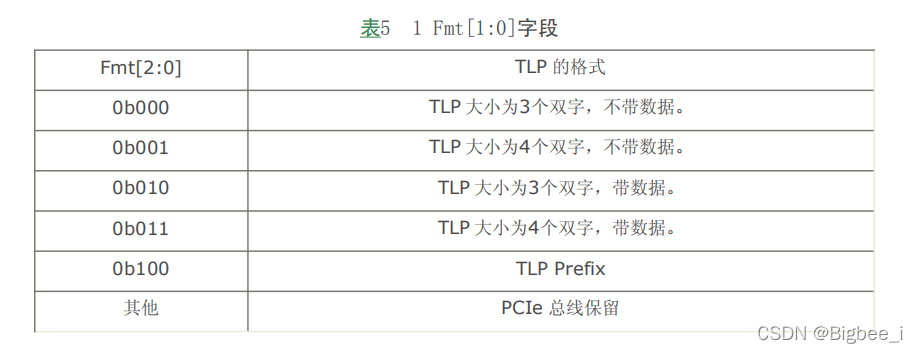

TLP 有三部分组成,帧头、数据、摘要(或者称 ECRC)。TLP 头标长 3 或者 4 个 DW,格式和内容随事物类型变化;数据端为 TLP 帧头定义下的数据段,如果该 TLP 不携带数据,那该段为空。Digest段(Optional)是基于头标、数据字段计算出来的 CRC,成为 ECRC,一般 Digest 段有 IP 核填充。所以,PCIe 的处理在用户层表现为处理 TLP 中头标和数据段。

4.1 物理层

除了端到端中提到的数据线外,还存在一些辅助信号:(#代表低有效)

- PERST# 全局复位信号,由处理器系统提供。

- REFCLK+和REFCLK- PCIe使用这组信号与处理器系统同步

- WAKE# PCIe设备使用这个信号想处理器系统提交唤醒请求,使处理器重新为PCIe设备提供主电源。除此之外还可以使用Beacon信号实现复位功能,与 WAKE#信号实现唤醒功能不同,Beacon 使用 In-band 信号,即差分信号 D+和 D-实现唤醒功能。Beacon 信号 DC 平衡,由一组通过 D+和 D-信号生成的脉冲信号组成。

- SMCLK和SMDAT x86处理器的 SMBus(System Mangement Bus)相关,由I2C总线发展而来,由于35ms的超时复位功能,总线频率最低10KHz,最高100KHz。主设备对从设备一些配置时用到吧(个人猜想)

- JTAG JTAG信号由TRST#和TCK,TDI,TDO,TMS信号组成,其中TRST#为复位,TCK为时钟,TDI,TDO为数据线,TMS为模式选择。FPGA可以通过JTGA接口实现ISP(In-System Programming)功能,进行系统级调试,读取寄存器等等操作。

- PRSNT1#和 PRSNT2# 与热插拔有关

4.2 数据链路层

4.3 事务层

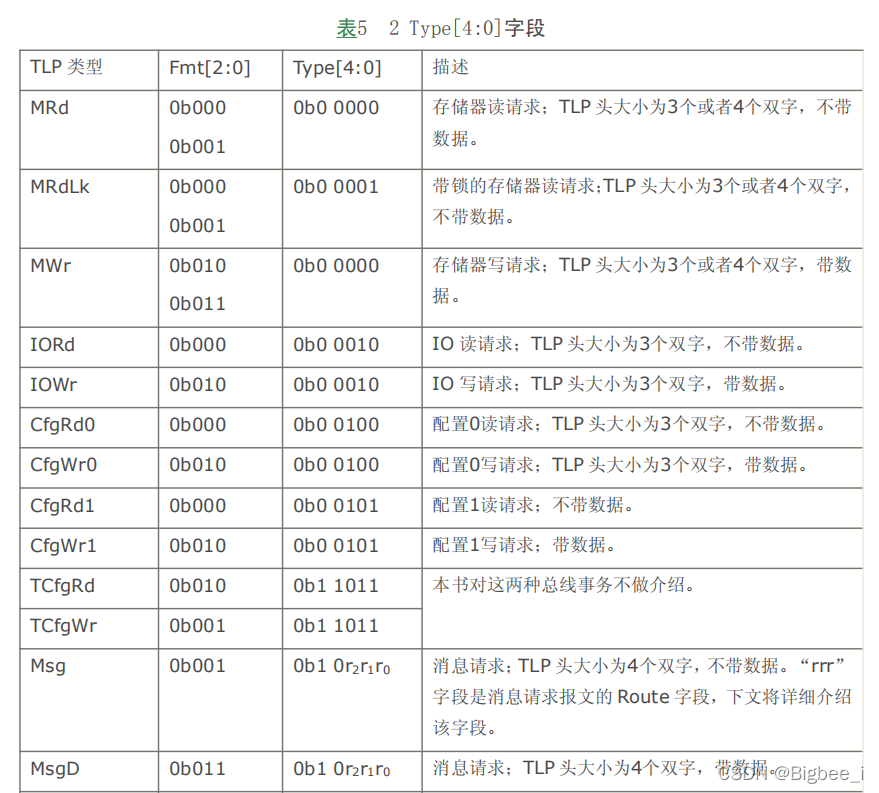

事务层是 PCIe 总线层次结构的最高层,该层次将接收 PCIe 设备核心层的数据请求,并将其转换为 PCIe 总线事务,PCIe 总线使用的这些总线事务在 TLP 头中定义。PCIe 总线继承了 PCI/PCI-X 总线的大多数总线事务,如存储器读写、I/O 读写、配置读写总线事务,并增加了 Message 总线事务和原子操作等总线事务。

PCIe 总线使用的数据报文首先在事务层中形成,这个数据报文也被称之为事务层数据报文,即 TLP,TLP 在经过数据链路层时被加上 Sequence Number 前缀和 CRC 后缀,然后发向物理层。

4.3.1 TLP包结构

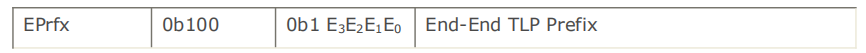

一个完整的 TLP 由

-

TLP Prefix (一个或多个)

-

TLP Header (包含总线事务,路由信息等内容)

-

Data Payload (可选,最小为0DW,最大为1024DW)

-

TLP Digest (可选,是否包含由TLP头决定)

组成。

5. 附录

6. 后言

觉得有帮助的朋友们可以点个赞!!

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?