最近在学习SV这门语言,做了一下Synopsys公司的lab(ces_svtb_2006.06-SP1.tgz),写一点自己的学习笔记。

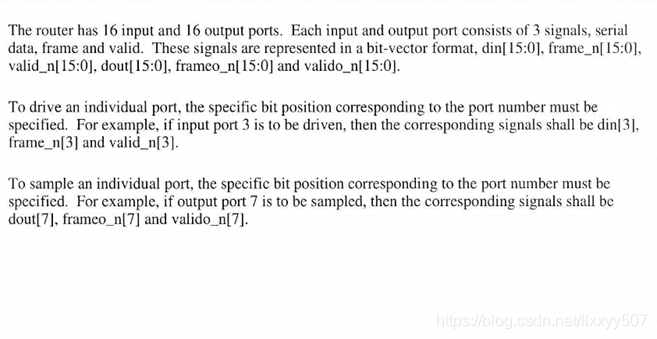

Synopsys公司的这个lab验证的DUT为一个router。介绍如下:

看了下router.v这个code,发现它还有一个端口ouput [15:0] busy_n ,在这个图上面没有画出来。

我写的lab1的SV code主要分为几个部分:

1,Interface:

我写的这个interface在clocking cb块里面声明了 output reset_n,(sync reset_n),然后在modport中也声明了一个output reset_n,(async reset_n),这表明reset_n即可以同步也可以异步。

clocking块中使用了default 语句,用了#1延时,表明了在posedge clock,#1前sample input,#1后drive output,就像verilog里面DFF采集输出一样。不用时,默认的为:default input #1 output #0

2,TEST

test里面为一个automatic program,注意接口就是router_io.TB,例化名字为rt。reset()这个task,给reset_n这个端口进行了两次赋值,一次就是异步的,一次就是同步的。

注意给clocking里面的信号赋值的时候都必须使用非阻塞赋值(<=)

3,TOP

在top例化了一个接口a_if,并连接上时钟SystemClock,注意例化DUT时的连接方式,interface声明中时钟为输入端,连接DUT时也是直接a_if.clk,和interface块中的信号连接方式相同。

如果DUT中也是采用的接口形式(像router_test中的那样),那么在例化时只需要router U_dut (a_if)。

2446

2446

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?