Verilog和SystemVerilog作为一种“松散类型”的语言已经被很多工程师广泛的用于设计验证领域,但是这并不是说各种电路结构或者验证环境中就可以肆无忌惮的随意使用,特别是在不同位宽的信号进行计算时,结果经常出现与自己表达式预期的结果不一致,以至于怀疑自己数学是不是体育老师教的,为此,本文将示例说明表达式不同位宽信号进行运算时,结果到底应该是什么。

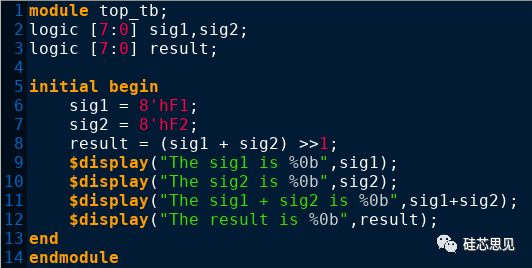

首先我们先看一个运算的各位数位宽一致,但是计算结果与期望不一致的示例。

【示例】本示例中,期望将运算结果向右移动一位,这样两个数的和的进位位就可以保留下来。

【仿真结果】

示例中,(sig1+sig2)结果应该为“1_1110_0011”,以为后的结果应该包含进位位“1”,但是实际result中并没有包含进位位。这是为什么呢?这是因为表达式中(sig1+sig2)进位操作时会产生一个中间结果,这个中间结果的位宽与sig1和sig2最宽的那一个数保持一致。示例中因为sig1和sig2都是8位宽,所以这个中间结果并没有包含进位位,因此进行移位操作的这个中间结果实际上只包含了(sig1+sig2)“和”的部分,因此移位后的结果进位位“消失”了,跟我们期望的结果不一致。为了解决这样的问题,我们需要保持中间结果中能够有效地把和的进位位保留下来,那么如何可以实现进位结果保留下来并且能够参与到移位操作中呢?我们一块看看下面几个示例。

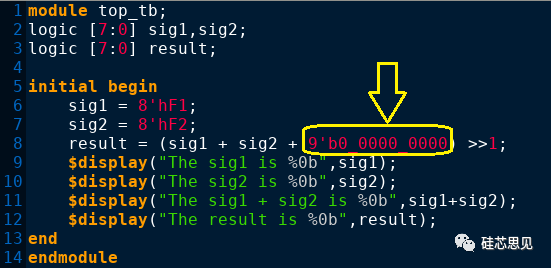

【示例】方法一:加入宽位宽数据拓展结果

【仿真结果】

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2810

2810

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?