1 FPGA硬件系统设计

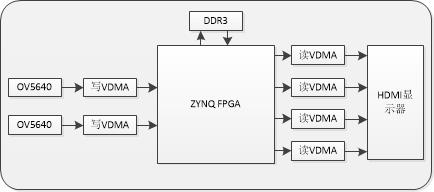

基于ZYNQ FPGA实现图像数据采集、存储、处理和显示系统框图如图1所示。说明:2路摄像头采集系统,4种显示方案,原始数据显示2路,经过算法处理2路。

图1 系统设计

OV5640模块:图像传感器,视频流来源。

写VDMA模块:硬件采集到的数据通过写VDMA存储到PS端的DDR中。

ZYNQ模块:ZYNQ-7000系列FPGA,ARM + FPGA架构,核心处理芯片。

读VDMA模块:通过读VDMA从PS端的DDR中读取图像数据。

RGB转换DVI模块:32bit转为RGB888,再转为DVI时序输出到HDMI显示。

HDMI显示器:显示图像视频数据。

2 关键技术

1)OV5640摄像头

设计中采用两片美国OmniVision公司的CMOS图像传感器OV5640,OV5640芯片支持DVP和MIPI接口。为保证OV5640正常工作,需要依次实现以下时序要求。

a、ResetB拉低、PWND拉高;

b、DOVDD和AVDD同时上电;

c、电源稳定5ms后,拉低PWND,再过1ms,拉高ResetB;

d、20ms后初始化OV5640DESCCB寄存器。

e、通过IIC接口配置,配置目标为RGB565、30FPS、720输出格式;

f、FPGA接收来自OV5640的视频流数据输入,需要对摄像头完成相应的时序操作。每次传输8bit,16bit为一个像素点,所以要进行数据转换8

基于ZYNQ FPGA实现图像采集存储显示

最新推荐文章于 2024-03-16 19:45:13 发布

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

8634

8634

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?