一、区别

parameter: 可以在实例化时修改参数值

localparam:只能在当前模块使用,不能进行实例化

二、用法

2.1 设计文件中parameter的用法

直接在模块名后面 #(parameter 参数名=参数值)

module top_FIFO_ly #(

parameter FIFO_DEPTH_16 = 16,

parameter ADDR_4 = 4

)

(

//写

input w_en,

input w_clk,

input w_rst_n,

input [FIFO_DEPTH_16-1:0] w_data,

output w_full,

//读

input r_en,

input r_clk,

input r_rst_n,

output r_empty,

output [FIFO_DEPTH_16-1:0] r_data

);

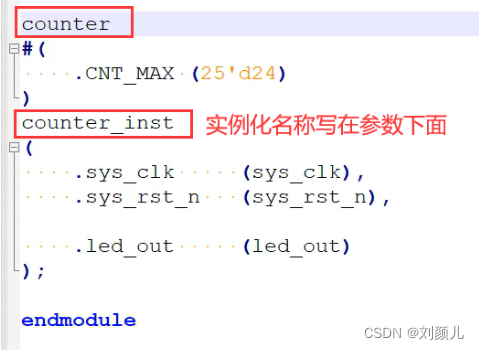

2.2 例化模块时parameter的用法

在模块名后面直接 #(.参数名 (参数值))

3777

3777

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?