Verilog中的parameter

1.module parameters

module parameters有parameter和localparam两种,它们所代表的值都可在编译时进行修改(参数传递),parameter可直接修改,localparam只能间接修改。

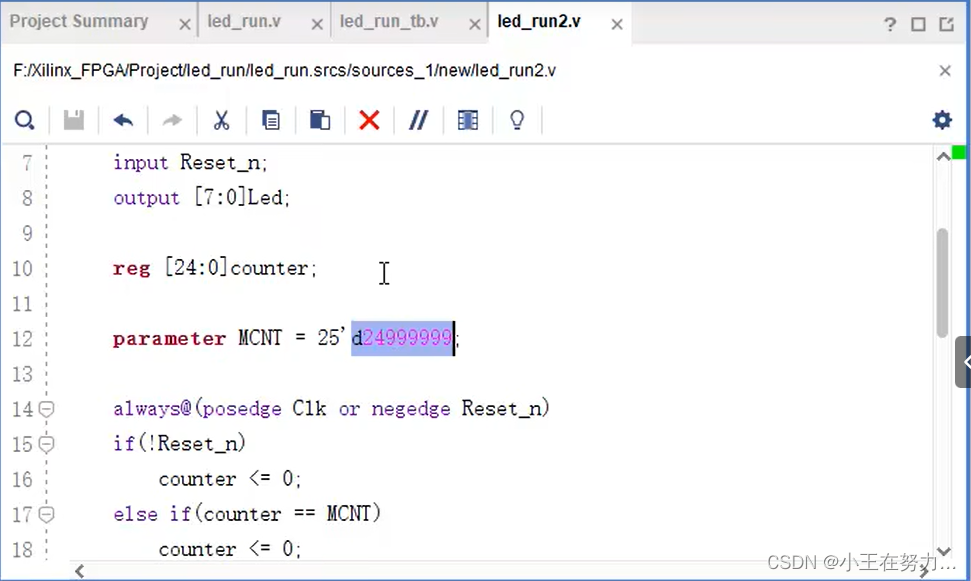

1.1 parameter

在模块中声明后,后续编译时还可以被重新声明的值所覆盖。

————————————————

【注】:

1)如果参数在声明时没有指定type和range,则默认为最后赋值给参数的type和range;

2)如果参数有指定range,但没有type,则它的符号默认为unsigned,并且range和符号都不会被后面的声明所覆盖;

3)如果参数有指定range,并且指定为有符号type,则它的range和符号都不会被后面的声明所覆盖;

1.2 localparam

localparam除了不能直接对其进行修改外,其他属性与parameter一样。可通过在声明时将parameter赋给localparam进行间接修改。状态机一般都使用localparam。

parameter X = 3;

localparam Y = X*2;

这样修改X就间接修改了localparam Y的值。

1.3 编译时parameter的参数传递

对parameter的修改有两种方式:

1)defparam声明

2)模块实例声明

————————————————

【注】:如果defparam声明和模块实例声明冲突了,则使用defparam声明的值。

1.3.1 defparam声明

defparam使用层次化名称对模块中的参数重新赋值,如下面的代码所示,

————————————————

【注】:如果有多个defparam声明一个parameter,则该parameter取文本(代码)中最后一个defparam声明的值。

1.3.2 模块实例声明

1)有序列表

列表的顺序必须严格按照模块中参数声明的顺序,且不可跳过任何一个参数。如下面代码,mod_mod中有三个参数,a = 4,b = 5,c = 6.

mod_mod #(1, 2, 3) mod_a(); //三个参数都修改

mod_mod #(4, 2, 3) mod_a(); //只修改b和c,但是也要将a的值声明

mod_mod #(1, 5, 3) mod_a(); //只修改a和c,但是也要将b的值声明

2)参数名

声明时的参数名称需要和模块实例中的参数名称一致,不需要重新声明的参数可以缺省。

2. `define与parameter的区别

define作用于整个工程,而parameter只作用于本模块,一旦define指令被编译,则在整个编译过程中都有效,所以仿真时使用`define相对于parameter重声明占用更少的内存

203

203

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?