Die2Die Adapter的功能有以下几点:

- 通过Sideband对协议参数的协商和交互。(链路初始化的最后一步)

- 对各个不同的上层FDI协议的不同FLIT 封装。

- 电源管理和状态协商

- 链路可靠性:CRC/Retry和重传

- 链路可靠性:runtime自测试

上一篇讲了第一条,本篇从第二条开始。

对各个不同的上层FDI协议的不同FLIT 封装。

如上文所述,D2D Adapter负责将FDI接口送下来的FLIT payload再次封装成D2D flit. 针对不同的上层协议,封装方式也有所区别。

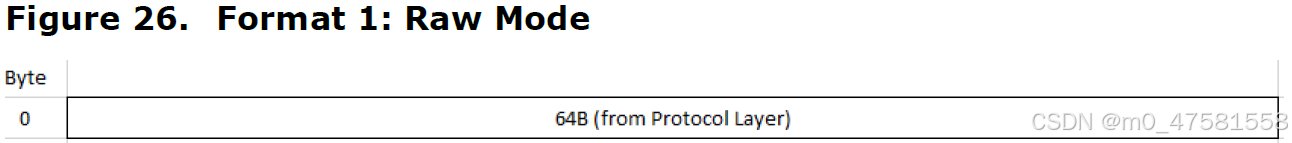

Raw Mode

在Raw mode下,D2D Adapter不对FDI接口下来的任何FLIT进行改变,直接透传到RDI接口。UCIe FLIT Format 1.

*Raw mode不需要Retry。

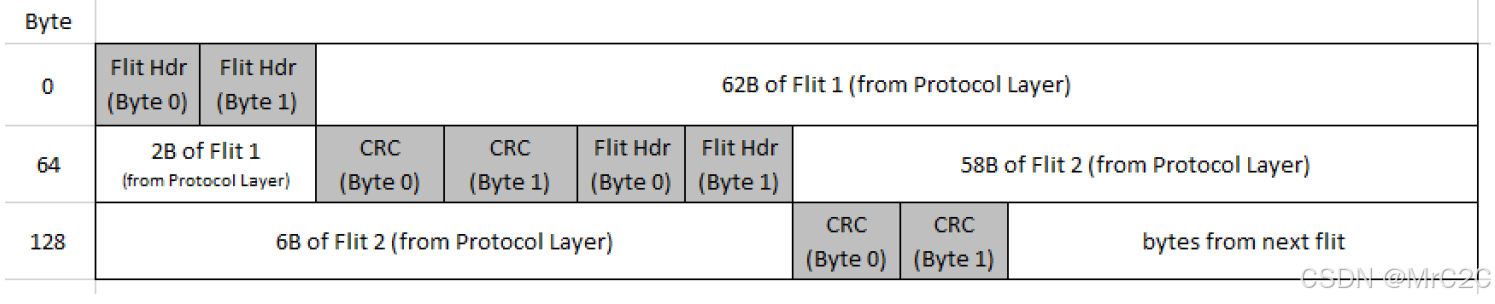

CXL 2.0 or "CXL 68B-Enhanced Flit Mode"

UCIe FLIT format 2 & Format 7.

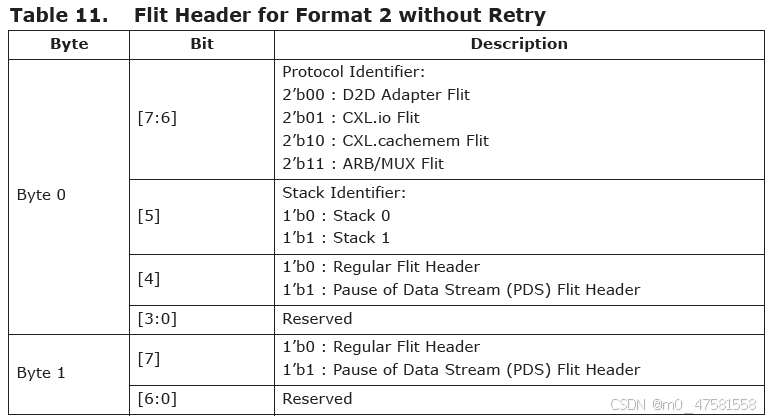

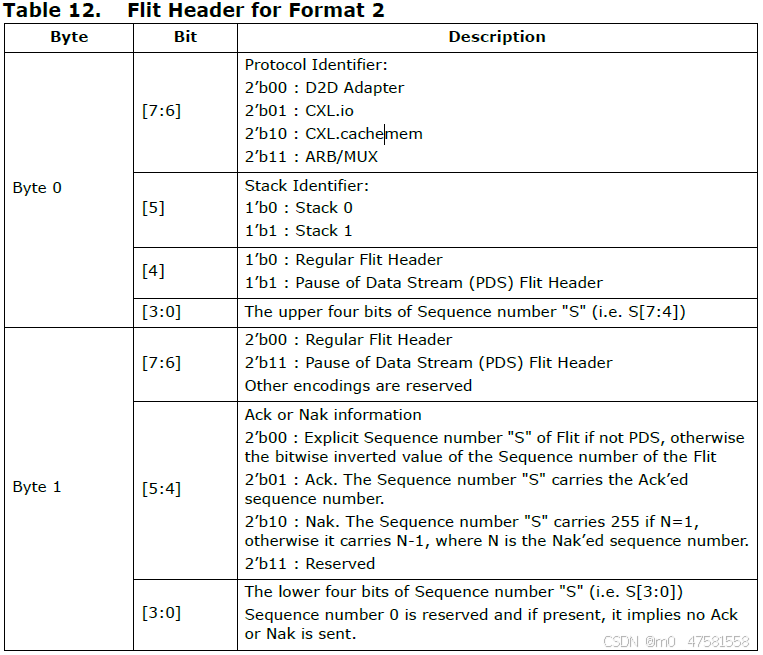

在此模式下,协议层通过FDI接口下发64Bytes数据或者信息(取决于协议层定义),Adapter将上层下发的数据增加2个byte的Flit header,并计算和添加2 bytes的CRC。Flit Header格式见下面表格:

上述两种包头中,无论是否enable Retry,Flit CRC都是必须要计算的,接收端检测到CRC Error,需要设置和报告Uncorrectable Internal Error。CRC计算边界采用128Bytes边界,在68Byte FLIT场景下,从FLIT byte 0计算到byte65, 并设置byte 67-127为0来计算CRC。*此中设计是为了兼容后一种FLIT(per 128bytes算一次CRC)

由于D2D Adapter层对上层下发的64Bytes数据增加了4个Byte (Hdr + CRC),会导致原始Flit无法对齐到物理层要求的最小对齐边界16Byte的要求,这就需要Adapter设计需要支持68 - 64=4Bytes的 Flit shifter来暂存数据,并且随下一个Flit发送出去。

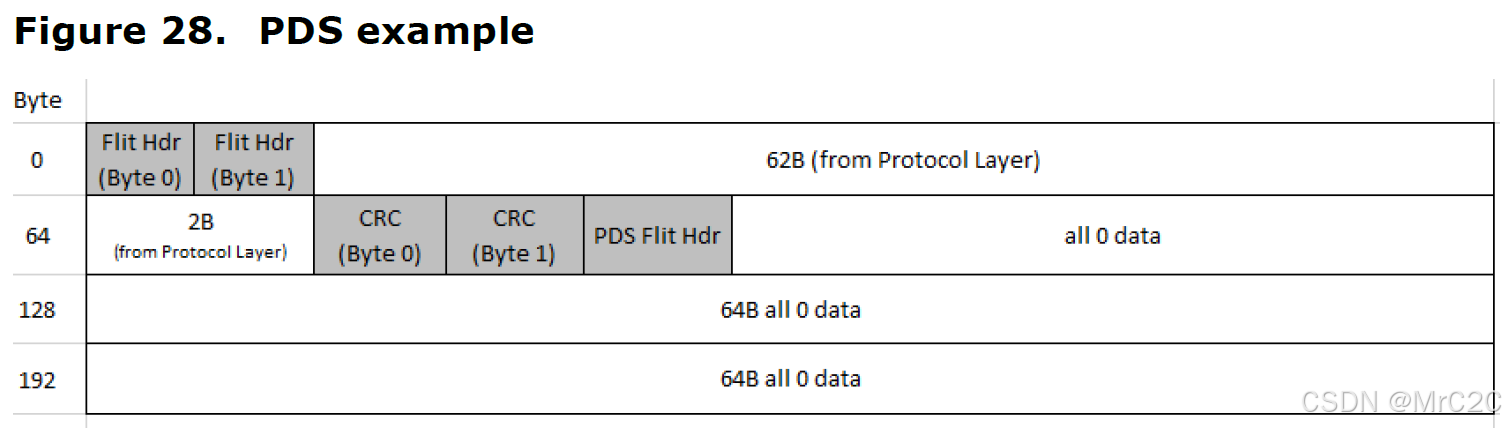

如果Adapter暂未从协议层收到数据,Adapter需要发送一种Pause of Data Stream (PDS)Flit,格式如下:

接收端Adapter收到PDS后,检查PDS field并丢弃,不能送给上层协议层。

PDS Flit header有特定格式要求:

- Byte0[4] = 1'b1

- Byte1[7] = 1'b1

- Byte1[6] = 1'b1

- Byte1[5:4] = 2'b00

协议特别标明:发送端需要严格遵循此规则发送PDS,但是接收端需要检测至少满足上述条件中的两条,就表示收到了一个合法的PDS。

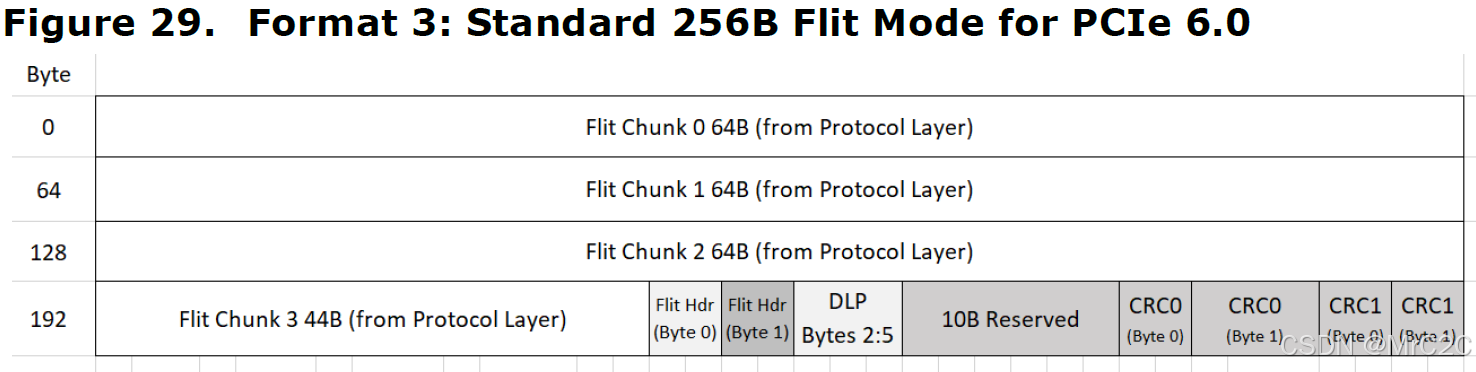

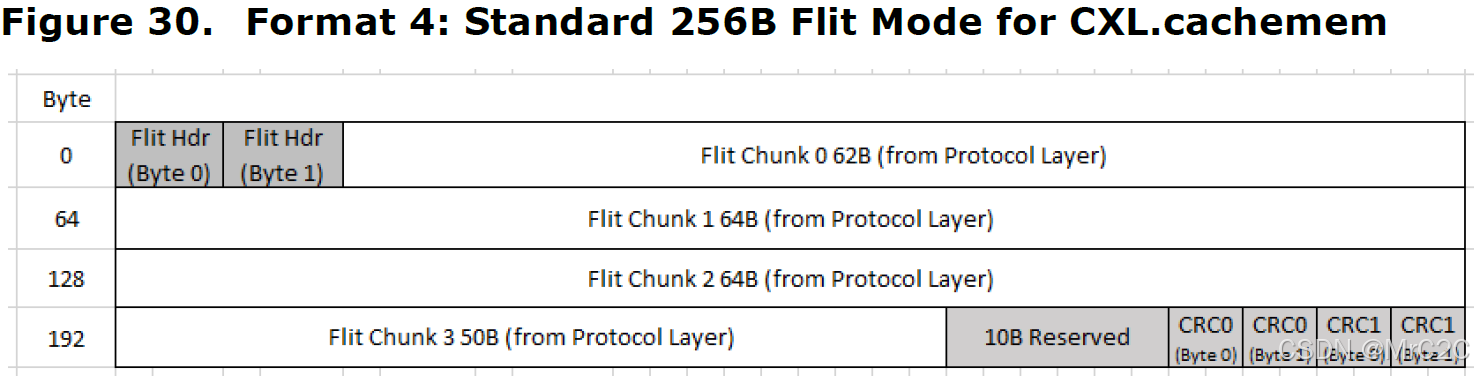

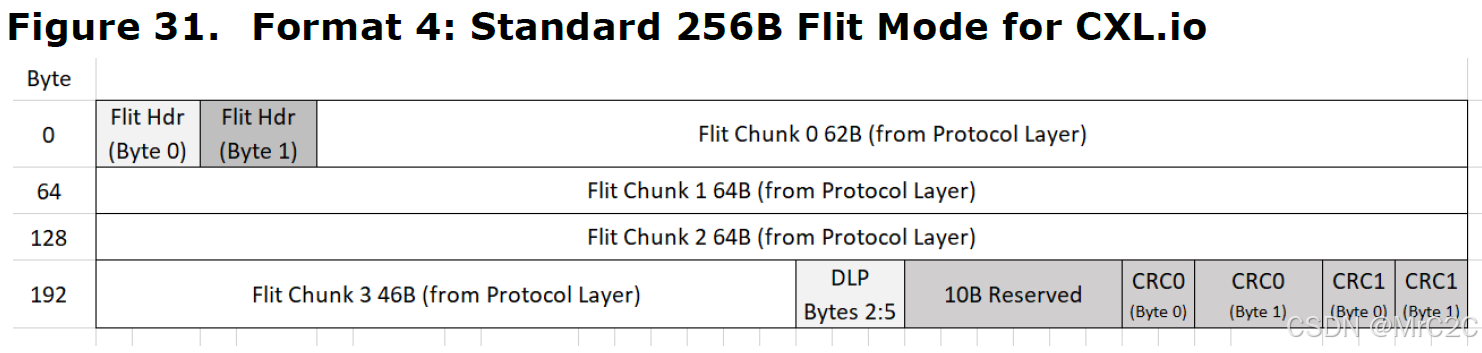

PCIe 6.0/CXL 256B Flit Mode

Adapter定义了3种Flit format,format3,4,5,分别如下图:

这3类Flit,分别针对PCIe, CXl.io和CXL.cachemem几类协议Flit。

这3类Flit,分别针对PCIe, CXl.io和CXL.cachemem几类协议Flit。

针对PCIe/CXl.io的TLP报文,正常按照64Bytes 切成flit chunk封装到adapter flit中,256Byte的flit最后包含(图29,31)的最后一行,用于封装PCIe/CXL.io的DLLP,UCIe 协议层和adapter之间的FDI接口提供了专门发送/接收DLLP的一组信号,发送端adapter负责将收到的DLLP插入到Flit的DLP byte 这个field中。接收端adapter负责将收到的DLP bytes恢复成DLLP并通过FDI接口发给协议层。

和64Byte的CRC一样,256B Flit也是每128Bytes计算一次CRC(2Bytes CRC),所以256B Flit在尾部有2组2Bytes CRC,分别代表FLIT的前128Bytes和后128Bytes的部分算出来的CRC。

针对PCIe: CRC0从Flit Chunk0到Chunk1, CRC1包含Flit Chunk2 和Chunk3,以及后面的Flit header和DLP bytes。攻击114Bytes,剩下的少于128byte的部分填0.

针对CXL: CRC0包含Flit的钱128Bytes,包含Flit Hdr0和1, Flit chunk0和Chunk1.CRC1包含Chunk2和chunk3和后续的DLP或者reserved的field,以及不够128Byte的部分用0来填充。

和68Byte flit要求一样,CRC的计算不依赖于是否enable Retry功能。UCIe 协议建议对于收到CRC校验错误的Flit,报告Uncorrectable Internal Error (UIE)

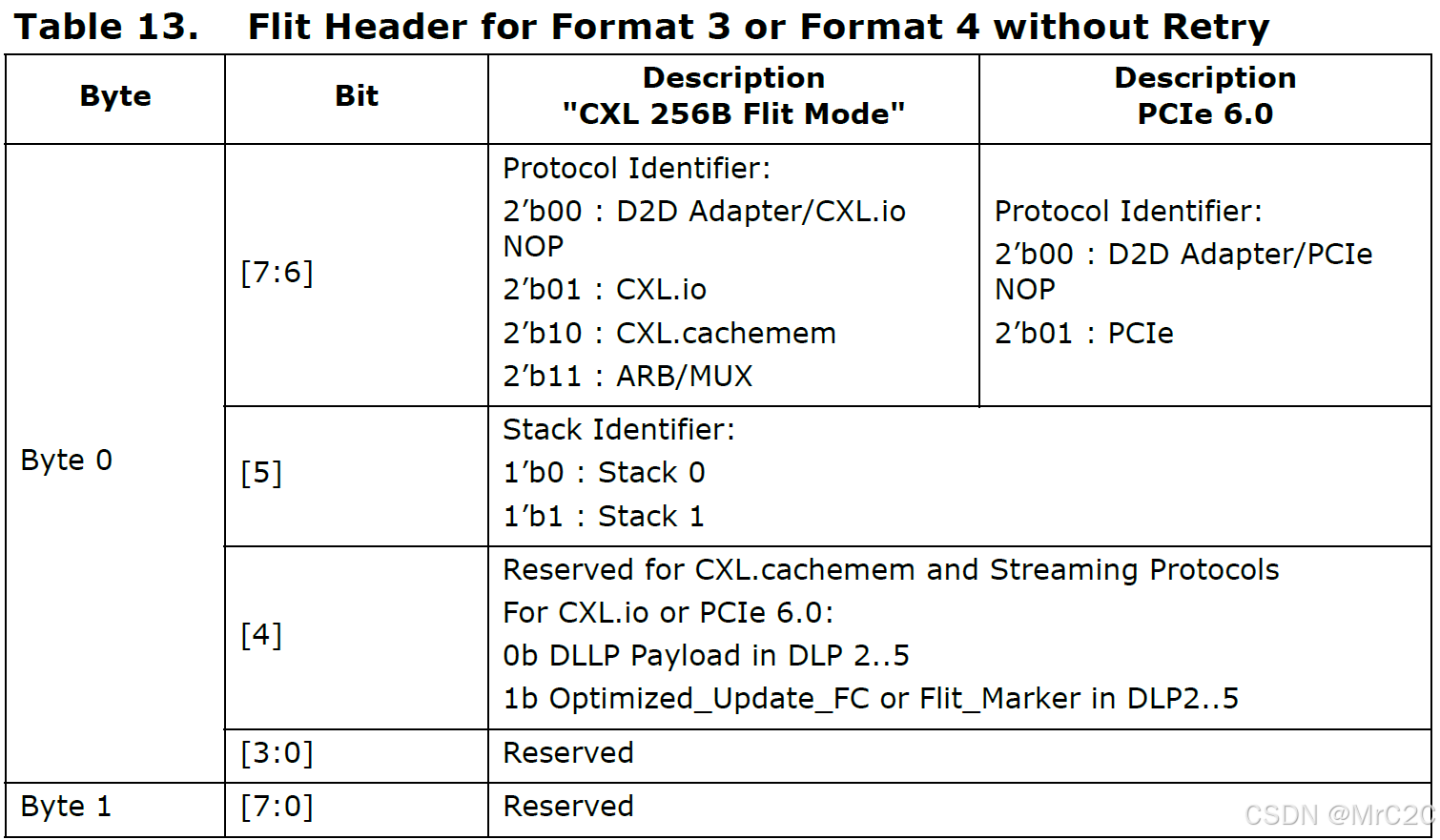

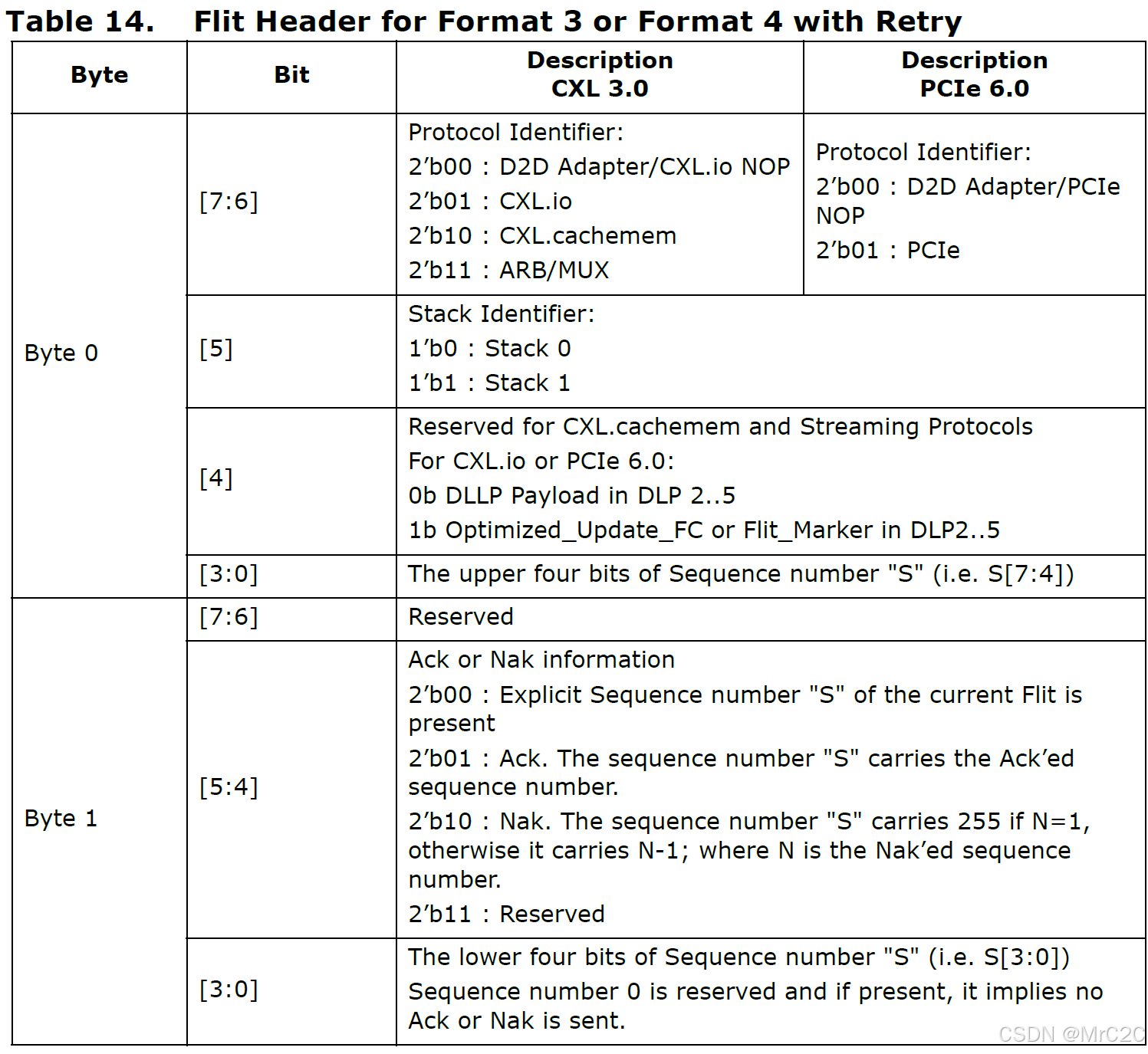

详细的Flit Header filed定义下面表格:

CXL 256B Flit with Latency Optimized

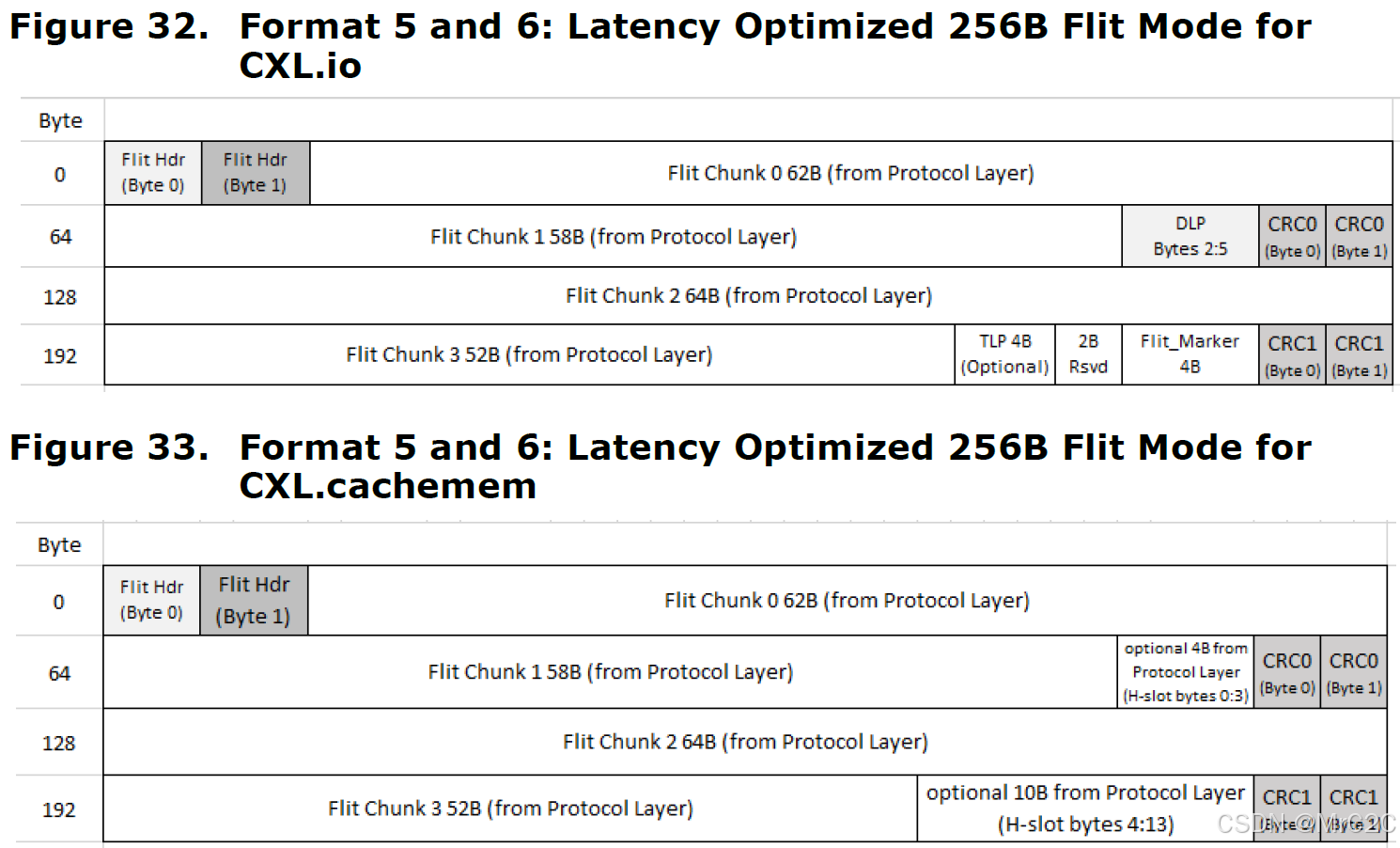

Adapter层定义了两种Latency Optimized Flit, Format 5, 6.见下图:

Latency Optimized Flit姑且称之为延迟优化Flit,其规则基本上和正常的CXL flit一致,区别在于上层传下的latency optimzied flit 填充了更多的optional 协议TLP/Flit bytes,另外CRC0 填充到Flit Chunk1和2中间了。其他规则和标准256B Flit保持一致。

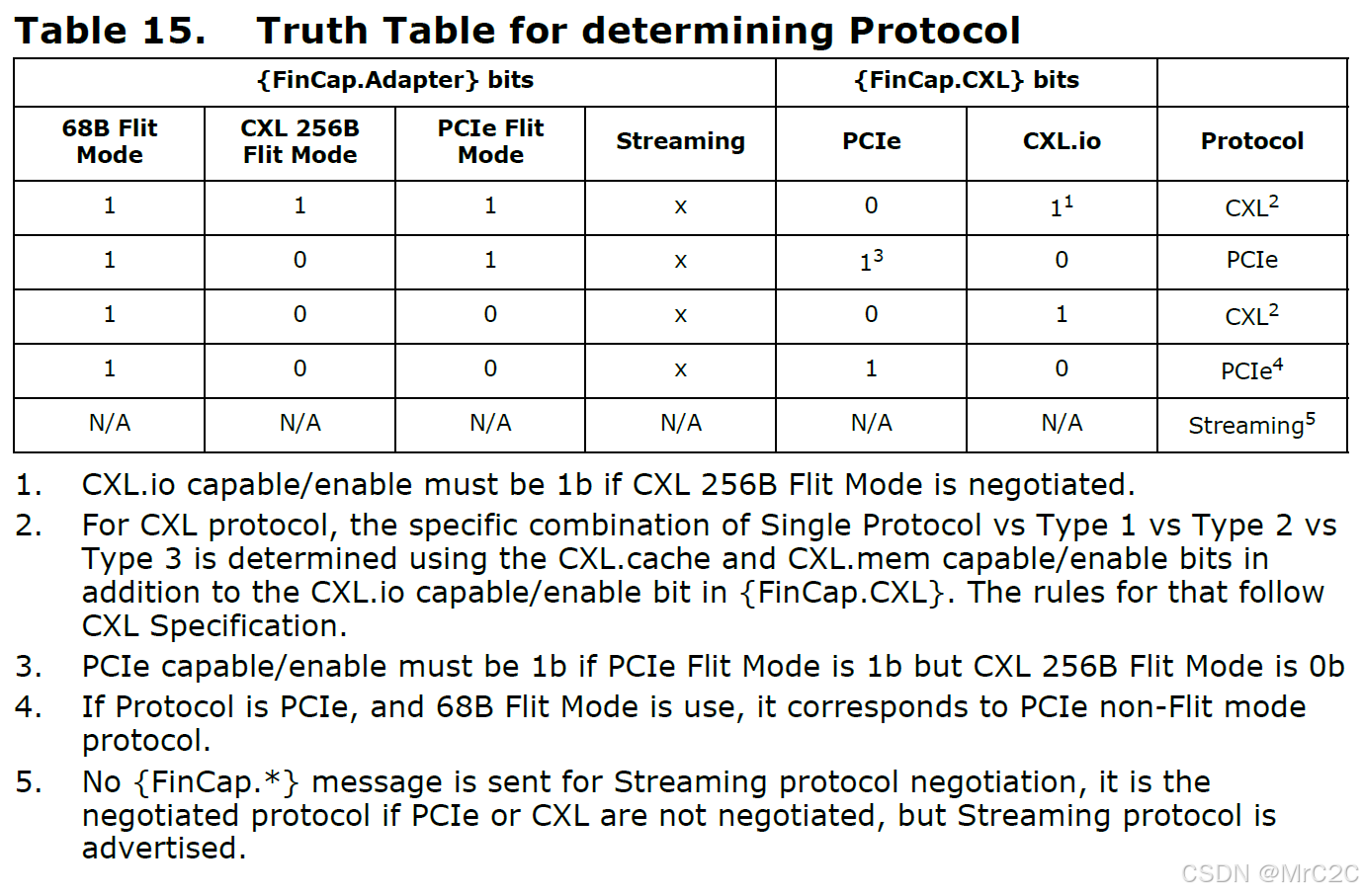

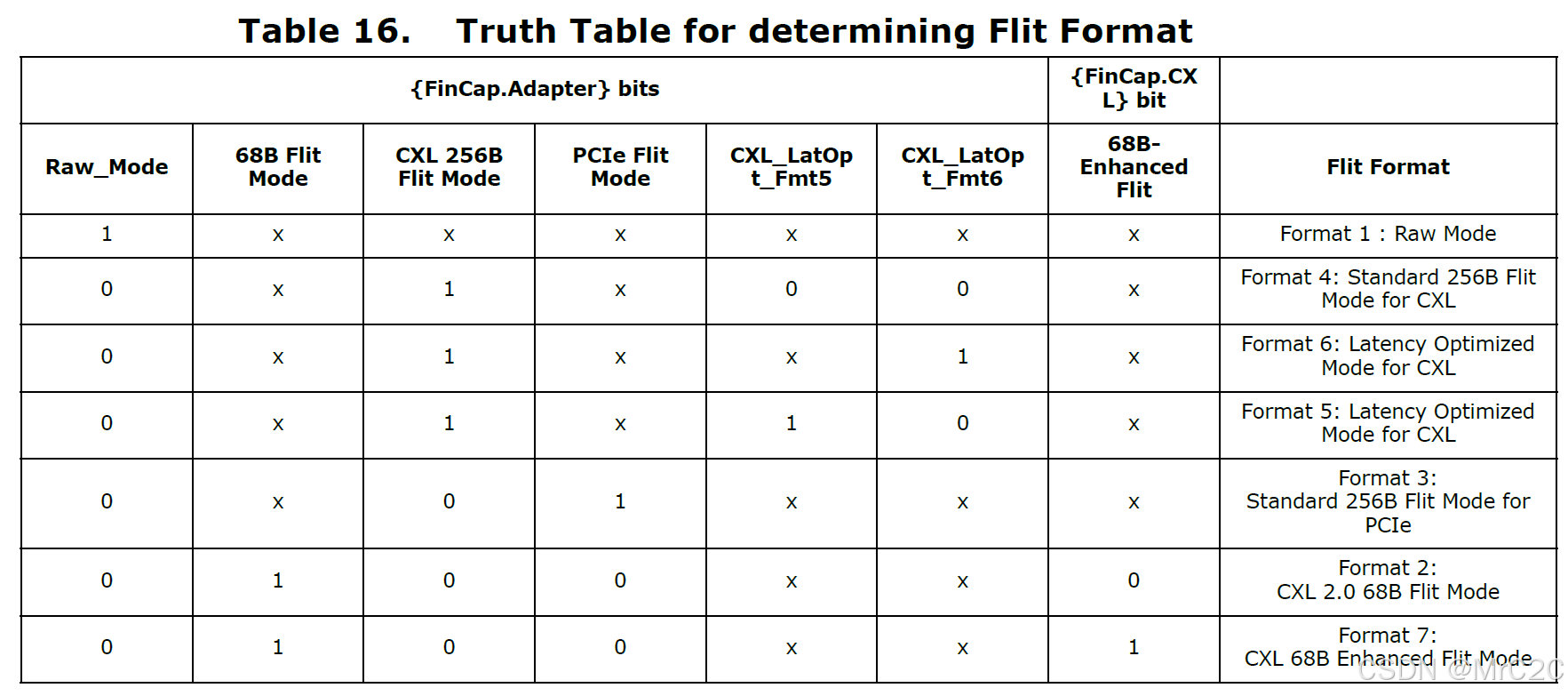

协议和Flit格式决策表

最后,贴上本章协议定义的protocol决策表和Flit format封装格式决策表:

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?