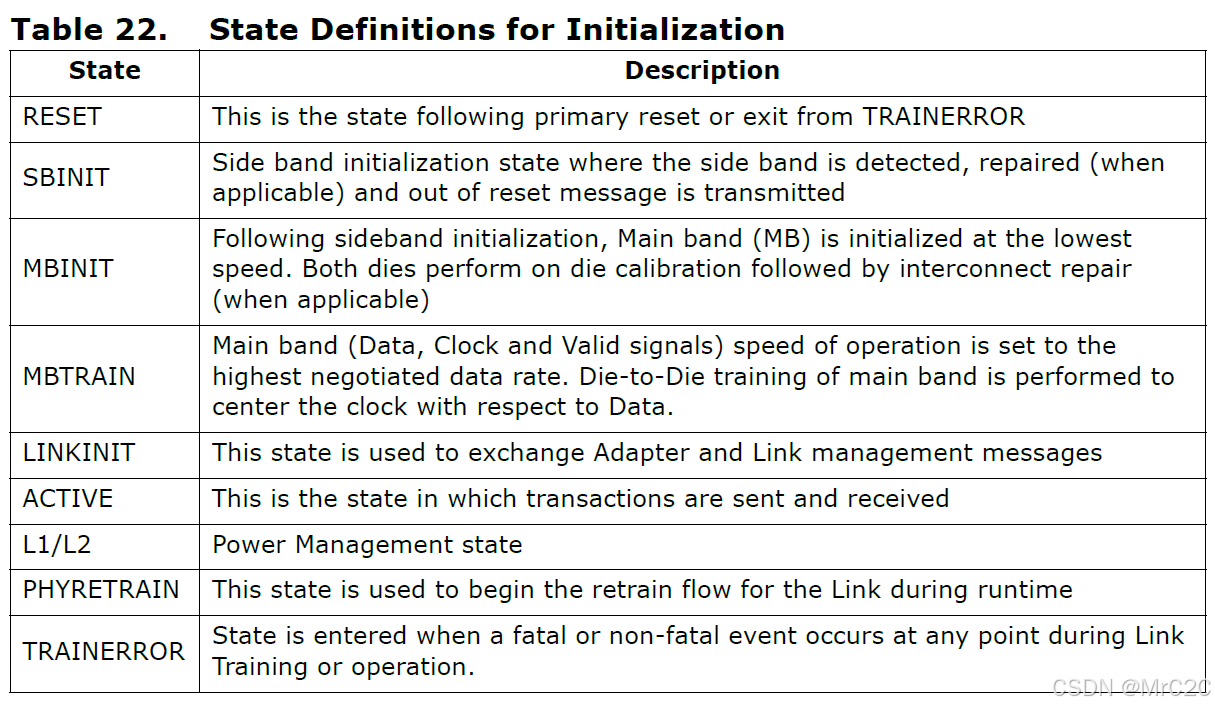

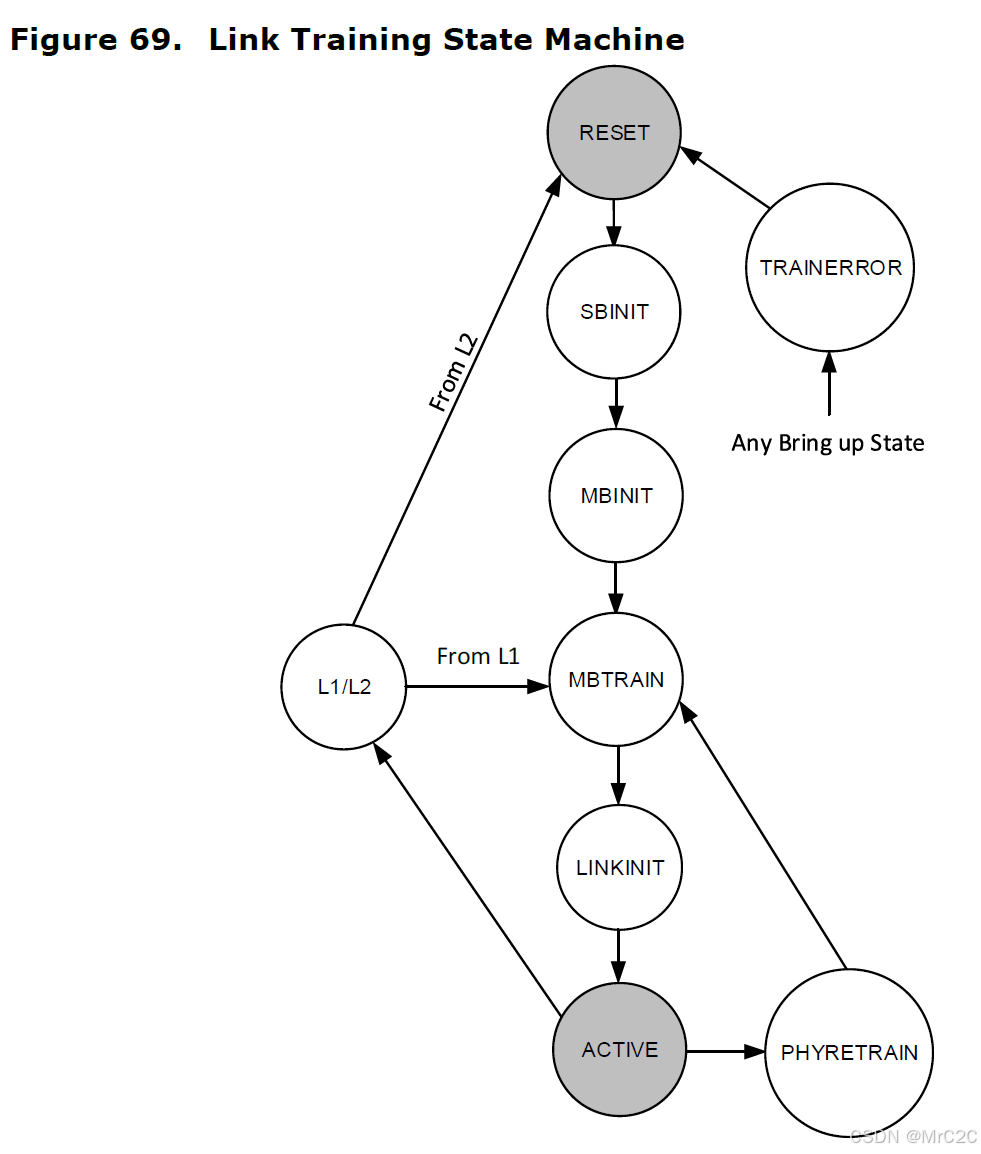

链路训练状态机(Link Training State Machine)

链路训练状态

链路训练状态转换图

链路状态说明:

RESET:

每次进入RESET状态后,PHY需要保持RESET状态至少4ms,保证PLL的stable。满足下面条件之一state可以推出RESET状态:

- Power supply stable。

- Sideband clock运行于800MHz。

- Mainband和die to die adapter clock稳定运行。

- Mainband时钟稳定运行在slow frequency (2GHz for 4GT/s)。

- Local SoC/Firmware未设置RESET状态。

- Link Training trigger开始training (trigger条件在本节开始有说明)。

SBINIT:

从复位状态进入SBINIT状态,SBINIT主要用于初始化sideband 通信通道,以及有必要的时候进行sideband repair。mainband信号处于3态或disable状态。SBINIT需要sideband clock运行于800MHz。

Advanced package同时要求SB clock和SB data各具备一条redundent冗余信号(CKSBRD和DATASBRD)。带repair的SBINIT sequence如下:

1. Repair CK/DATA pair: 由于带冗余的Sideband信号包含CKSB/DATASB和CKSBRD/DATASBRD两对,两两组合的话会有4种可能性。repair后可能组成4种CKSB<->DATASB成对的某一种。如:CKSB<->DATASB, CKSB <-> DATASBRD, CKSBRD <-> DATASB, CKSBRD <-> DATASBRD. 具体序列如下:

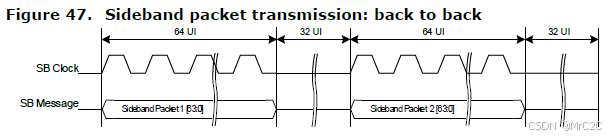

UCIe module (A)端Transmitter发起64个UI Clock的pattern和32 UI的低电平。同时以CKSB和CKSBRD为时钟和DATASB和DATASBRD上同时发起此pattern。

UCIe module (B)端Receiver端分别以CKSB和CKSBRD来采样DATASB和DATASBRD。注意,此处需要4个sample逻辑并行同时处理。CKSB为时钟采样DATASB;CKSB为时钟采样DATASBRD;CKSBRD为时钟采样DATASB;CKSBRD为时钟采样DATASBRD;

接收端(B),需要具备四个独立采样器采样数据并比较接收到的pattern为64个UI clock 和32个UI低电平。

接收端有任何一路比较器匹配到CK/DATA pair成功的检测到了pattern,发送端可以继续发送4轮64UI+32UI pattern后 停止发送pattern。并此后离开RESET状态,此后Receiver和transmitter可以开始互相发送sideband message。

如果接收端没有CK/Data pair检测到pattern,则UCIe module 继续发送pattern持续1ms,然后进入idle状态1ms,如此pattern 1ms+idle 1ms,循环4次,共计8ms结束后。发生timeout,链路状态进入TRAINERROR状态。

Note:接收端共计4中组合的CK/DATA pair的pattern比较器,会同时产生4bit的结果。[0]: DATASB/CKSB,[1]:DATASB/CKSBRD,[2]:DATASBRD/CKSB,[3]:DATASBRD/CKSBRD。

sideband信号最重采用哪一路的CK/DATA pair取决于下面的优先级比较器:

if result[0] { sideband = DATASB/CKSB;}

else if result[1] { sideband = DATASB/CKSBRD;break;}

else if result[2]: { sideband = DATASBRD/CKSB;break;}

else if result[3]: { sideband = DATASBRD/CKSBRD;break;}

2. sideband信号repair后,UCIe module开始发送和接收 sideband message。UCIe 发送端开始并持续发送「SBINIT Out of Reset」 sideband消息,知道接收端也同时接收到SBINIT Out of Reset message (表示对端已经接收到SBINIT消息,并发送out of reset消息)或者8ms timeout (对端即使没接收到SBINIT,本端也需要发送Out of Reset,实际上下个状态为TRAINERROR)。

3. 在「SBINIT Out of Reset」sideband message互相接收后,UCIe transmitter/receiver pair选择正确的CK/DATA pair(成为functional sideband pair)。

4. 在此之后任何的sideband message交互均在此选定的functional sideband pair上进行。

5. UCIe A端发送SBINIT done Req消息并等待response,B端接收此消息后发送SBINIT done resp消息回应。UCIe两端分别经历上述消息后,链路进入下一个状态:MBINIT状态。

标准封装的接口(standard package)并不要求CK/DATA的repair,不具备CKSBRD/DATASBRD。此类接口的SBINIT状态协商不具备CK/DATA repair pattern的协商,每一端的Tx用仅有的DATASB/CKSB pair发送64UI + 32UI (Low)的pattern,并持续发送等待timeout后进入TRAINERROR,或者如果对端正确接收到pattern,则进入RESET状态。其他状态转换规则和Advanced保持一致。

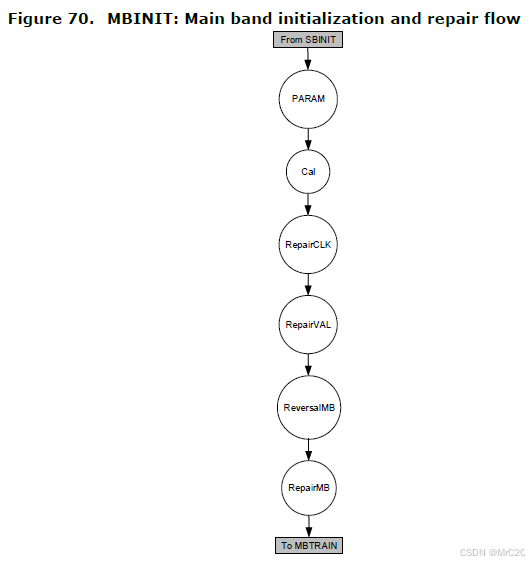

MBINIT:

MBINIT状态用来初始化,repair,或许还包含链路降规(降速或降位宽)main band接口。mainband接口的最低速度要求是4GT/s。

Advanced package的Mainband还需要支持repair功能。MBINIT的字状态需要支持data/clock/track/valid lanes的repair。Standard package不需要repair功能。

mainband的init和repair状态机和转换流程见下图:

MBINIT.PARAM

此状态用于链路两端的参数交互,包含最大链路速率,宽度等其他链路参数交互。包含:

1. Voltage Swing: Voltage swing参数由5bit组成,UCIe module在PARAM子状态发送此voltage swing参数给对端,对端receiver必须用此参数值(swing)和其接收端的termination info来设置其Reference voltage (Vref)参数。

2. Maximum Data Rate:4-bit max data rate,发送端将data rate 4-bit field随着MBINIT.PARAM configuration req消息发送,对端收到后,对比自己支持的max data rate,取较小的值(较低的速率),并设置较小值跟随MBINIT.param configuration resp 消息发送给transmitter端。

3. Clock Mode: 1-bit clock mode表示支持的时钟是strobe模式还是continuous模式。

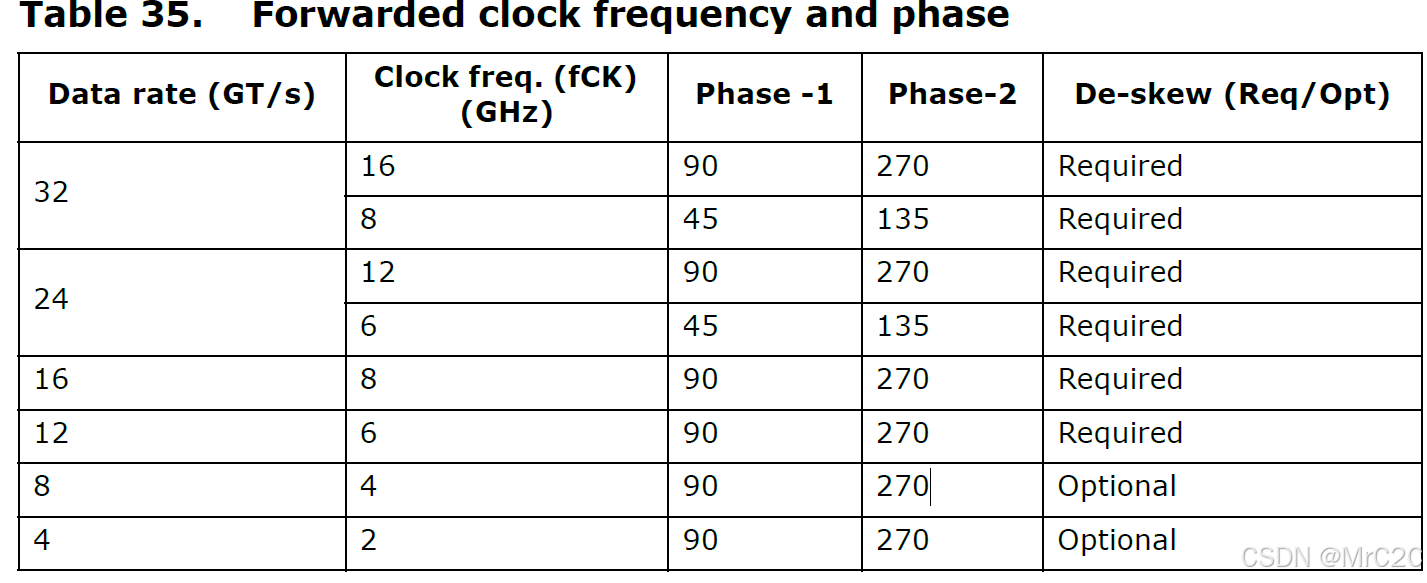

4. Clock Phase: 1-bit clock phase表示phase1或phase2如下表所示。不同的rate模式下此bit代表的相位度数如下表定义。

接收端反馈的「MBINIT.param configuration resp」内的此field的值取决于request的value和接收端是否支持。

5. Module ID: 用来在多module configuration场景下的module ID分配/协商,如Byte mapping,module 开关等。

MBINIT.Param的协商流程(这段描述简单,直接引用spec):

1. The UCIe Module sends sideband message {MBINIT.PARAM configuration req} to

exchange parameters with the UCIe Module Partner.

2. Once {MBINIT.PARAM configuration req} is received, the UCIe Module Partner

resolves and responds with {MBINIT.PARAM configuration resp} sideband message.

MBINIT.CAL

本状态进行链路两端的calibration(如:Tx Duty Cycle correction,Receiver offset和Vref calibration)。流程如下:

1. UCIe module tri-state TX pins. 并可以进行必要的rx/tx calibration。

2. calibration结束后发起{MBINIT.CAL Done req} sideband message并等待{MBINIT.CAL Done resp}来结束CAL状态,进入MBINIT.REPAIRCLK。

注:Calibration一般的是PHY本身的校准行为,链路状态机并不定义calibration本身怎么做,只会定义calibration的request和response协商的参数和cal本身行为开始和结束后转到下个状态等此类状态转换条件。

MBINIT.REPAIRCLK

从此子状态开始,进入mainband的REPAIR操作,顺序依次是CLK -> VALID -> Lane Reversal -> Mainband (DATA).

REPAIRCLK/VAL/DATA等具体repair的方式前面已经有描述,本节不再赘述。本节主要描述REPAIR状态机跳转的message交互和条件。

在REPAIRCLK状态,UCIe双方必须同时打开Transmitter和Receiver的clock,track 和redundent clock通道。其他通道(如valid/data)可以继续保持3态。

MBINIT.REPAIRVAL

MBINIT.REPAIRLMB

MBINIT.REVERSALMB

MBTRAIN:

LINKINIT:

ACTIVE:

PHYRETRAIN:

TRAINERROR:

L1/L2:

待续。。。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?