本章开始主要介绍UCIe协议第四章,物理层逻辑定义和规范。

如其他的通信协议一样,接口的物理层包含两个部分,逻辑子层和电气子层。其中逻辑层主要负责:

1.定义接口信号和时序

2. 定义发送端如何将上层数据分发到各个物理通道以及接收端如何把从各个通道收到的数据恢复成byte stream(Flit)。

3. Broken Lane的repair和remap。

4. 链路初始化,训练(training)和电源状态管理/切换。

5. 扰码Scrambling和training sequence的产生。

6. Lane Reversal和ID映射。

7. 宽度和速度协商和动态切换。

数据和sideband信号,时序定义及数据分配

Mainbaind数据分配和传输

UCIe接口信号分sideband和mainband,其中sideband主要用于链路初始化/训练和状态迁移,capatility等的消息协商。mainband主要用于传输上层protocol/FDI或者以上层的控制或data flit。

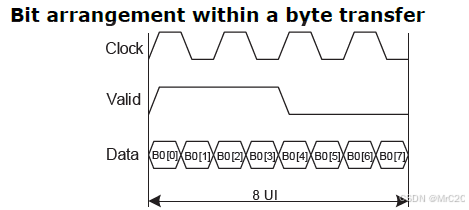

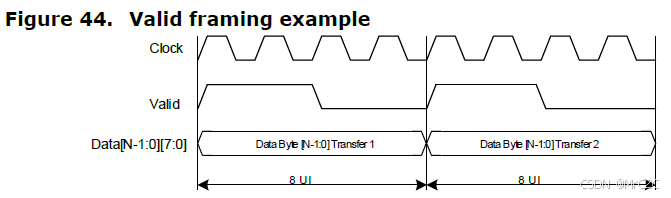

下图是mainband的传输信号和时序:

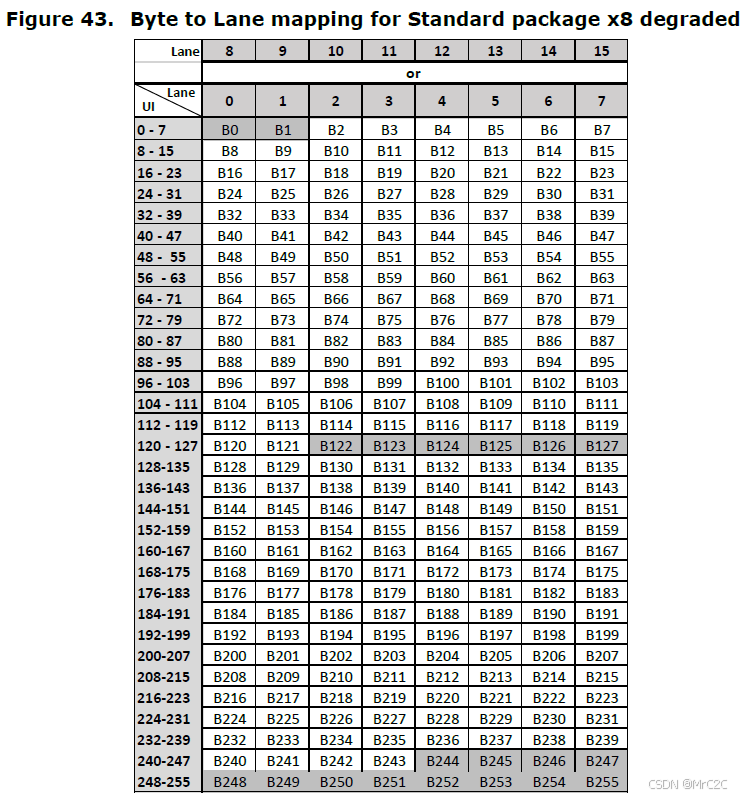

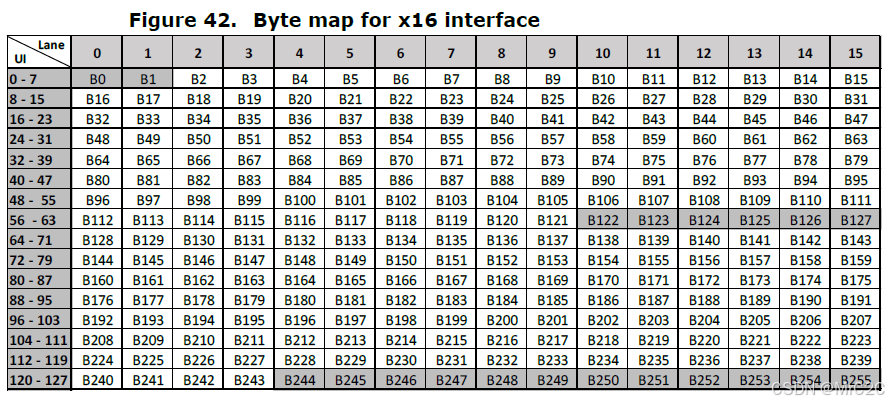

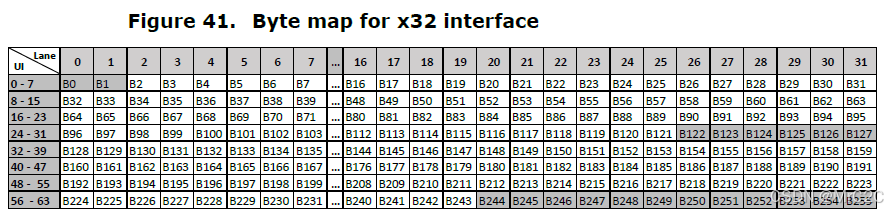

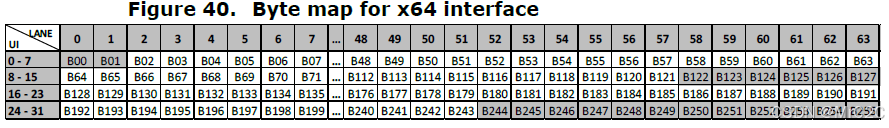

UCIe的capability,支持x16, x32, x64等等,甚至最低可以降级支持到x8 (协议称为Degraded模式),逻辑层从RDI接口收到FLIT的Bytes,并根据物理通道数(经过lane remapping数量),以及Lane Logic ID (remap 或者reversal之后的lane ID),把RDI数据分配到各个lane上发送出去。

分配方式见协议定义的几张图:

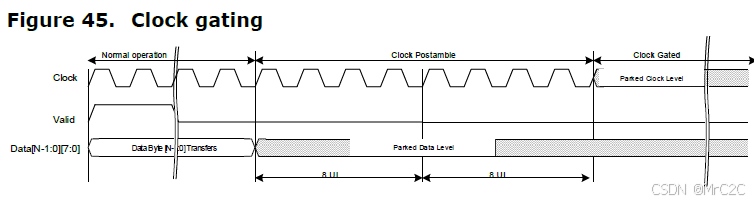

时钟门控

UCIe支持两种时钟模式,free running模式(时钟永远toggle,无论有无valid数据传输)和门控模式。门控时钟模式下,UCIe master在无数据传输时,继续发送16UI(8周期clock)之后,可以停止clock,见下面时序图:

sideband传输

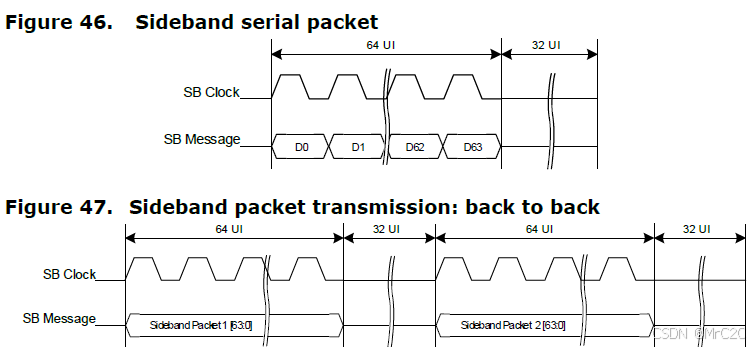

Sideband信号定义和时序见下图:

sideband信号由1bit的sb clock和1bit穿行的sb message,共计两pin。UCIe协议定义了两类Sideband Message。带data的message(128-bit)和不带data的message (64-bit)

按照上图,无论是发送带data 还是不带data的message, sideband 消息一次只发送64UI,即64bit数据,如果是64-bit message,则一次性发送完成。如果128-bit message,则需要按两次发送。UCIe协议规定在两次Sideband packet之间,至少间隔32UI (32-sb clock cycle)

Lane Reversal, Lane Remap, Repair

Lane Reversal/Remap协议往往是指实际的物理封装或者PCB上看到的PHY的PAD管脚,是有通道ID序号的,定义这种为Physical ID(物理ID)。这类lane 通道ID往往会为了PCB或者封装走线方便,实际在控制器内部由链路训练模块重新映射成逻辑通道(Logical ID)。协议定义了一些变量名(因为后续有算法描述映射关系,用缩略词方便表示)

TD_P/RD_P:物理(Physical) 数据(Data) 通道。T/R分别代表发送和接收。

TRD_P/RRD_P: 物理(Physical) 冗余(Redundant) 数据(Data) 通道。

TD_L/RD_L:逻辑(Logical) 数据(Data) 通道。

TCKP_P/TCKN_P/TTRK_P/RCKP_P/RCKN_P/RTRK_P: 第一个T/R代表发送或接受,CKP/CKN表示查分时钟clock_p/n端,最后的P表示物理通道。

TCKP_L/TCKN_L/TTRK_L/RCKP_L/RCKN_L/RTRK_L: 第一个T/R代表发送或接受,CKP/CKN表示查分时钟clock_p/n端,最后的L表示逻辑通道。

TRDCK_P/RRDCK_P/TRDCK_L/RRDCK_L: 时钟/Track 查分对的冗余信号(分别R接收,T发送)的P物理通道和L逻辑通道。

TVLD_P/RVLD_P/TVLD_L/RVLD_L:Valid信号(R接收,T发送)的P物理通道和L逻辑通道。

TRVLD_P/RRVLD_P/TRVLD_L/RRVLD_L:Valid冗余信号(R接收,T发送)的P物理通道和L逻辑通道。

Lane Reversal

协议规定UCIe device必须支持Lane reversal,Reversal是指LaneID顺序去反,即Die0的lane0可以连到Die1的Lane N-1, 例如16lane的情况下,连到Die1的Lane15)

| Die0.Lane0 | Die1.Lane15 |

| Die0.Lane1 | Die1.Lane14 |

| Die0.Lane2 | Die1.Lane13 |

| Die0.Lane3 | Die1.Lane12 |

| Die0.Lane4 | Die1.Lane11 |

| Die0.Lane5 | Die1.Lane10 |

| Die0.Lane6 | Die1.Lane9 |

| Die0.Lane7 | Die1.Lane8 |

| Die0.Lane8 | Die1.Lane7 |

| Die0.Lane9 | Die1.Lane6 |

| Die0.Lane10 | Die1.Lane5 |

| Die0.Lane11 | Die1.Lane4 |

| Die0.Lane12 | Die1.Lane3 |

| Die0.Lane13 | Die1.Lane2 |

| Die0.Lane14 | Die1.Lane1 |

| Die0.Lane15 | Die1.Lane0 |

其中:仅Data/Redundant lane可以被reverse,且仅有Transmitter需要做reversal。Track/Valid/Clock和sideband信号是不可以reverse的。

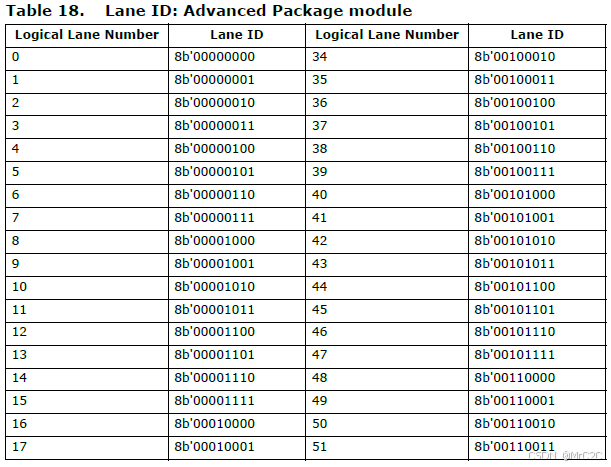

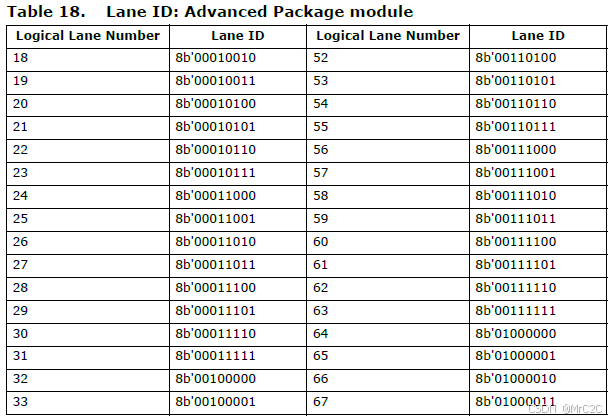

Lane ID:

数据通道Repair (Data Lane Repair)

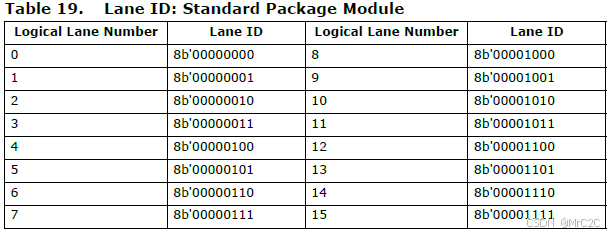

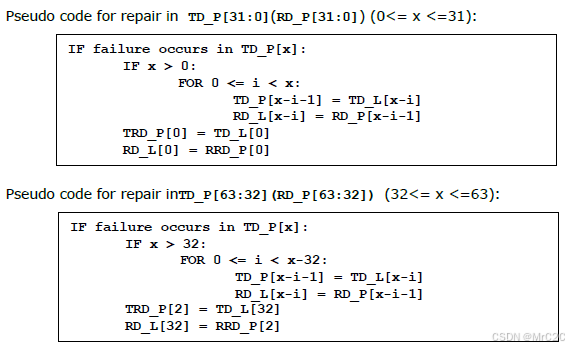

协议规范支持每个32 data lane(TD_P[31:0] 和TD_P[63:32]) 最多可以repair 2个 data lane。对应使用TRD/RRD_P[1:0]和TRD/RRD_P[3:2].

UCIe的repair是通过“shift left”或"shift right",左移或者右移的方式实现的lane remapping,进而实现repair。

shift的算法描述协议中定义如下:

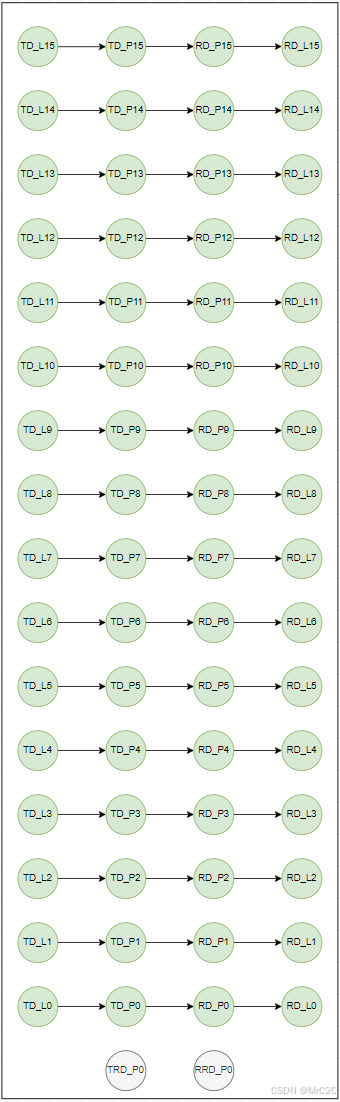

下图是我根据算法描述画的一个repair示意图,先画不需要repair的logic 到physical lane mapping示意图:

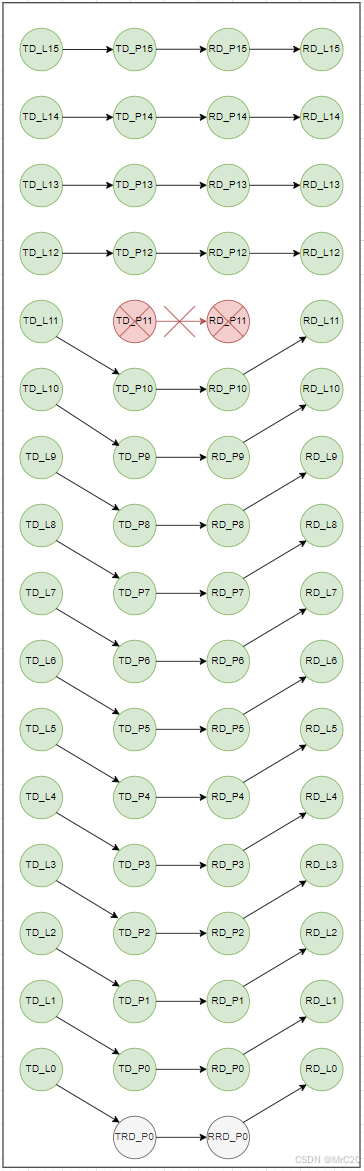

假设Physical Lane #11 坏了(单lane repair),不工作,那么logic lane remapping的方式如下图:

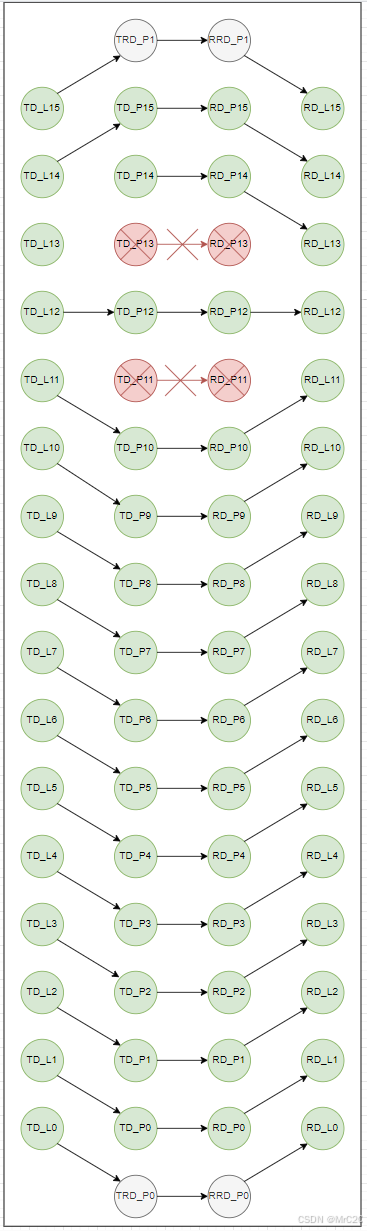

下图是双lane repair(假设了16 lane,也适用于32lane):

例子中距离了16lanes,对于小于等于32lanes的情况下,最多repair 2lanes,对于64lanes以下的,最多可以repair 4lanes。就是每32lanes,可以repair 2lanes。

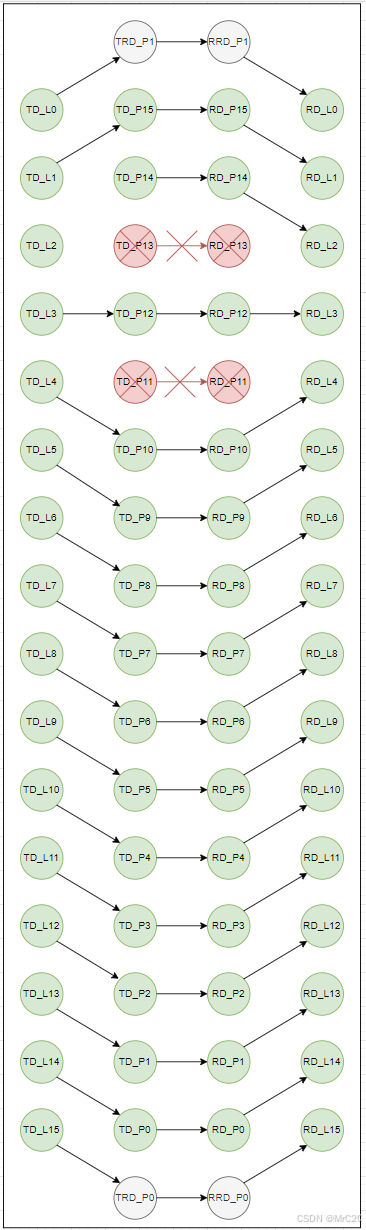

Lane repair(remapping)和lane reversal可以共同使用,其使用方式和没有reversal方式一致,只有logical lane ID排布反序了,见下图示例(2lanes repair):

Clock和Track Lane remapping

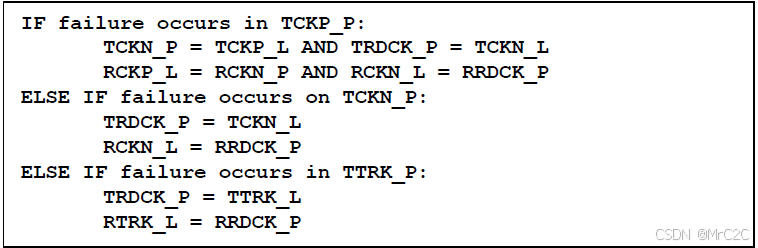

差分时钟和track 信号的repair伪代码:

比较直观的repair策略见下图:

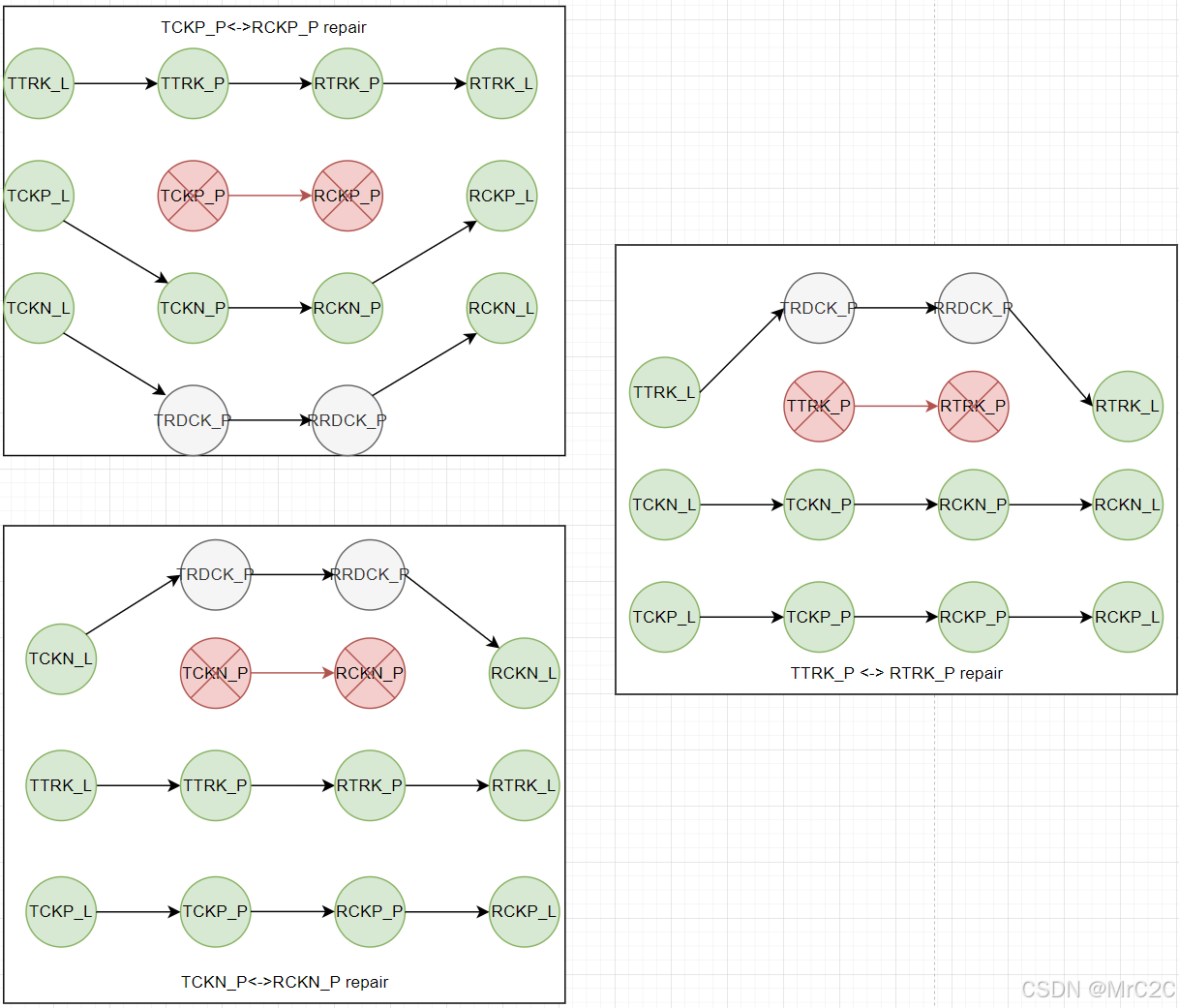

Valid Repair

由于Valid只有一个pin,并且冗余valid也只有一个pin,repair很直观,就是valid pin出break了的话,用redundancy path就好了。

宽度降低

协议定义的标准封装和高级封装中的宽度模式如x16, x32, x64, 在standard package的标准模式x16中,如果发生某个lane不工作,也不支持repair功能,或者repair的lane已经被用完,那么协议支持一种degrade模式,可以将链路宽度降低到x8模式,如果坏lane位于物理通道0-7,那么将物理通道8-15映射成逻辑通道0-7,如果坏lane位于物理通道8-15,则直接把0-7映射成逻辑通道0-7即可。如果是reveral的lane,那么lane id需要配合reversal机制反序。

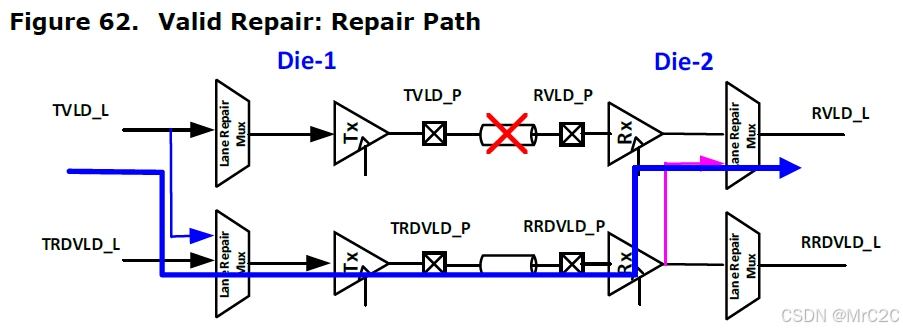

链路时钟数据训练和测试模式

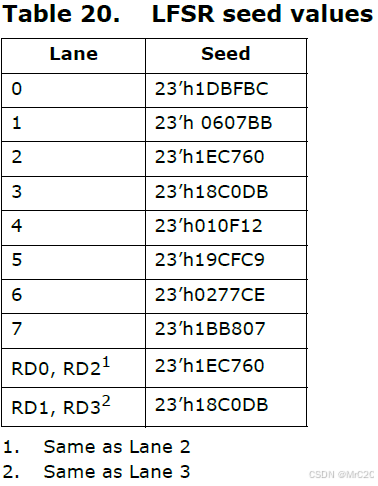

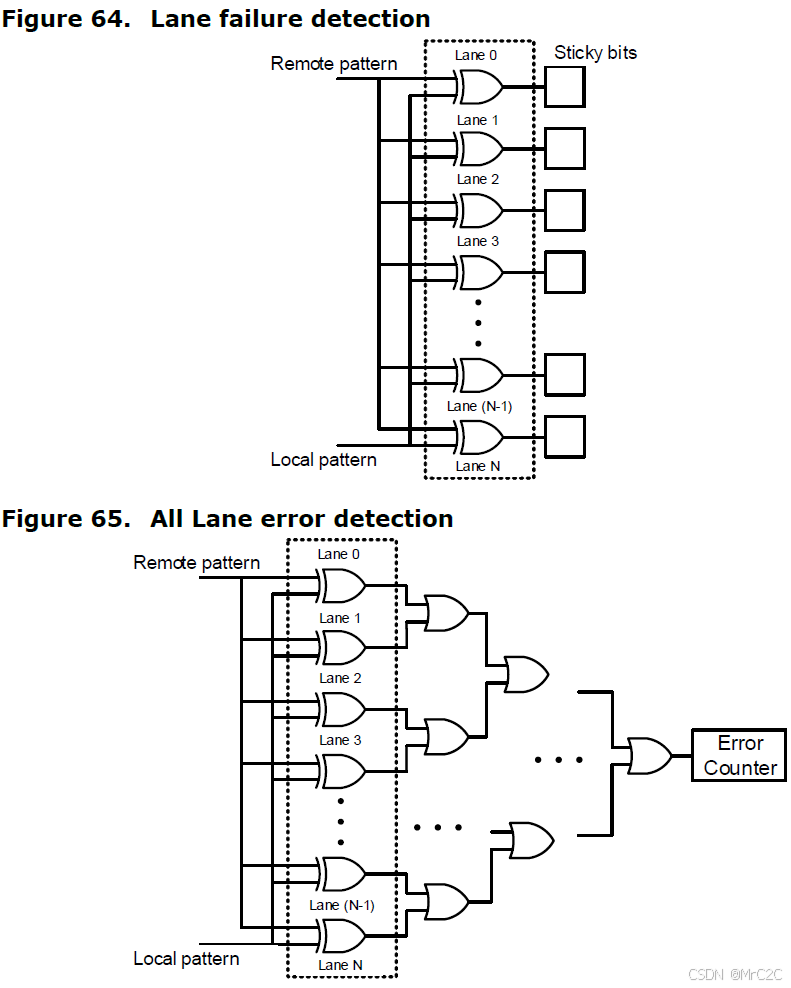

协议定义的链路测试采用PRBS23,其多项式为:G(x) = X23 + X21 + X16 + X8 + X5 + X2 + 1.链路pattern gen和check方式见下图:发送端产生pattern,并随着clock/valid输出到对端die的Rx链路,Rx per lane生成reference pattern并在收到对端发来的pattern后检查收到的和本地生成的reference pattern是否匹配。

每条lane使用的随机数种子见上图。

UCIe协议规定,每个lane产生的error状态需要寄存器记录并汇报(Sideband可读到)。所有lane的error需要ORed 到一个bit,并使用一个16-bit 计数器,用来计算整体链路的BER。

链路初始化和链路状态训练

下一章待续。。。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?