FPGA课程结课总结

前言

FPGA课程结束了,学习了20小时不到,但也学到好多东西,至少可以写写计数器,流水灯。为了让以后可能再次用到FPGA,还能记得一些东西,就以复盘大作业的形式记录遇到的问题。

大作业题目

可逆加减计数器设计

1、任务

可预置16位可逆加减计数器。要求计数器有16位计数输出同时有进位和借位输出,预置输入采用同步方式。

用FPGA开发板上的按键作为加减计数控制输入,数码管(或led)作为计数值输出。

2、目的

掌握自顶向下的全正向设计方法,掌握使用verilogHDL硬件描述语言进行硬件电路设计的方法,熟练使用Quartus II和Modelsim工具。

3、使用环境 (软件/硬件环境,设备等)

设计验证过程将使用以下的环境和工具进行:

1)、windows环境下使用ModelSim仿真工具进行逻辑仿真和时序仿真;

2)、windows环境下使用QuartusII工具进行设计综合。

4、设计方案

功能描述:

可预置加减计数器输入输出均为16位,计数范围为0~~ffffH,可实现加法和减法计数功能,并可以从预置数开始计数。

可预置加减计数器根据加法或减法信号来控制进行加法计数还是减法计数,并且从预置信号决定是否从预置数开始计数,若进行加法计算时,当计数器到ffffH时,进位信号输出为1,计数器从0开始计数;若进行减法计算时,当计数器到0时,借位信号输出为1,计数器从ffffH开始计数。

设计思路

题目要求自顶向下设计,确实需要这样做,不过在实际中比较混乱,刚开始的思路是先写计数器,在计数器的功能上添加按键消抖、数码管显示。

置数端的输入用两个按键开关控制,其余用电平控制,本来在32的板子上轻轻松松的事情在fpga板子就异常麻烦。最后这些东西都没有整,相对于4位计数器,不同的仅仅是它是16位的。

之后开始着手计数器设计,设计过之后,突然想到某次实验的例程与这个及其相似,所以就放弃之前的想法,直接吧我的设计的计数器用到之前的例程上去,不过要改好多代码,还要自己写仿真,不过就我这连半吊子都不算的水平着实比较难。

遇到的问题与注意事项

1.Verilog文件

1.一定要弄清reg和wire的区别

2…端口要对应

3.其它问题报错就直接找原因,找百度吧

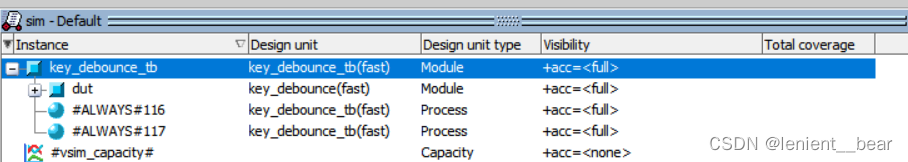

2.仿真文件

a.注意窗口,关掉的话在veiw里找

这个是schematic 这个里面可以往波形图加内部的线

b.

这个查看仿真报错信息

3. 其他

吐槽一下fpga如此底层的逻辑给写代码带来很不方便

以后想到再补充

最后感谢某位龚姓大佬

代码直接放链接了

菜鸡,写的不好,纯属为了应对大作业。

https://download.csdn.net/download/m0_52223807/85363952

不需要积分就能下载。

1033

1033

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?