专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

分析

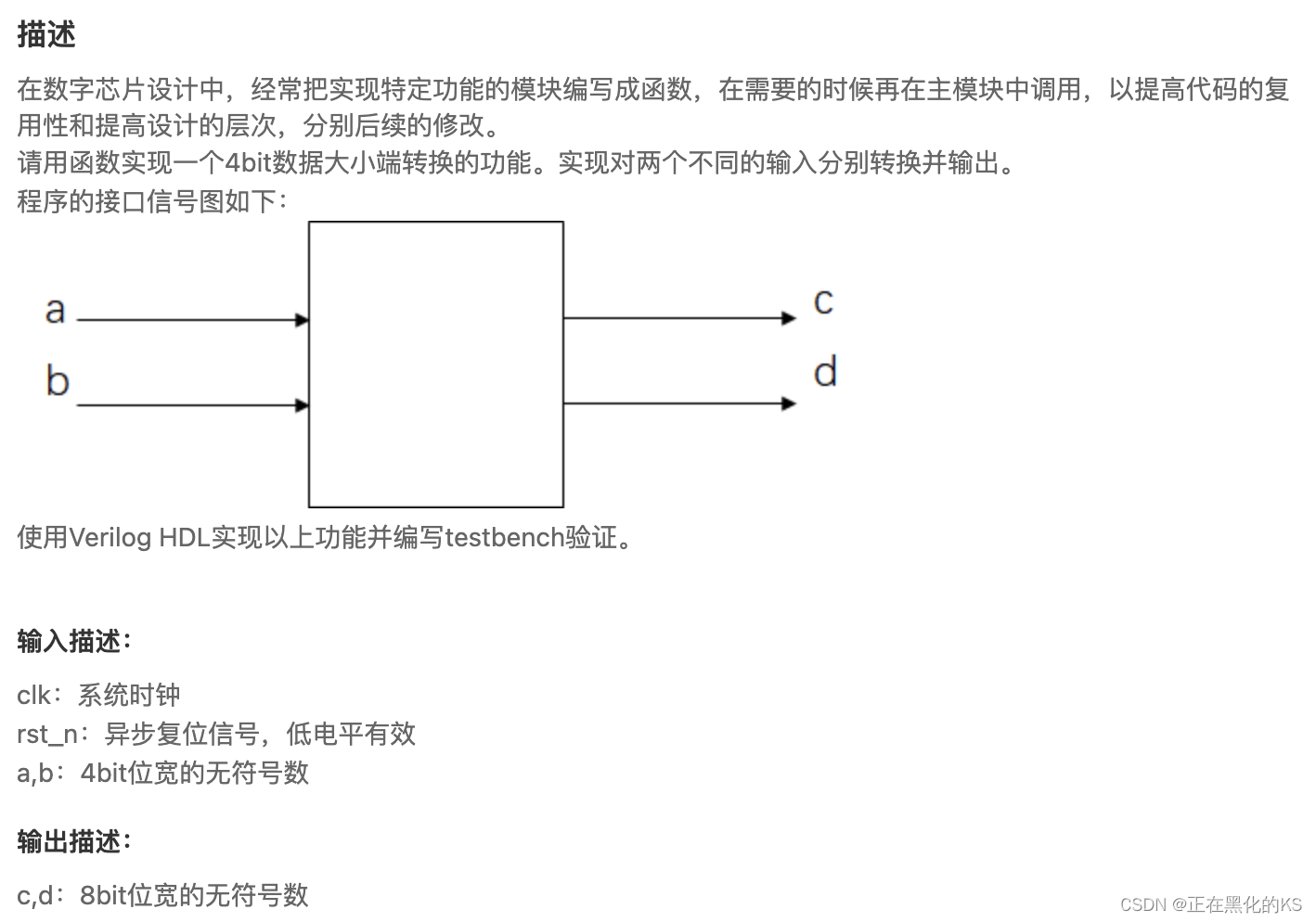

题目要求使用函数实现4bit数据大小端转换的功能,所谓大端,即数据的高位写在左侧,低位写在右侧。小端则反过来:高位写在右侧,低位写在左侧。实现N比特数的大小端转换,只需要把数据的N位赋值给0位,N-1位赋值给1位,依此类推。

在函数编写完成之后,实现对两个不同的输入分别转换,只需要调用两次函数,分别对两个输入进行转换即可。

在Verilog HDL中,函数的声明由关键字function开始,endfunction结束。对于函数中的语句需要用begin…end包含,即使只有一句。函数的声明模板如下:

function [range-1:0] function_name ; input_declaration ; other_declaration ; procedural_statement ; endfunction函数在声明时,会隐式的声明一个宽度为 range、 名字为 function_id 的寄存器变量,函数的返回值通过这个变量进行传递。当该寄存器变量没有指定位宽时,默认位宽为 1。然后进行输入变量的声明和其它声明。

函数通过指明函数名与输入变量进行调用。函数结束时,返回值被传递到调用处。

函数调用格式如下:

function_name(input1, input2, …);通过函数名调用函数,并在参数列表中填入输入参数。

要实现大小端转换,即将输入数值的最高位赋予输出的最低位,次高位赋予次低位,依次类推即可。

`timescale 1ns/1ns

module function_mod(

input [3:0]a,

input [3:0]b,

output [3:0]c,

output [3:0]d

);

assign c = data_out(a) ; // 默认wire类型 用assign赋值

assign d = data_out(b) ;

function [3:0] data_out ;

input [3:0] data_in ;

integer i ; // 不能使用parameter类型,因为该类型在整个程序中不能修改

begin

for (i = 0 ; i < 4 ; i = i + 1)

data_out[i] = data_in[3 - i] ;

end

endfunction

endmodule

5167

5167

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?