专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

`timescale 1ns/1ns

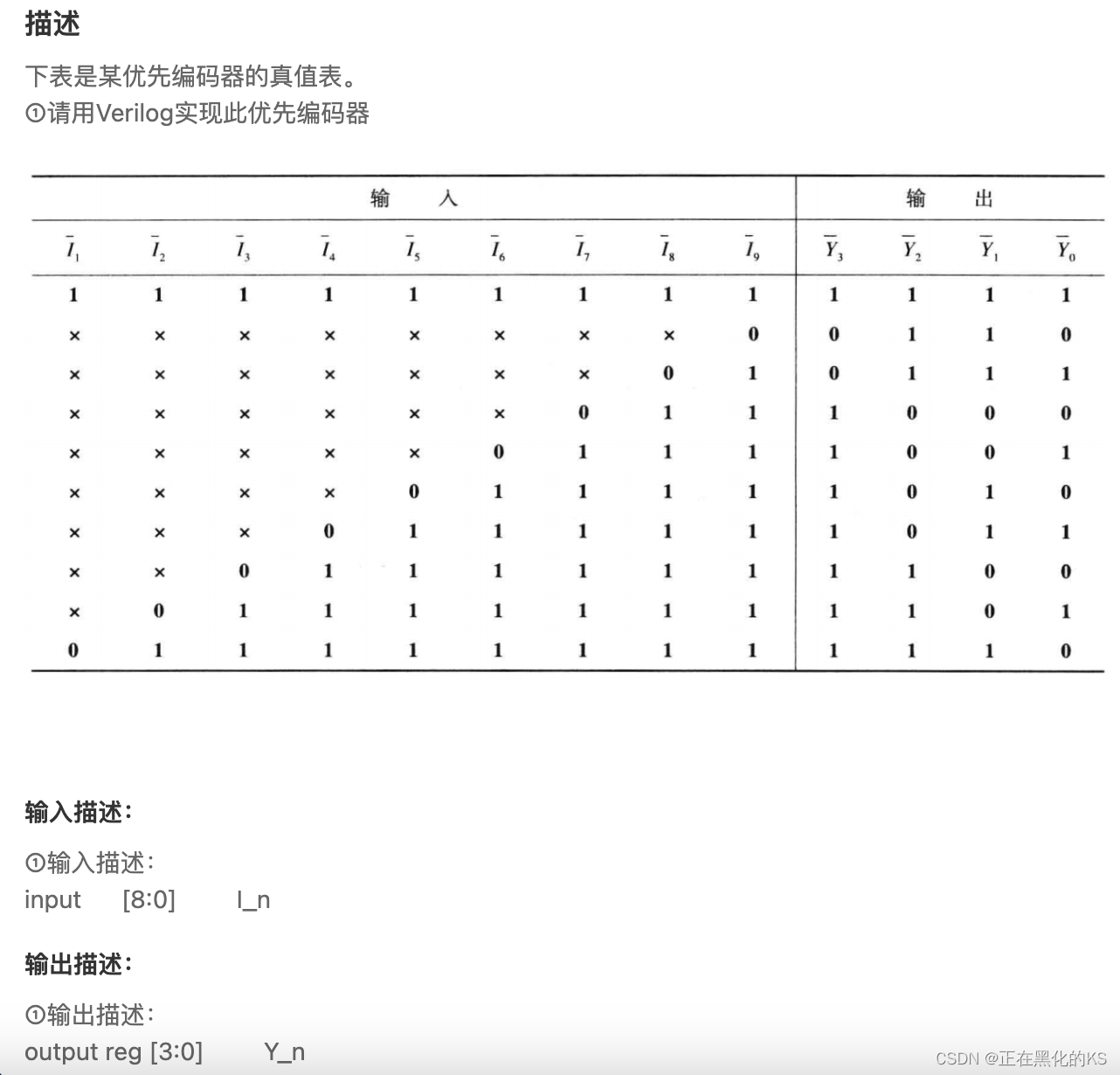

//优先编码器电路1

//电路的优先顺序是,从9到1,高级到低级

//9个输入端:I端,4个输出端:Y端,低电平有效。

//输入端从9到1有效输入,输出端从9到1进行输出

module encoder_0(

input [8:0] I_n ,

output reg [3:0] Y_n

);

always @ (*) begin

casez(I_n) //casez语句用来处理不考虑高阻值z的比较过程,即状态z在case语句中不会被视为正常的z状态

9'b1_1111_1111: Y_n = 4'b1111 ;

9'b0_????_????: Y_n = 4'b0110 ; //其中?,被视为高阻状态,casez中视为不必考虑的状态

9'b1_0???_????: Y_n = 4'b0111 ;

9'b1_10??_????: Y_n = 4'b1000 ;

9'b1_110?_????: Y_n = 4'b1001 ;

9'b1_1110_????: Y_n = 4'b1010 ;

9'b1_1111_0???: Y_n = 4'b1011 ;

9'b1_1111_10??: Y_n = 4'b1100 ;

9'b1_1111_110?: Y_n = 4'b1101 ;

9'b1_1111_1110: Y_n = 4'b1110 ;

default: Y_n = 4'b0000 ;

endcase

end

endmodule

5539

5539

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?