描述

下表是某优先编码器的真值表。

①请用Verilog实现此优先编码器

输入描述

①输入描述:

input [8:0] I_n

输出描述

①输出描述:

output reg [3:0] Y_n

解题分析

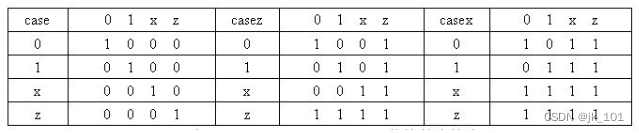

本优先编码器,可采用case语句实现,注意到真值表中,出现了x状态,所以考虑采用casex语句实现。casex语句的真值表如下:

由真值表可以看出,当选择端是x时,输入端是任何状态,输出都将是1.

根据优先编码器真值表,可写出如下Verilog:

always @(*)begin

casex(I_n)

9'b111111111 : Y_n = 4'b1111;

9'b0xxxxxxxx : Y_n = 4'b0110;

9'b10xxxxxxx : Y_n = 4'b0111;

9'b110xxxxxx : Y_n = 4'b1000;

9'b1110xxxxx : Y_n = 4'b1001;

9'b11110xxxx : Y_n = 4'b1010;

9'b111110xxx : Y_n = 4'b1011;

9'b1111110xx : Y_n = 4'b1100;

9'b11111110x : Y_n = 4'b1101;

9'b111111110 : Y_n = 4'b1110;

default : Y_n = 4'b1111;

endcase

end参考代码

方法一:

`timescale 1ns/1ns

module encoder_0(

input [8:0] I_n ,

output reg [3:0] Y_n

);

always @(*)begin

casex(I_n)

9'b111111111 : Y_n = 4'b1111;

9'b0xxxxxxxx : Y_n = 4'b0110;

9'b10xxxxxxx : Y_n = 4'b0111;

9'b110xxxxxx : Y_n = 4'b1000;

9'b1110xxxxx : Y_n = 4'b1001;

9'b11110xxxx : Y_n = 4'b1010;

9'b111110xxx : Y_n = 4'b1011;

9'b1111110xx : Y_n = 4'b1100;

9'b11111110x : Y_n = 4'b1101;

9'b111111110 : Y_n = 4'b1110;

default : Y_n = 4'b1111;

endcase

end

endmodule方法二:

`timescale 1ns/1ns

module encoder_0(

input [8:0] I_n ,

output reg [3:0] Y_n

);

always@(*) begin

casez (I_n)

9'b1_1111_1111: Y_n = 4'b1111;

9'b0_????_????: Y_n = 4'b0110;

9'b1_0???_????: Y_n = 4'b0111;

9'b1_10??_????: Y_n = 4'b1000;

9'b1_110?_????: Y_n = 4'b1001;

9'b1_1110_????: Y_n = 4'b1010;

9'b1_1111_0???: Y_n = 4'b1011;

9'b1_1111_10??: Y_n = 4'b1100;

9'b1_1111_110?: Y_n = 4'b1101;

9'b1_1111_1110: Y_n = 4'b1110;

default: Y_n = 4'b0000;

endcase

end

endmodule注:题目分析来源网友,如有侵权请告删之。

1227

1227

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?