问题:

一个stackup 为8层2阶 的PCB板,设计检查DRC时,出现盲埋孔1-3与6-8 间距过近的DRC提示,

具体报错如下:

{

Constraint: Minimum Blind/Buried Via Gap

Constraint Set: DEFAULT

Constraint Type: NET SPACING CONSTRAINTS

}

原因:

Allegro 针对 Minimum Blind/Buried Via Gap 的检查,默认对所有层的孔都会进行检查,所以即使两个孔在Z向空间相距甚远,在XY投影平面距离过近也会上报DRC,而此设计不影响加工制作。

故,可将此类DRC提示关闭;

解决方案:

个人在设计中选择方案二:

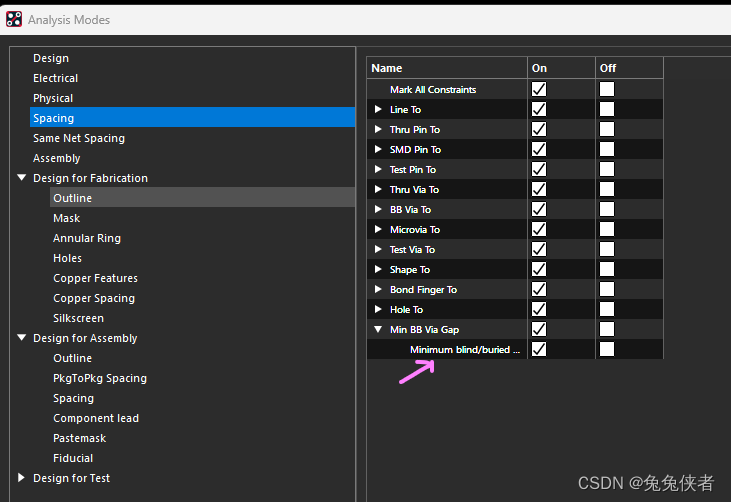

在菜单栏中选择 Setup/constrains/modes, 打开Analysis Modes 对话框:

方法一:可以直接将途中Min BB via Gap 提示关闭;

方法二:修改下图中 BB via layer seperation 的值:

该名词定义如下:

在8层2阶PCB设计中遇到Allegro DRC报错,指出盲埋孔1-3与6-8间距不足。DRC检查默认对所有层孔进行,即使实际不影响加工。关闭相关约束或调整BB Via layer separation值可解决此问题。验证表明,两种解决方案均有效。

在8层2阶PCB设计中遇到Allegro DRC报错,指出盲埋孔1-3与6-8间距不足。DRC检查默认对所有层孔进行,即使实际不影响加工。关闭相关约束或调整BB Via layer separation值可解决此问题。验证表明,两种解决方案均有效。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5211

5211

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?