目录

1.1历史回顾

1.2数字集成电路设计中的问题

1、时钟对系统设计的挑战

2、电源分布网络对系统设计的挑战

1.3数字设计的质量评价

1.3.1集成电路的成本

暂略

1.3.2功能性和稳定性

1、数字系统中的大多数噪声都是内部产生的,噪声的值与信号的摆幅成正比。电容和电感间的串扰以及内部产生的电源噪声就是这样的例子。一些噪声源来自系统之外,它们的值与信号电平无关。

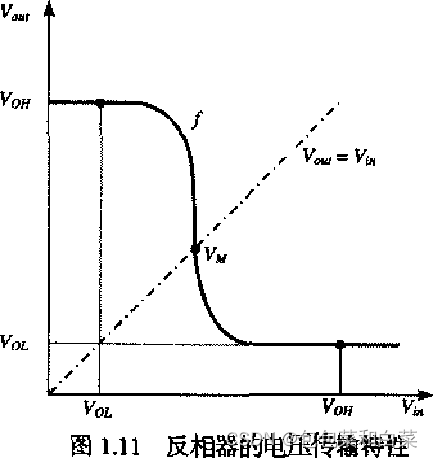

2、电压传输特性VTC:

VTC上另一个重要的特征点是门阈值电压或开关阈值电压VM,它定义为VM=f(VM)

3、信号逻辑摆幅Vsw

4、:最高低电平,

:最低高电平

5、不确定区(过滤区宽度:Transition Width)

6、高电平噪声容限 ;低电平噪声容限

7、再生性:

要具有再生性,一个门的VTC应当具有一个增益绝对值大于1的过渡区(即不确定区), 该过渡区以两个合法的区域为界,合法区域的增益应当小于1,这样的一个门具有两个稳定的工作点。这就清楚地定义了构成合法区和过渡区边界的VIH和VIL的电平。

8、方向性:

一个门的方向性要求它是单向的。就是一个输出电平的变化不应当出现在同一电路的任何一个未改变的输入上,否则输出信号的翻转就会作为噪声信号反射到这个门的输入上,从而影响信号的完整性。

9、扇入和扇出

扇出表示连接到驱动门输出端的负载门的数目N。增加一个门的扇出会影响它逻辑输出电平。

一个门的扇入定义为该门输入的数目。扇入较大的门往往比较复杂,这常常会使静态和动态特性变差。

1.3.3性能

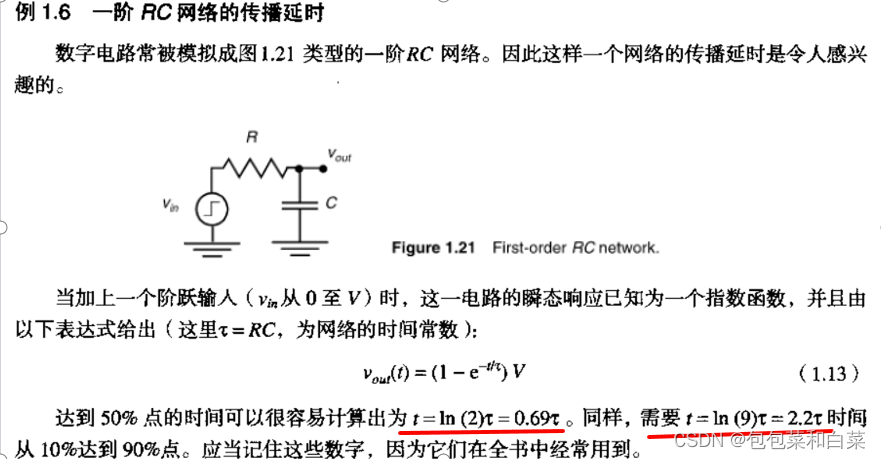

1、延时

传播延时不仅与电路工艺和拓扑连接有关,还取决于其他因素。最重要的是延时与门的输入输岀信号斜率有关。为了定量这些特性,我们引入了上升时间tr和下降时间和tf,它们是用来衡量单个信号波形而不是针对门的,并且它们表明了信号在不同电平间的翻转有多快。为了避免无法确定一个翻转实际开始和结束的时间,把上升和下降时间定义为在波形的10%和 90%点之间。一个信号的上升/下降时间很大程度上取决于驱动门的强度以及它所承受的负载。

2、环振

用来度量延时的标准电路是环振;它是由奇数个反相器连成的环状链构成的。

1.3.4功耗和能耗

1、

静态功耗:静态功耗即使在没有发生开关时也存在,并且是由在电源和地之间 的静态导电通路或由于漏电流引起的。它总是存在,甚至当电路在等待状态时也存在。使这一功耗来源最小是一个十分重要的目标。

动态功耗:只发生在门开关的瞬间。这是由于对电容充电以及在电源和地之间有一暂时的电流通路造成的,因此它正比于开关频率:发生开关的次数越多,动态功耗越大。

2、

功耗---延时积(power -delay product :PDP):表示一个门一个开关事件所消耗的能量,它可以作为一个开关器件性能的度量。 一个理想门应当快速而且不消耗能量。

能量-延时积(the energy-delay product:E-D)就是把这两个因素放在一起考虑的复合指标,它经常作为最后的质量评价。E-D相当于功耗-延时2.

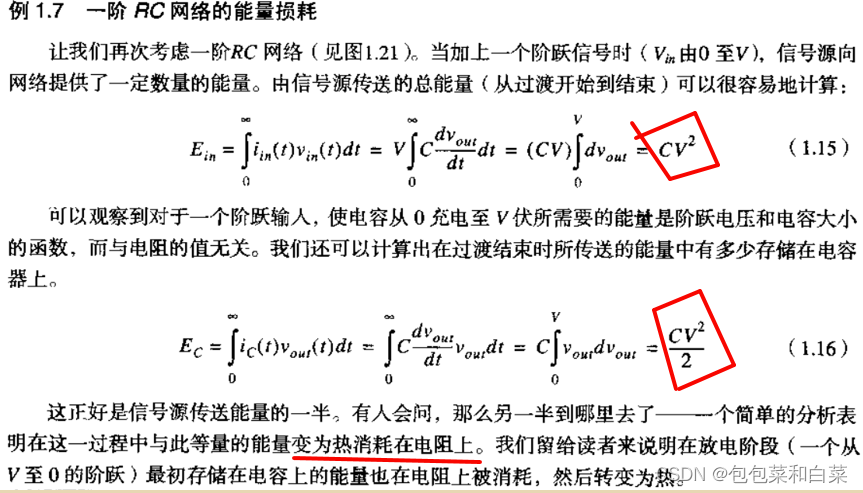

3、RC充放电功耗

1.4小结

1.5进一步探讨

1、有源区上做器件,有源区之外的场区作器件隔离。

2、如何解决同步时钟带来的问题呢?现在主要的技术趋势就是片上网络。

3、半导体工艺制程中的7nm、5nm究竟指的栅极宽度,即沟道长度。

4、工艺越先进,线与线的电容耦合越严重,如下图:

当达到65nm工艺时,电容串扰噪声成为一个重要挑战,65nm工艺的成熟标志是解决此问题:引入低k介质;

2507

2507

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?