目录

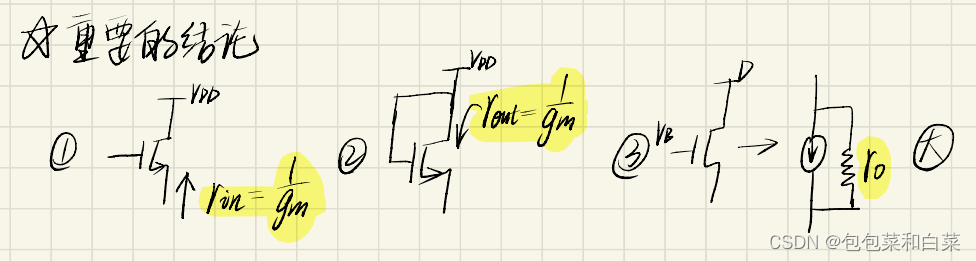

MOS管从三个端口看进去的电阻不同:

圈1中忽略了gmb。

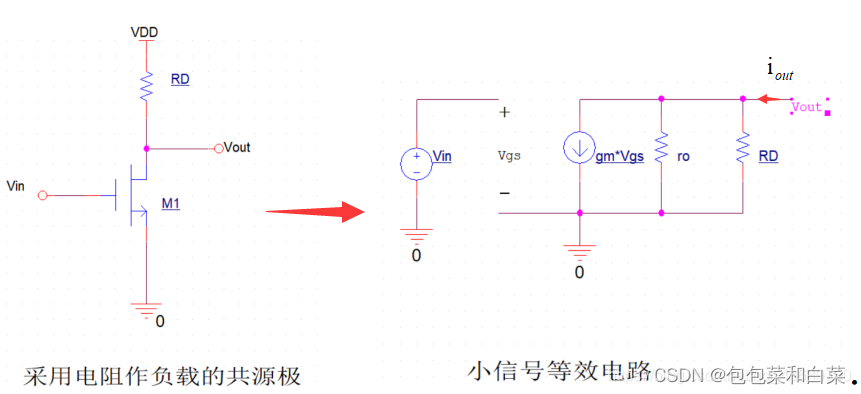

电阻做负载的共源极:

对于M1,从输出看进MOS,漏极看进去的电阻为 ro 。

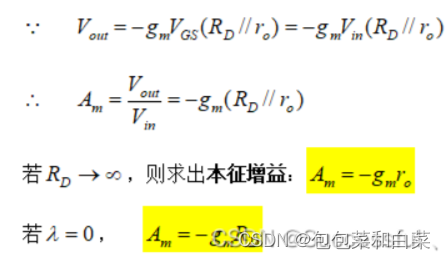

二极管做负载的共源极:

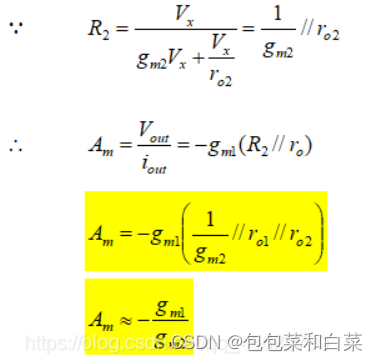

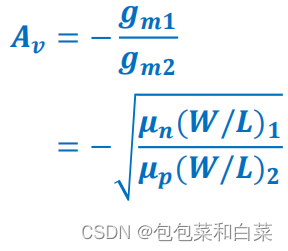

PMOS做二极管负载(负载mos无体效应):

对于M2,从Vout看进去的等效电阻为 ,

对于M1,从Vout看进去的等效电阻为

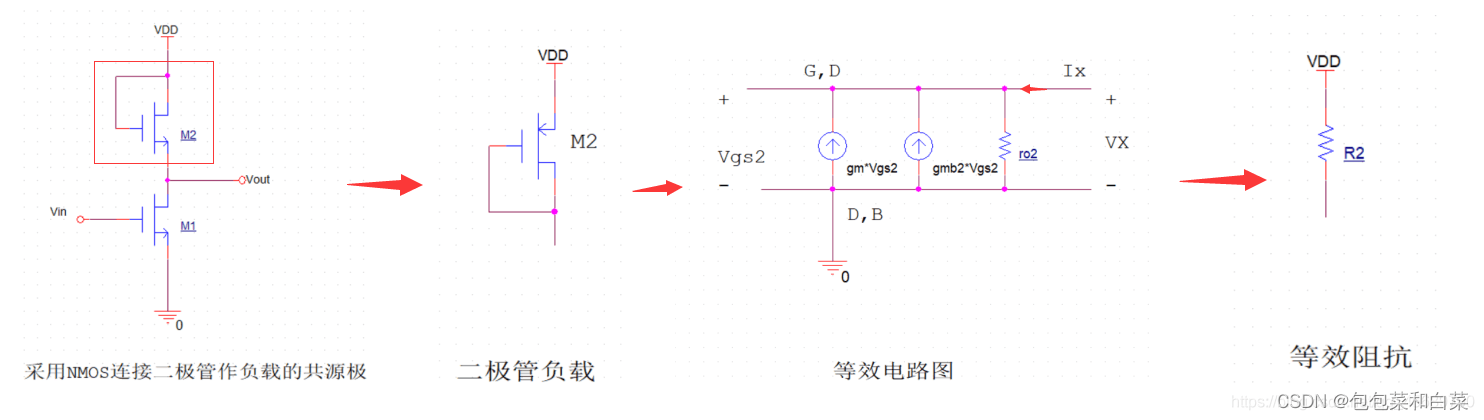

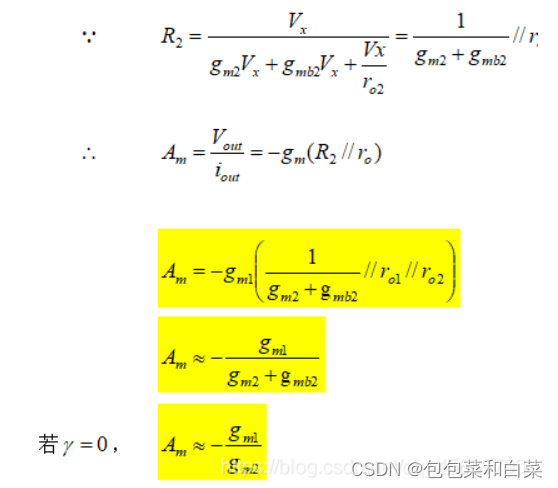

NMOS做二极管负载:

对于M2,从Vout看进去的等效电阻为 ,

对于M1,从Vout看进去的等效电阻为

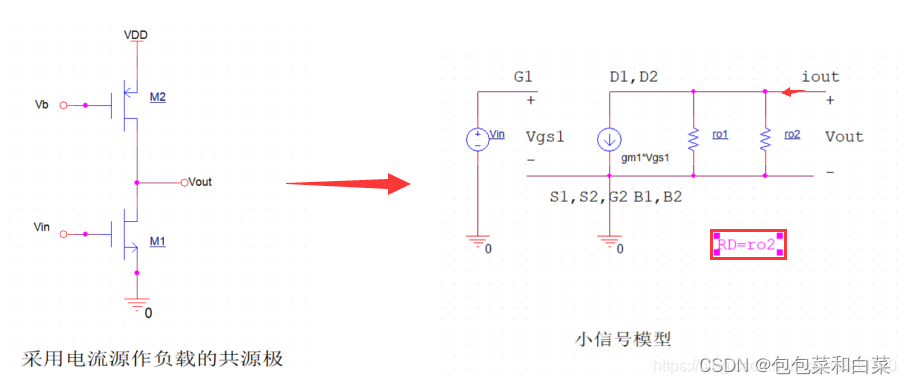

电流源做负载的共源级:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2060

2060

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?