脉冲控制LSI/ASIC芯片的定义与核心功能

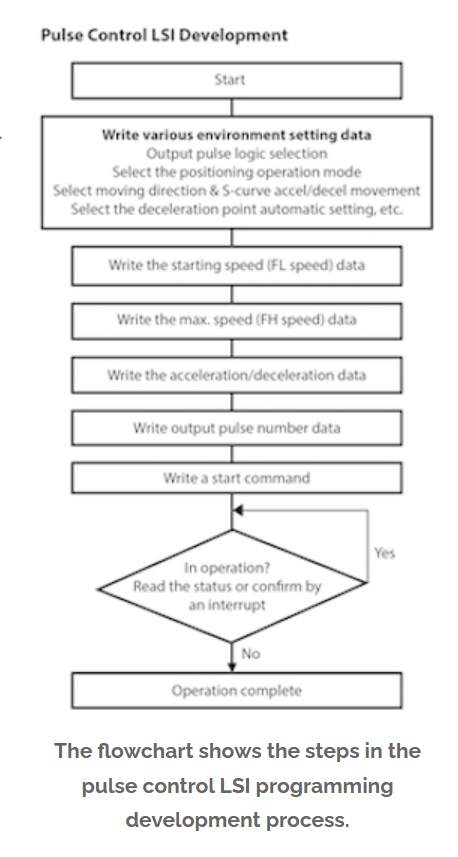

脉冲控制LSI(大规模集成电路)和ASIC(专用集成电路)是专为运动控制设计的集成电路芯片,其核心功能是通过生成高精度脉冲序列来控制电机的速度、加速度和方向。这类芯片通常集成脉冲生成器、逻辑控制器和通信接口,能够直接驱动步进电机、伺服电机等执行机构,同时支持复杂的运动曲线规划(如线性加减速、S型曲线加减速)。

技术特点对比:

-

LSI:

- 定义:将1000个以上元件集成在单一芯片上,包含小型存储器、微处理器及可编程逻辑模块。

- 在运动控制中的应用:常用于通信协议处理(如CC-Link IE Field)与基础运动功能的集成,例如CP520芯片集成以太网通信ASIC和运动控制功能。

- 优势:高集成度降低系统复杂度,支持多任务并行处理。

-

ASIC:

- 定义:针对特定任务(如电机加减速控制)定制设计的芯片,硬件级优化实现最高性能。

- 在运动控制中的应用:内置运动轨迹算法(如S曲线加减速),直接生成驱动信号,例如ZH6429芯片集成路径规划算法和SPWM发生器。

- 优势:相比通用芯片,功耗降低30%-50%,响应速度提升2-5倍。

在电机控制中的核心作用

1. 脉冲生成与运动曲线实现

脉冲控制芯片通过精确调节脉冲频率(决定转速)和脉冲数量(决定位移)实现电机控制。例如,1.8°步进电机在2细分模式下需要400个脉冲完成一周转动。

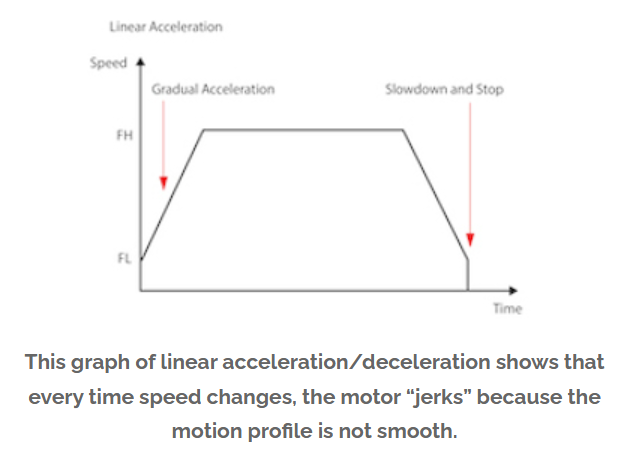

- 线性加减速:加速度恒定,算法简单但存在启停冲击(加速度不连续导致机械振动)。

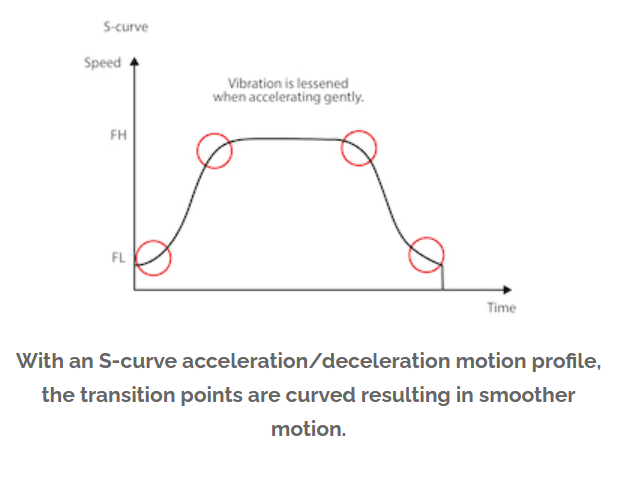

- S型加减速:通过五阶段或七阶段模型(加加速→减加速→匀速→加减速→减减速)实现加速度连续变化,降低冲击,适用于半导体设备等精密场景。

2. 系统资源优化

专用芯片通过硬件加速减轻主控单元(CPU/FPGA)的负担:

- CPU局限性:需通过软件生成脉冲,占用计算资源且实时性差(例如中断延迟导致脉冲丢失)。

- ASIC优势:内置硬件计数器、PWM模块,支持微秒级响应,且开发周期缩短50%以上。

与CPU/FPGA方案的性能对比

| 指标 | CPU | FPGA | 脉冲控制LSI/ASIC |

|---|---|---|---|

| 实时性 | 毫秒级延迟(受OS调度影响) | 微秒级延迟(并行处理) | 纳秒级延迟(硬件逻辑固化) |

| 开发难度 | 低(C/Python编程) | 高(需HDL语言) | 中(参数配置驱动库) |

| 功耗 | 高(通用计算架构) | 中(可重构电路静态功耗) | 低(专用电路优化) |

| 灵活性 | 高(软件可编程) | 极高(硬件可重构) | 低(功能固化) |

| 典型应用 | 简单点位控制 | 高速多轴同步 | 高精度轨迹控制(如S曲线) |

案例对比:

- 基于TMS320F2812的步进电机控制:DSP芯片通过软件实现S曲线算法,需消耗80%的CPU资源。

- ZH6429芯片:硬件直接生成S曲线脉冲,CPU仅需发送目标位置指令,资源占用低于5%。

应用场景与选型建议

-

高精度场景(半导体、医疗设备):

- 优先选择ASIC芯片,利用其内置的S曲线算法和抗干扰设计(如THB7128芯片支持1/128细分,定位精度达0.014°)。

-

多协议通信需求(工业机器人):

- 选用集成通信功能的LSI(如CP520支持CC-Link IE Field和运动控制),减少外部接口芯片数量。

-

低成本简单控制(家电、消费电子):

- 采用通用LSI或低端ASIC(如A4988驱动芯片),通过线性加减速满足基本需求。

技术发展趋势

- 算法硬件化:将更复杂的运动规划算法(如前瞻控制、自适应加减速)集成至ASIC,减少对主控单元的依赖。

- 异构集成:LSI与ASIC融合(如CP520集成MPU和ASIC),兼顾灵活性与高性能。

- 低功耗设计:采用28nm以下工艺制程,功耗降低至传统方案的1/3,适用于便携式设备。

通过专用脉冲控制芯片,工程师可在资源成本、开发效率和运动性能之间实现最优平衡,尤其在需要高可靠性及实时性的工业场景中,其优势显著超越通用计算方案。

2323

2323

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?