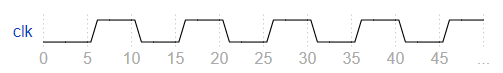

Testbench

1 Tb/clock

一个已知的的模块具有以下声明:

module dut ( input clk ) ;

编写一个测试文件,创建一个模块dut的实例(实例名称任意),并创建一个时钟信号以驱动模块的clk输入。时钟的周期为10 ps。时钟应初始化为零,其第一次转换为0到1。

module top_module ( );

reg clk=1'd0;

always #5 clk=~clk;

dut dut(.clk(clk));

endmodule

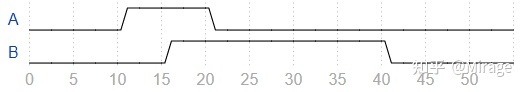

2 Tb/tb1

编写一个Verilog测试文件,为输出A和B生成以下波形:

module top_module ( output reg A, output reg B );//

// generate input patterns here

initial begin

A=0;

B=0;

#10 A=1;

#5 B=1;

#5 A=0;

#20 B=0;

end

endmodule

//可以5s得写

3 Tb/and

module top_module();

reg [1:0] in;

reg out;

initial begin

in[1]=0;

in[0]=0;

#10 in[0]=1;

#10 in[0]=0;

in[1]=1;

#10 in[0]=1;

end

andgate andgate1(.in(in),.out(out));

endmodule

4 Tb/tb2

module top_module();

reg clk=0;

always #5 clk=~clk;

reg in,out;

reg [2:0] s;

initial begin

in=0;

s=3'h2;

#10 in=0;

s=3'h6;

#10 in=1;

s=3'h2;

#10 in=0;

s=3'h7;

#10 in=1;

s=3'h0;

#30 in=0;

end

q7 q71(.clk(clk),.in(in),.s(s),.out(out));

endmodule

5 Tb/tff

module top_module ();

reg clk=0;

always #5 clk=~clk;

reg reset,t,q;

initial begin

reset=1;

t=0;

#10 reset=0;

t=0;

#10 t=1;

end

tff tff1(.clk(clk),.reset(reset),.t(t),.q(q));

endmodule

123

123

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?