一、层次化设计理论学习

数字电路中根据模块层次不同有两种基本的结构设计方法:自底向上(Bottom-Up)的设计方法和自顶向下(Top-Down)的设计方法。

自底向上的设计是一种传统的设计方法,对设计进行逐次划分的过程是从存在的基本单元出发的,设计树最末枝上的单元要么是已经构造出的单元。在自底向上建模方法中,我们首先对现有的功能块进行分析,然后使用这些模块来搭建规模大一些的功能块,如此继续直至顶层模块。

自上而下的设计是从系统级开始,把系统分为基本单元,然后再把每个单元划分为下一层次的基本单元,一直这样做下去,直到直接可以用EDA元件库中的原件来实现为止。在自顶向下设计方法中,我们首先定义顶层功能块,进而分析需要哪些构成顶层模块的必要子模块;然后进一步对各个子模块进行分解,直到到达无法进一步分解的底层功能块。

二、全加器为例实现层次化设计

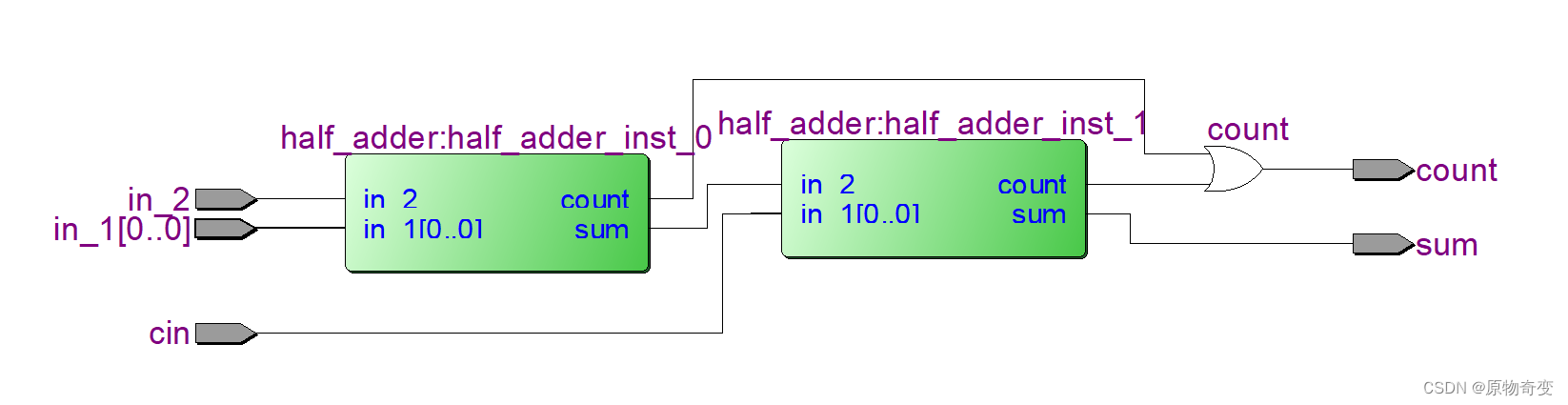

(1)实验框图

(2) 波形绘制

(3) 代码编写

module full_adder

(

input wire [0:0] in_1,

input wire in_2,

input wire cin,

output wire sum,

output wire count

);

wire [0:0] h0_sum;

wire [0:0] h0_count;

wire [0:0] h1_count;

half_adder half_adder_inst_0

(

.in_1(in_1),

.in_2(in_2),

.sum(h0_sum),

.count(h0_count)

);

half_adder half_adder_inst_1

(

.in_1(cin),

.in_2(h0_sum),

.sum(sum),

.count(h1_count)

);

assign count = (h0_count|h1_count);

endmodule(4)代码编译以及RTL视图

(5)仿真代码编写

`timescale 1ns/1ns

module tb_full_adder();

reg in_1;

reg in_2;

reg cin;

wire sum;

wire count;

initial

begin

in_1 <= 1'b0;

in_2 <= 1'b0;

cin <= 1'b0;

end

initial

begin

$timeformat(-9,0,"ns",6);

$monitor("@time %t:in_1 %b,in_2=%b,cin=%b,sum=%b,count=%b",$time,in_1,in_2,cin,sum,count);

end

always #10 in_1 <= {$random}%2;

always #10 in_2 <= {$random}%2;

always #10 cin <= {$random}%2;

full_adder full_adder_inist

(

.in_1(in_1),

.in_2(in_2),

.cin(cin),

.sum(sum),

.count(count)

);

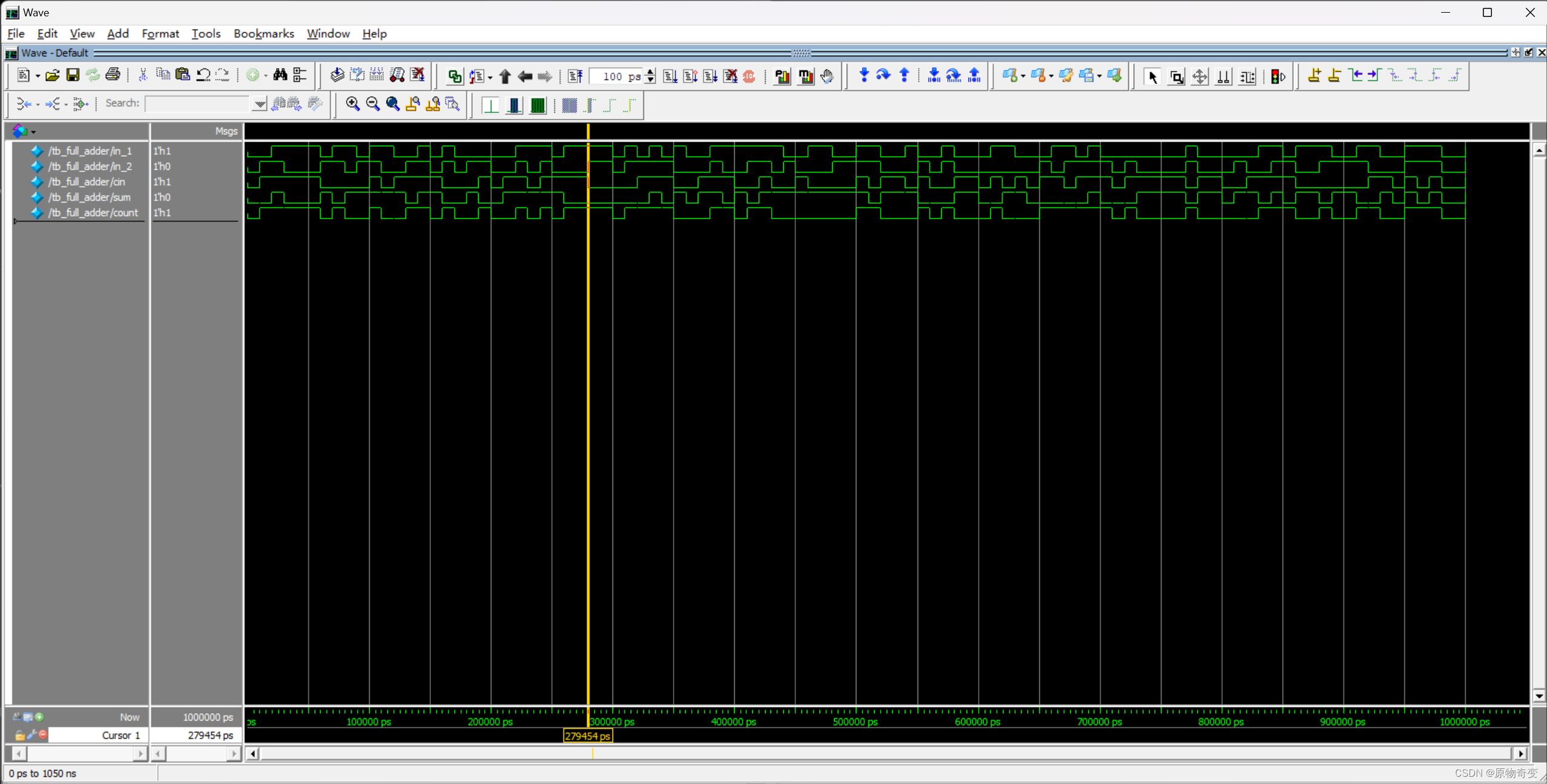

endmodule(6)仿真波形验证

3707

3707

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?