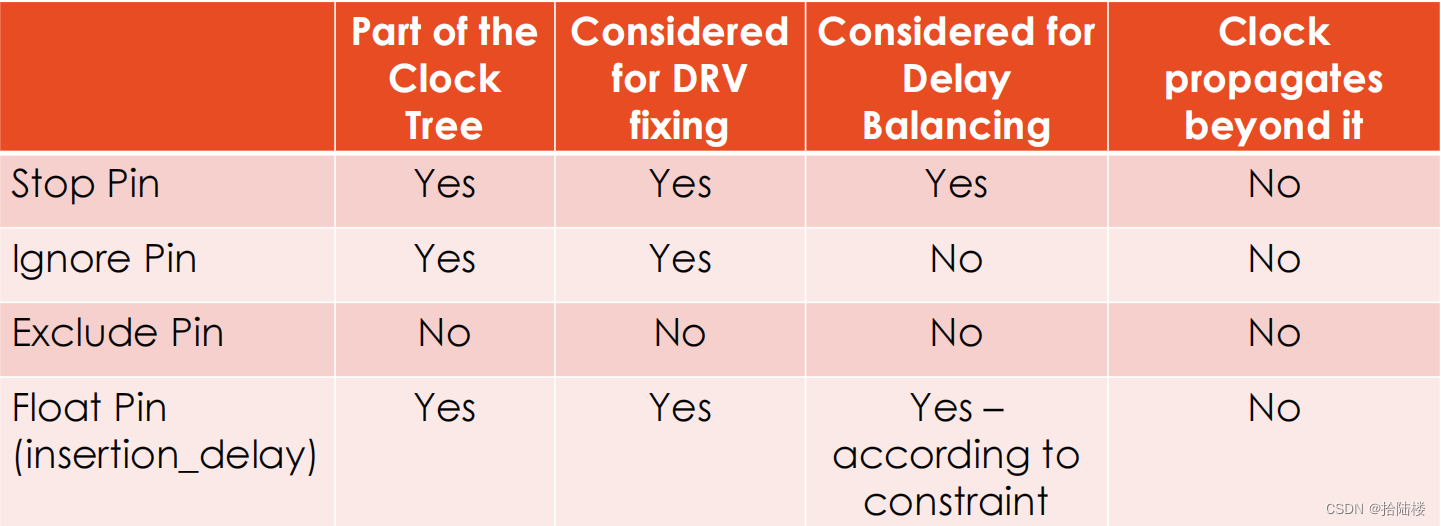

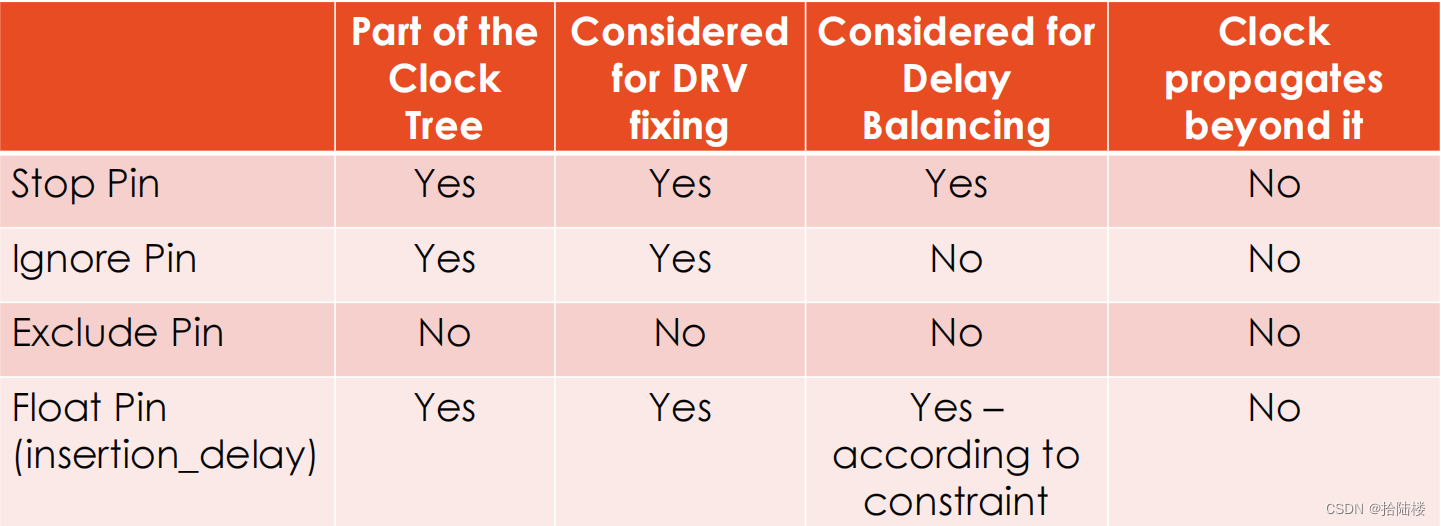

stop pin、ignore pin、exclude pin和float pin的区别如下图:

1、Stop pins

stop pin是clock tree的leaf pin,作为clock tree的终点,需要balance insertion delay(latency),clock sink都是stop pin。

stop pin、ignore pin、exclude pin和float pin的区别如下图:

stop pin是clock tree的leaf pin,作为clock tree的终点,需要balance insertion delay(latency),clock sink都是stop pin。

9185

9185

7293

7293

6581

6581

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?