描述

请编写一个序列检测模块,检测输入信号a是否满足01110001序列,当信号满足该序列,给出指示信号match。

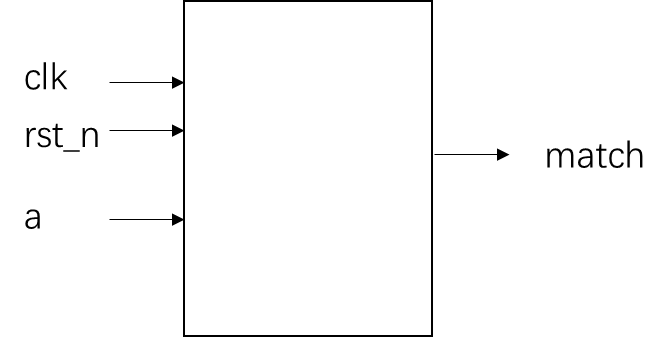

模块的接口信号图如下:

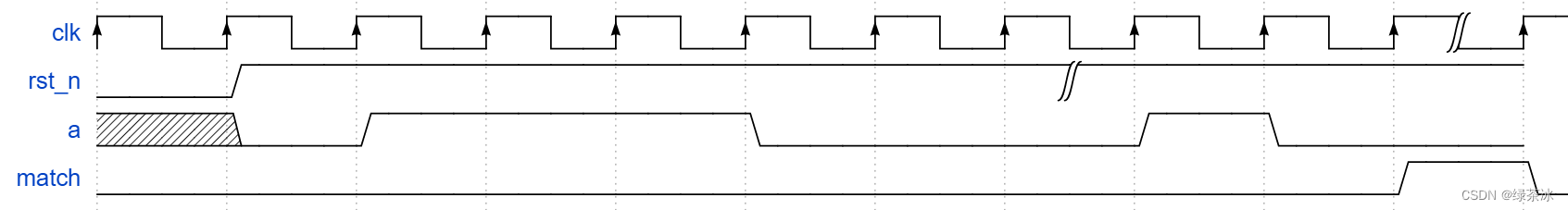

模块的时序图如下:

请使用Verilog HDL实现以上功能,并编写testbench验证模块的功能

输入描述:

clk:系统时钟信号

rst_n:异步复位信号,低电平有效

a:单比特信号,待检测的数据

输出描述:

match:当输入信号a满足目标序列,该信号为1,其余时刻该信号为0

问题分析:

当检测到第一个信号为true时,继续检测第二个信号……当检测到第n个信号为ture时,继续检测第n+1个信号,直到所有信号检测均为treu输出match为1,方法一:采用状态机来实现。方法二:采用数组缓存法

本文采用方法二来实现,用一个always块接收采集的下一个信号加入缓存序列,最先前的信号则移位溢出,移位操作可以采用位拼接和位截取实现。

移位操作可以表示为

seq<={seq[6:0],a};完整代码

`timescale 1ns/1ns

module sequence_detect(

input clk,

input rst_n,

input a,

output reg match

);

reg [7:0] seq;

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

match<=1'b0;

else if(seq==8'b01110001)

match<=1'b1;

else

match<=1'b0;

end

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

seq<=8'b00000000;

else

seq<={seq[6:0],a};

end

endmodule

770

770

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?