前言笔者:人生建议从第四章开始看。。。。

一、初认SDRAM

物理 Bank:传统内存系统为了保证 CPU 的正常工作,必须一次传输完 CPU 在一个传输周期内所需的数据。而CPU 在一个传输周期能接受的数据容量就是 CPU 数据总线的位宽当时控制内存与 CPU之间数据交换的北桥芯片也因此将内存总线的数据单位是 bit (位)位宽等同于 CPU 数据总线的位宽,而这个位宽就称之为物理 Bank (Physical Bank) 的位宽。

芯片位宽:每一片SDRAM缓存芯片本身的位宽。

CPU需要多少位宽数据,SDRAM就要提供多少位宽数据,位宽不够使用多片SDRAM级联。、

二、SDRAM操作时序

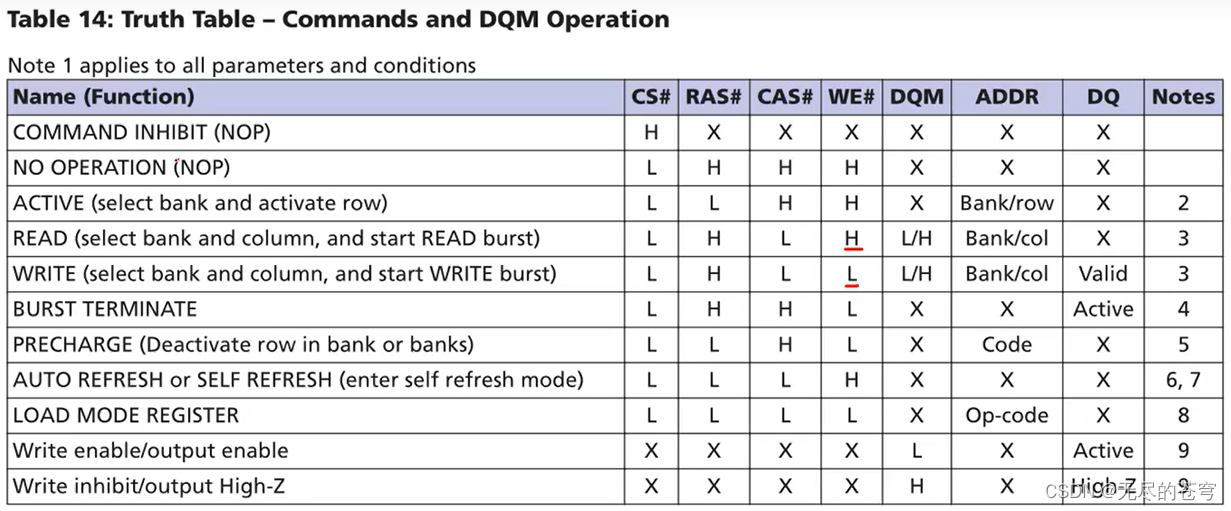

1、SDRAM操作指令

CS#:片选 RAS#:行选通 CAS#:列选通 WE#:读写切换 DQM:数据掩码 ADDR:数据总线 DQ:数据 Notes:参考详细说明

2、指令时序

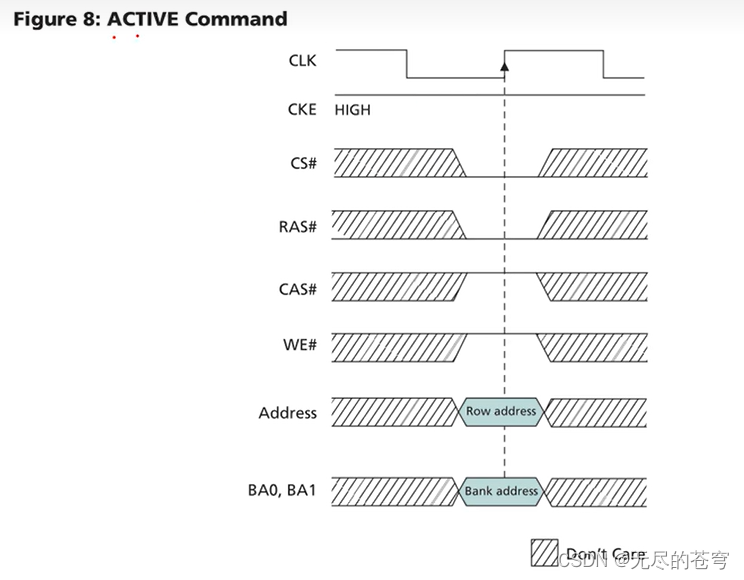

(1)ACTIVE Command(行激活指令)

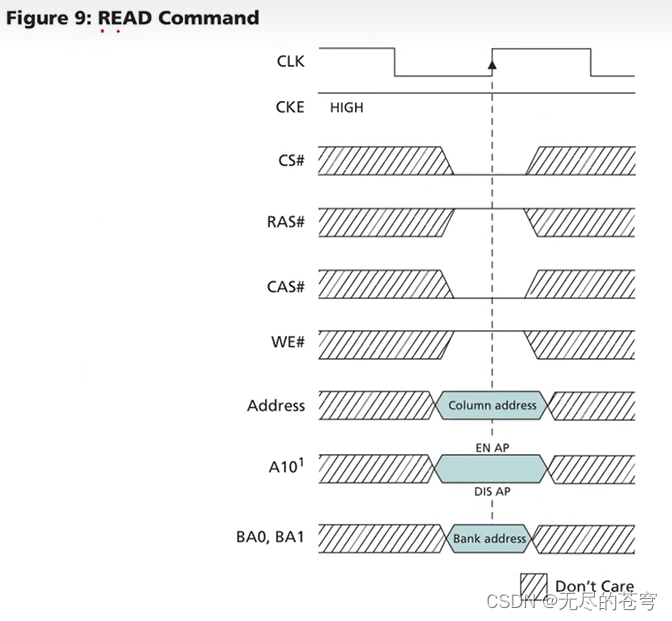

(2)READ Command(读,列激活)

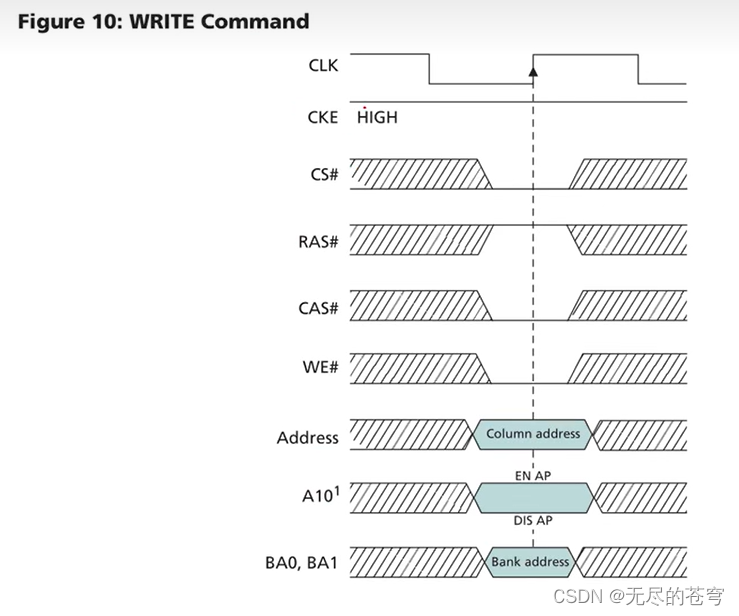

(3)WRITE Command(写,列激活)

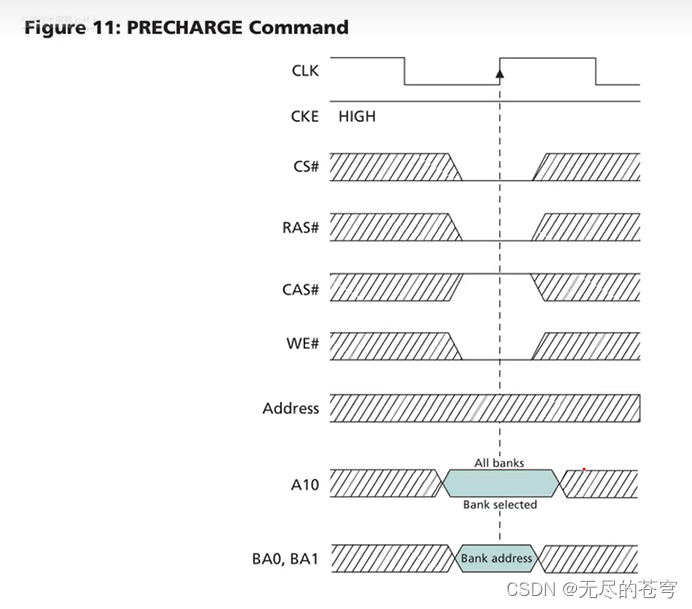

(4)PRECHARGE Command(手动预充电)

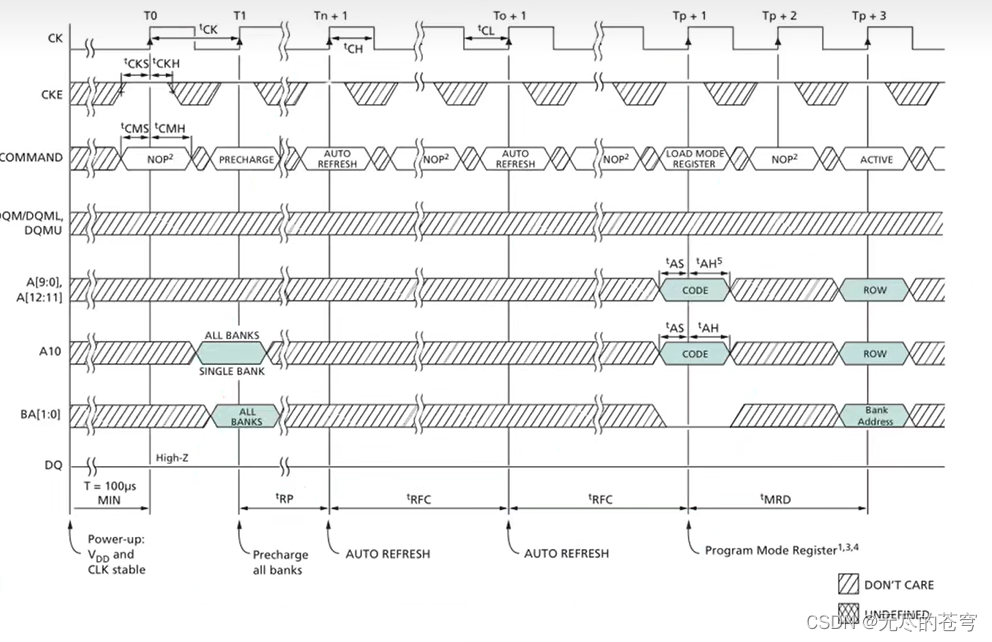

(5)初始化时序,加载模式寄存器

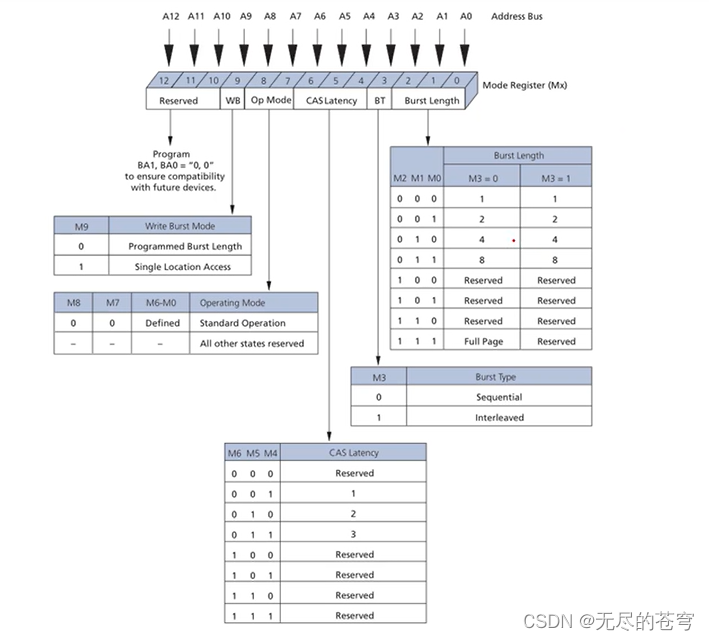

(6)配置模式寄存器

A0~2:突发模式 A3:突发类型 A4~6:CL延迟

(7)突发读时序

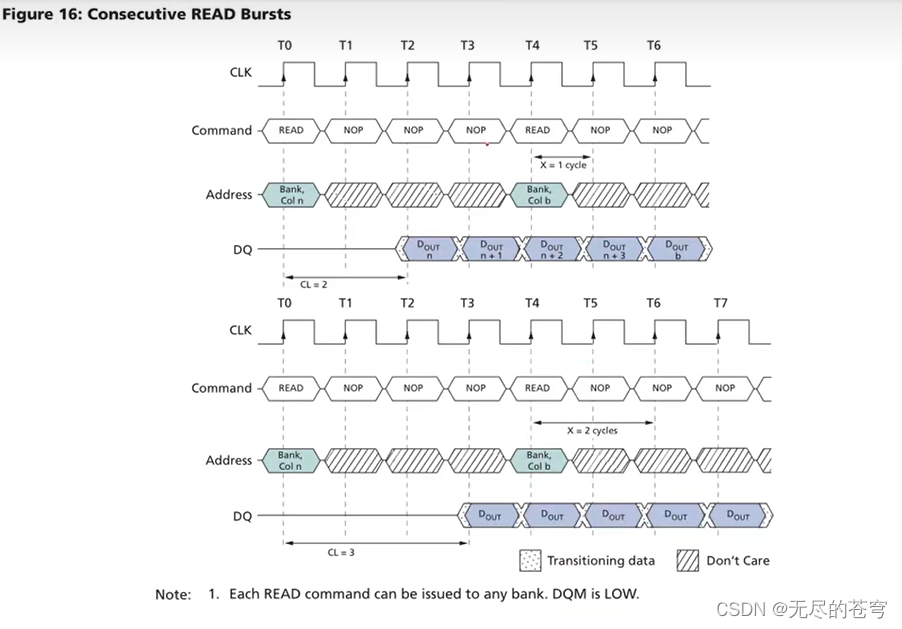

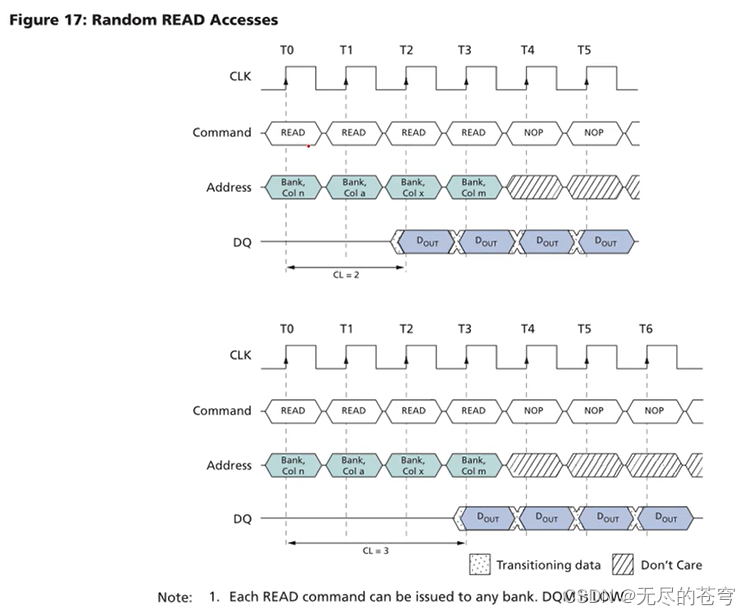

(8)连续发送读指令时序

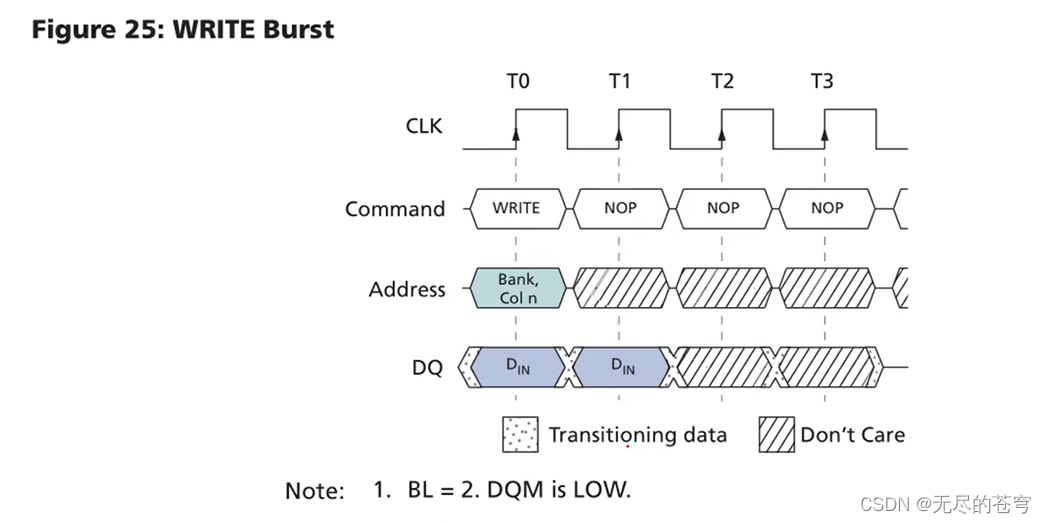

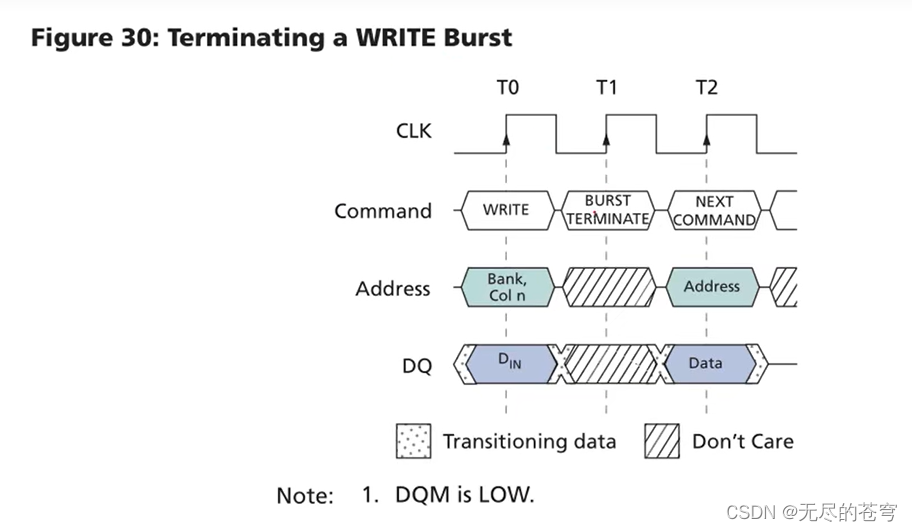

(9)突发写时序

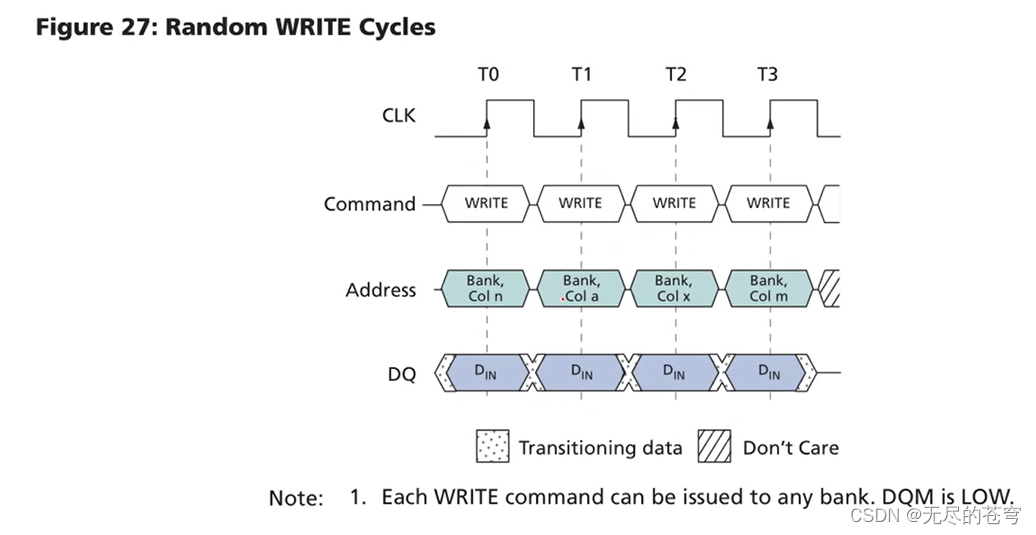

(10)连续写时序

(11)禁止指令

三、DDR2 SDRAM

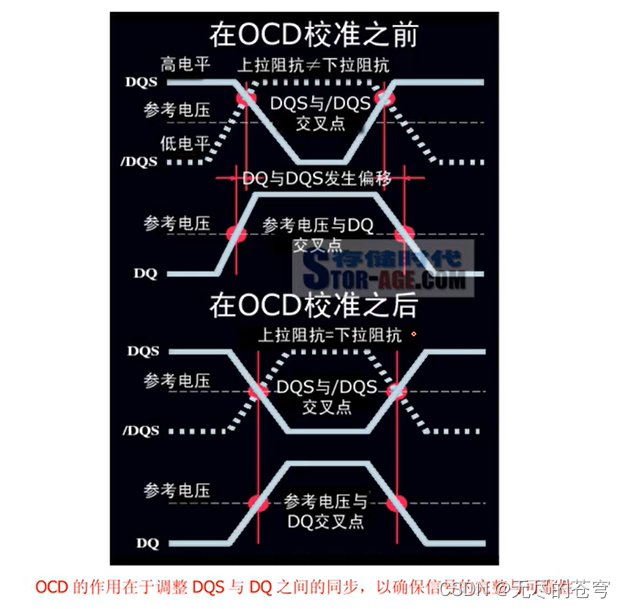

1、OCD校准

2、前置CAS、附加潜伏期、写入潜伏期

四、DDR3 SDRAM

1、与DDR2的区别之处

(1)突发长度

(2)寻址时序

(3)新增重置功能

(4)新增ZQ校准功能

(5)参考电压分成两个

(6)点对点连接

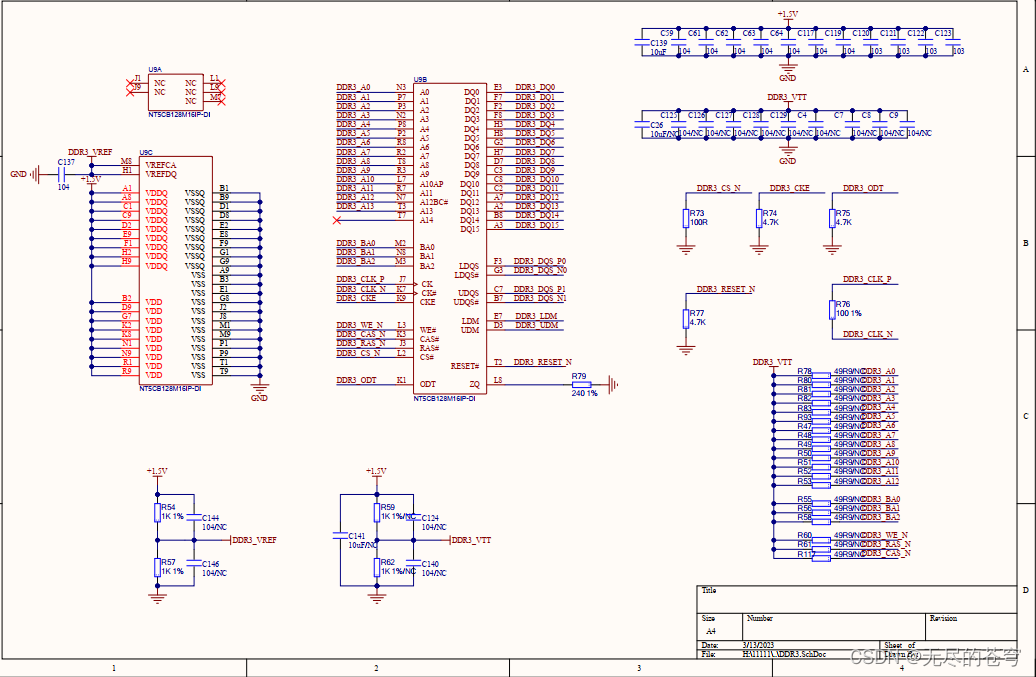

2、DDR3硬件设计与时序

DDR3

3、初始化时序

(1)上电一瞬间RESET拉低保持200us(再次期间其他信号无效)。

(2)RESET拉高前,CKE至少保持10ns拉低。

(3)至少等待500us后(期间CK差分始终提前CKSRX时间稳定),CKE拉高。

(4)CKE拉高后,等待tls时间,后发送NOP指令,继续等待tXPR时间。(期间ODT处于工作状态)

(5)发送MRS配置指令,每配置一个等待tXPR时间,MRX寄存器配置完成等待tDLIK=tMOD+tZQinit时间。

(6)在tDLIK等待时间内,发送ZQCL指令,以及NOP指令。到此整个DDR激活结束。

4、DDR3模式寄存器配置

(1)MR0寄存器

BL:突发长度 CL:等待 RBT:读的突发类型 CAS Latency:延时配置

TM:工作模式(常规/测试) DLL:重置(back返回值归零)

WR:写复原(重新写回原本数据) PPD:退出速度( )

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3316

3316

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?