一、XILINX器件原语

原语,是FPGA厂商针对其器件特征开发的一系列常用模块的名称。原语是FPGA芯片中基本元件,代表FPGA中实际拥有的硬件逻辑单元,如LUT,D触发器,RAM等。原语在设计中可以直接例化使用,是最直接的代码输入方式,原语和HDL原语的关系,类似于汇编语言和C语言的关系。

Xilinx公司的原语按功能分为10类,包括计算组件、I/O端口组件、寄存器、时钟组件、处理器组件、移位寄存器、配置和检测组件、RAM/ROM组件、Slice/CLB组件以及吉比特收发器组件。常用的原语包括时钟缓冲、差分和单端信号相互转换以及I/O处理(IDDR、ODDR)原语等。

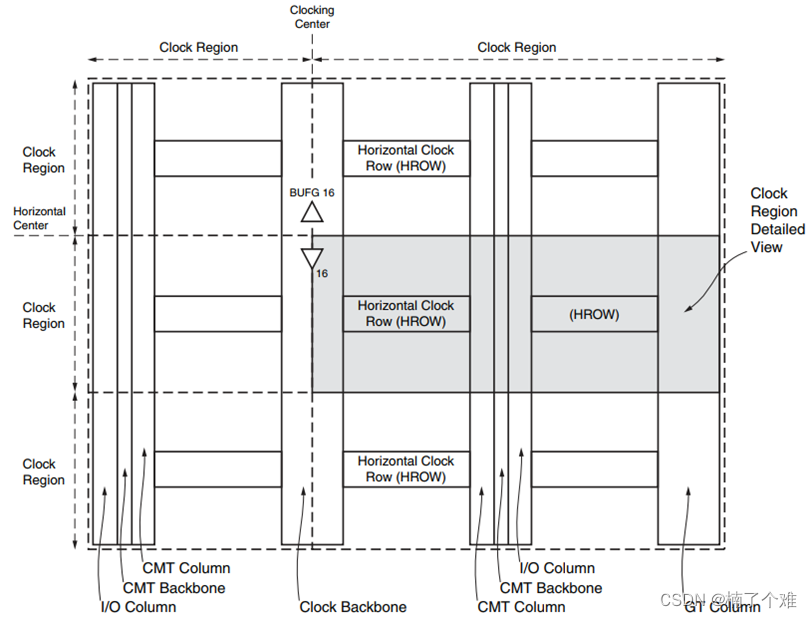

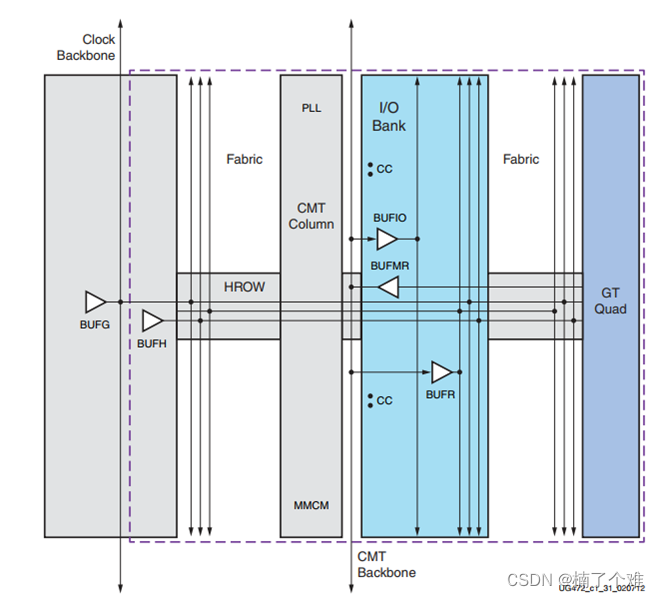

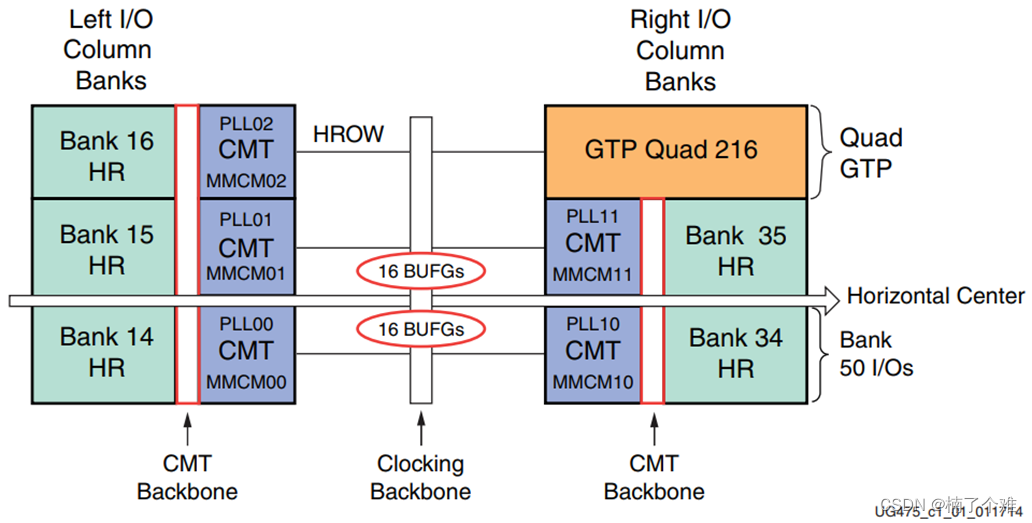

二、7系列FPGA高级时钟结构视图

三、时钟组件

时钟组件包括各种全局时钟缓冲器(BUFG)、全局时钟复用器、普通I/O本地的时钟缓冲器(BUFR)以及高级时钟管理模块。与其相关的原语包括: BUFG、 BUFR、BUFH、 BUFIO、 BUFGCE、 BUFGDLL和DCM等。

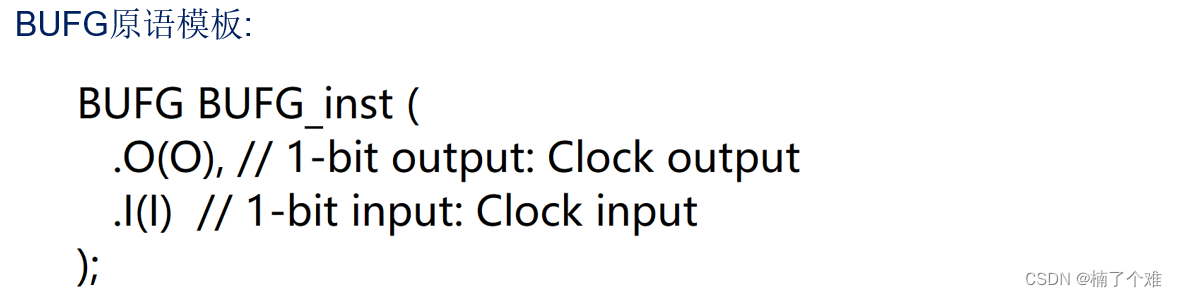

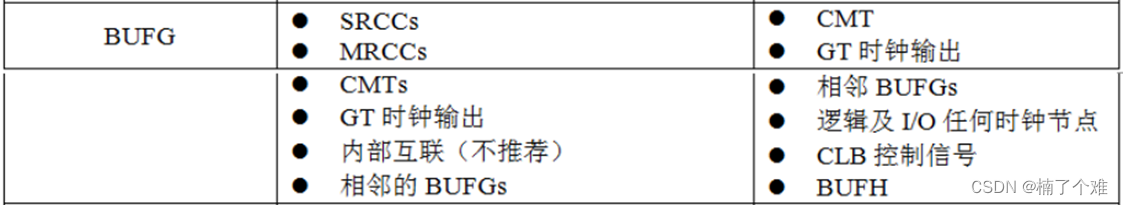

1、BUFG

全局缓冲器, BUFG 的输出到达 FPGA 内部的 IOB、 CLB、块 RAM 的时钟延迟和抖动最小 可以到达FPGA任何一个节点。

SRCCs只可以对本区域内时钟使用。MRCCs可以对相邻两个区域时钟使用 。

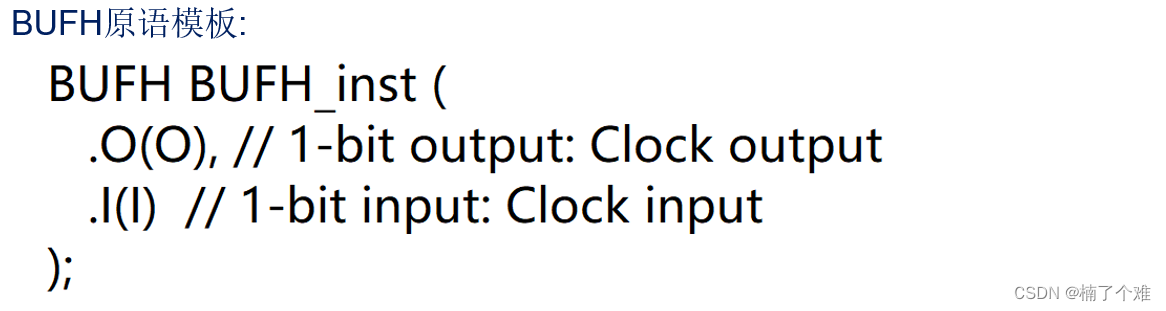

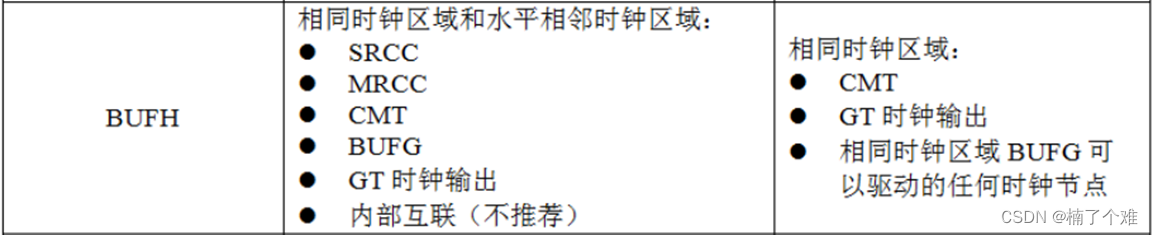

2、BUFH

水平时钟缓冲器,它相当于一个功能受限的BUFG,其输出时钟只能通过HROW在左右相邻的时钟区域内工作。每个区域内有12个BUFH可用。

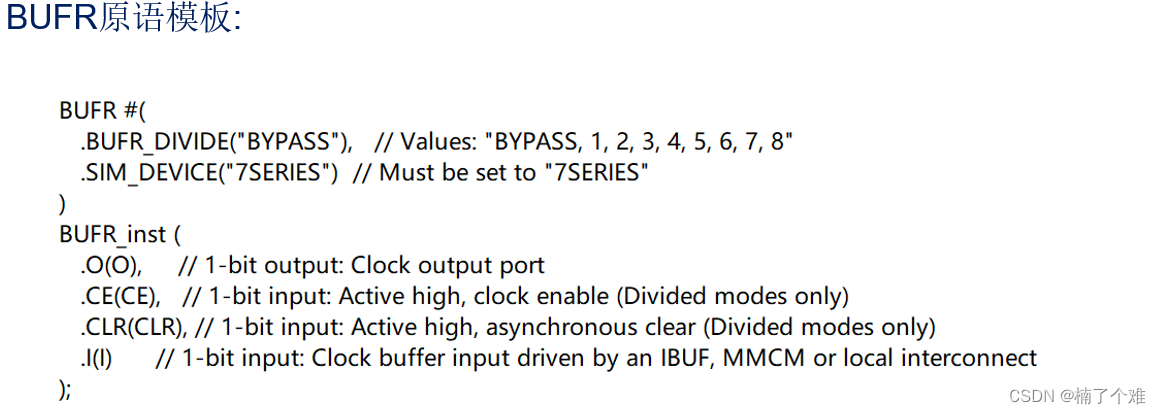

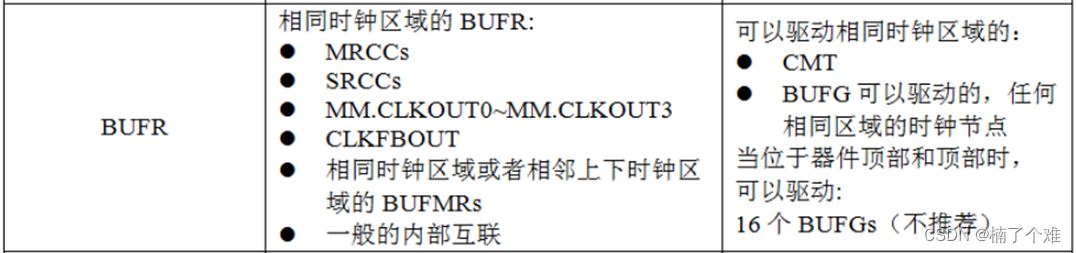

3、BUFR

区域时钟缓冲器,其输出只能作用在一个时钟区域,相当于BUFH的阉割版。

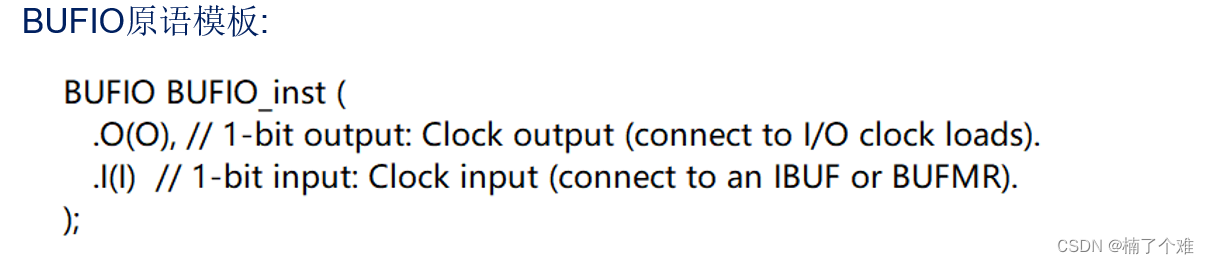

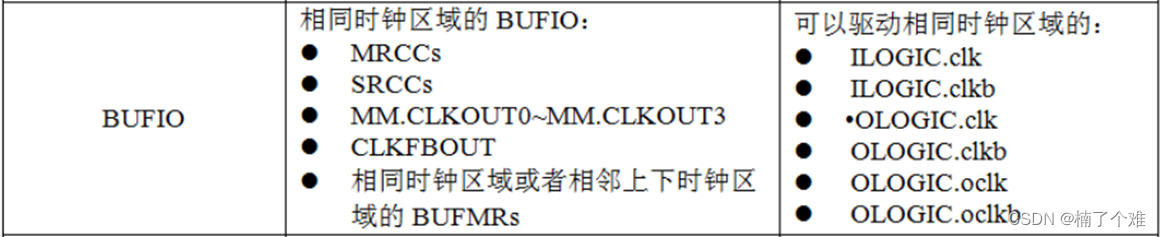

4、BUFIO

4、BUFIO

IO时钟缓冲器,其输出时钟只能作用在一个时钟区域的IO寄存器处,无法在FPGA内部逻辑使用。

5、时钟区域视图

6、缓冲器使用场景

| BUFG | BUFH | BUFMR | BUFR | BUFIO | |

| 使用场景 | 一般用在跨多个时钟区域的时钟上 | 一般用在相同时钟区域或者相邻时钟区域的时钟 | 当输入时钟需要连接多个区域的BUFR或者BUFIO时使用 | 可用于不需要跨区域的时钟,但一般用作IO资源的接口时钟 | 只能用于IO资源的接口时钟 |

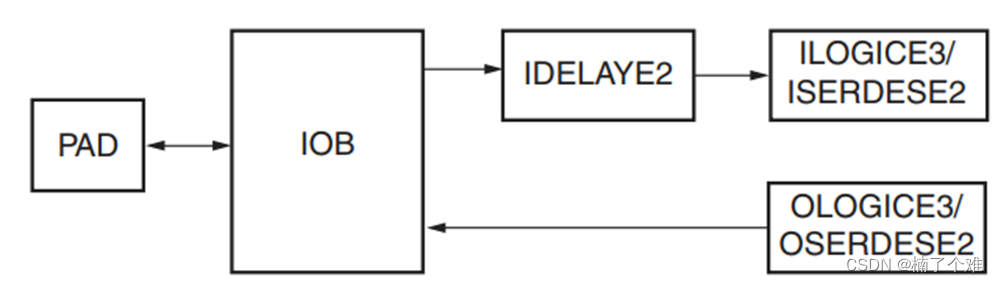

四、IO端口组件

I/O组件提供了标准单端I/O缓存(IBUF/OBUF)、DDR专用I/O信号缓存(IDDR/ODDR)、可变抽头延迟链(IDELAY/ODELAY)、上拉(PULLUP)、下拉(PULLDOWN)以及单端信号和差分信号之间的相互转换(IBUFDS/ OBUFDS) 等。

1、XA735T BANK分布

2、IO资源分布

3、IDDR

输入数据的双沿采样,是ILOGIC块中专用的寄存器,用于实现输入数据双沿采样。

ILOGICE3结构:

(1)工作模式

①OPPOSITE_EDGE mode 相反沿

②SAME_EDGE mode 相同沿

③SAME_EDGE_PIPELINED mode 相同沿流水模式

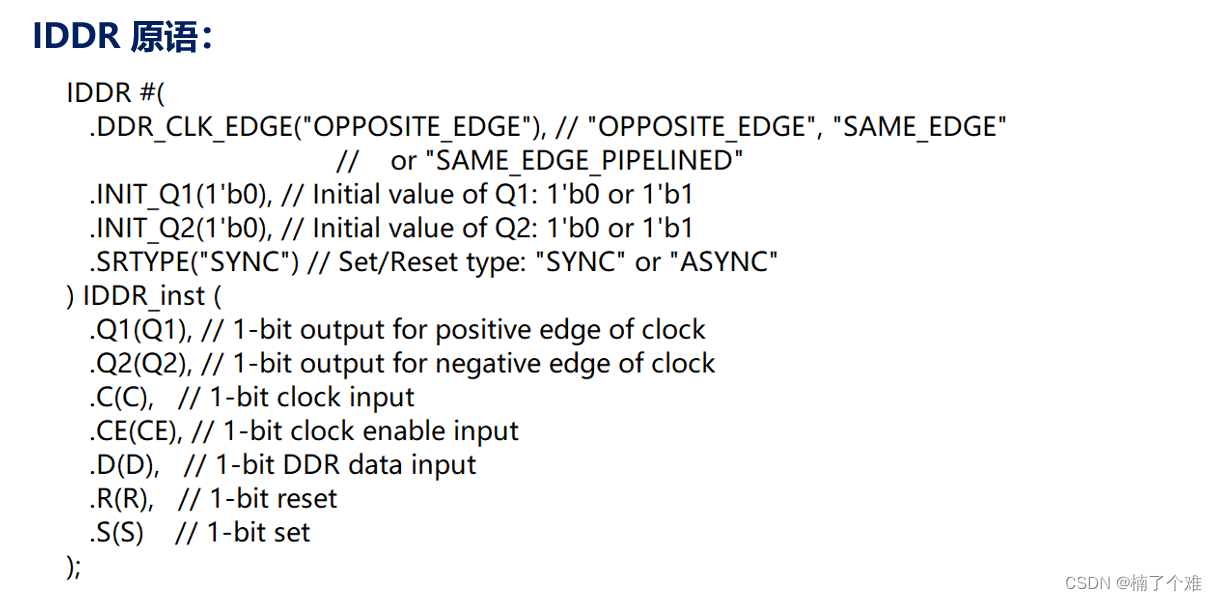

(2)IDDR原语

4、ODDR

输出数据的双沿采样,是OLOGIC块中专用的寄存器,用于实现输出数据双沿采样。

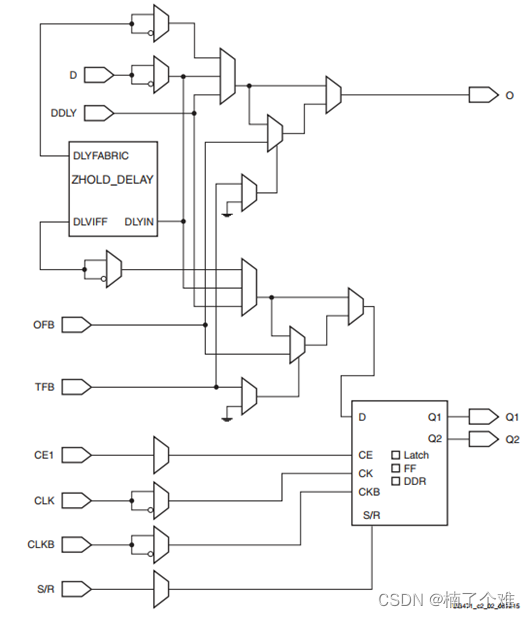

OLOGICE3 结构

(1)工作模式

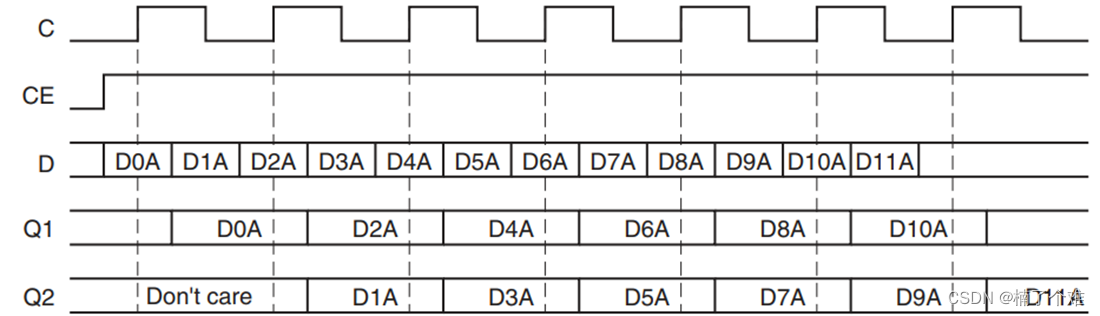

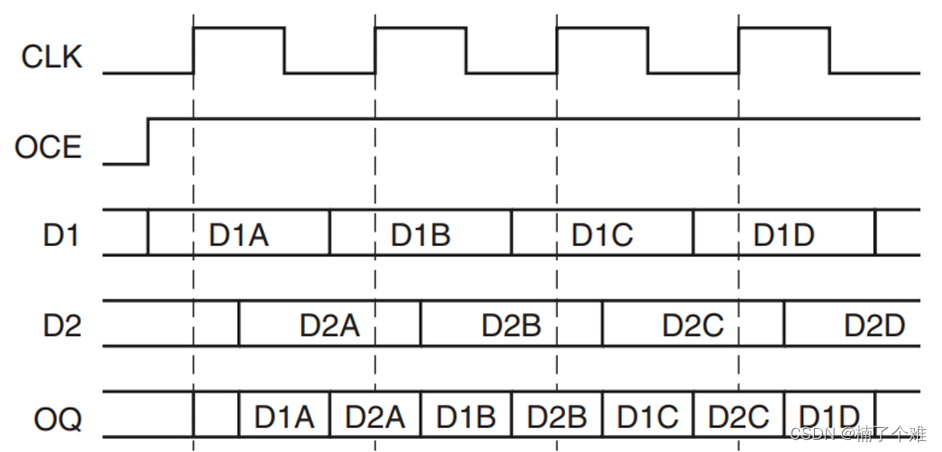

①OPPOSITE_EDGE mode 相反沿

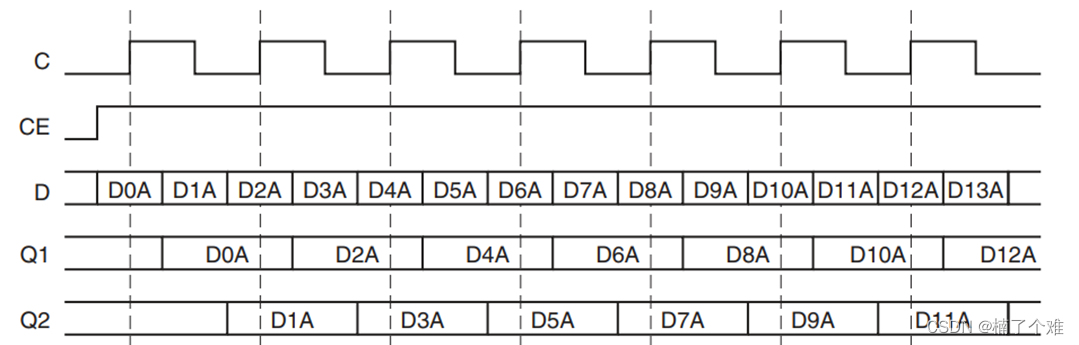

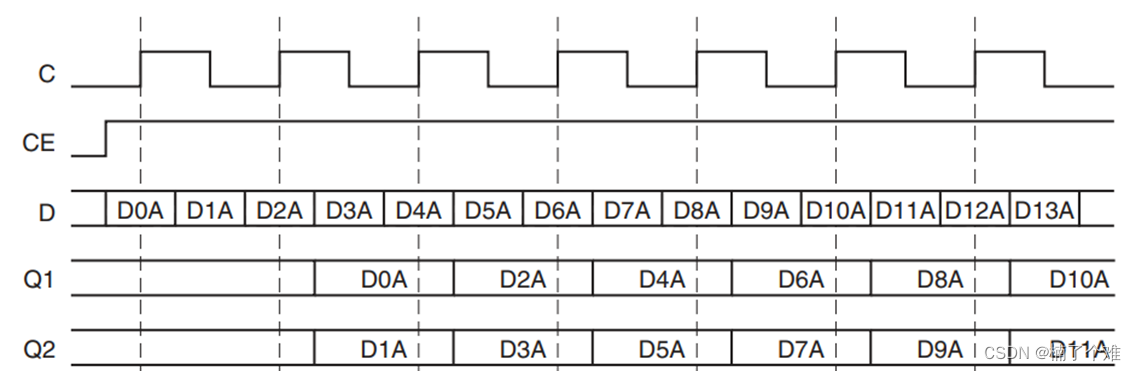

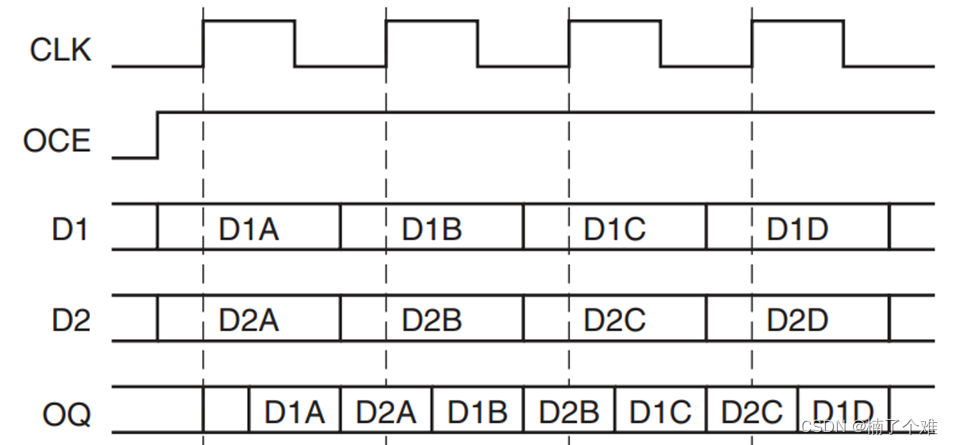

②SAME_EDGE mode 相同沿

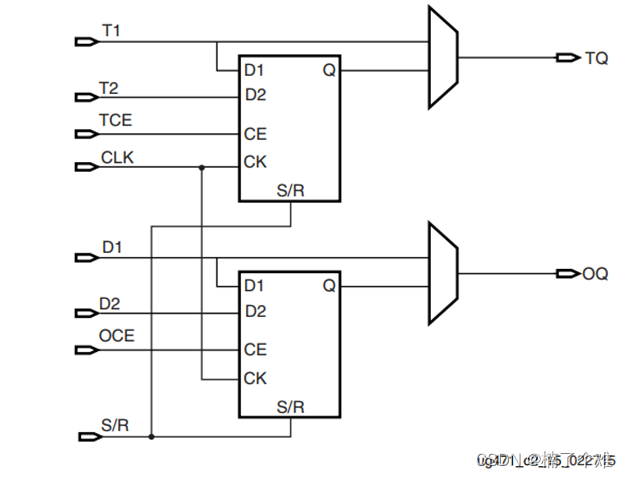

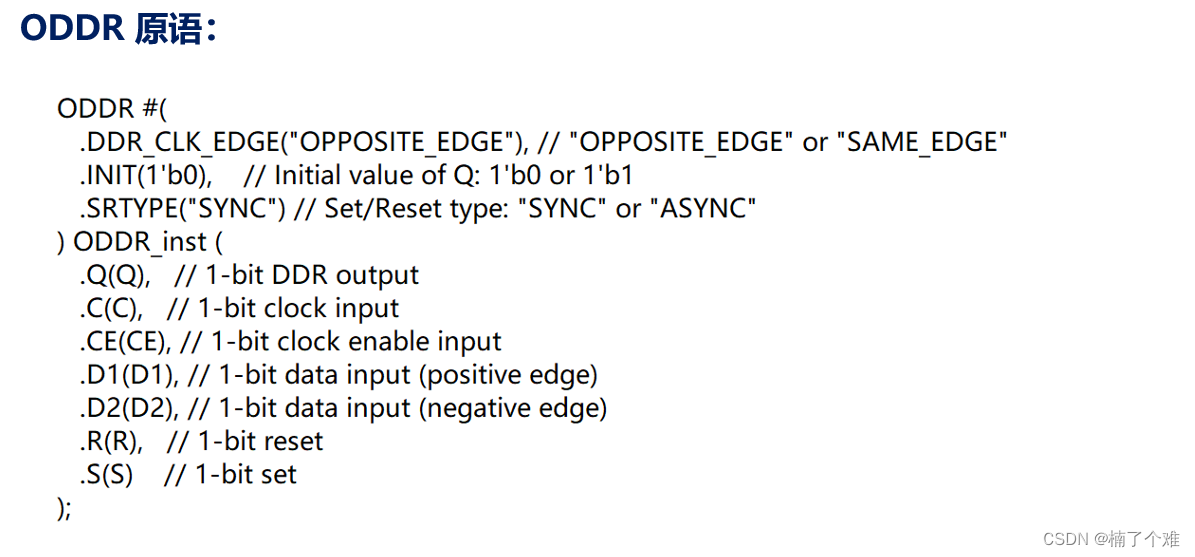

(2)ODDR原语

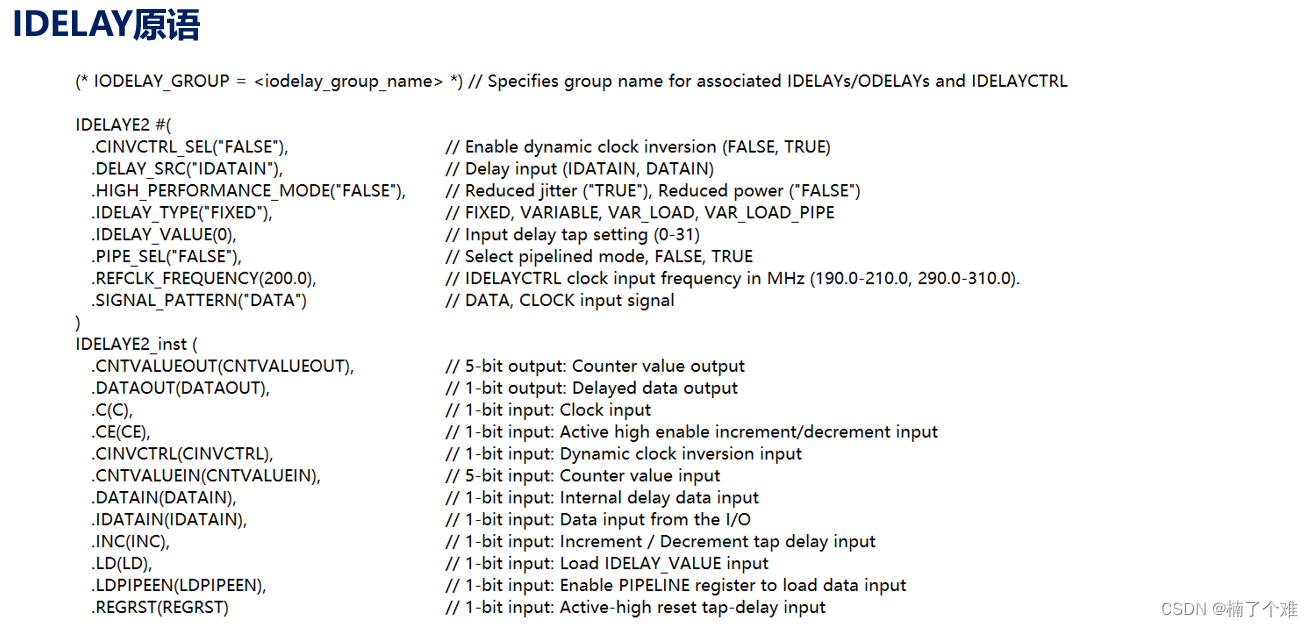

五、IDELAY原语

每个I/O模块都包含了一个可编程的延迟原语,称作IDELAYE2 。 IDELAY2是一个可编程的31阶延迟原语,它既可以应用于组合逻辑也可以应用于时序逻辑或者同时用于两者。

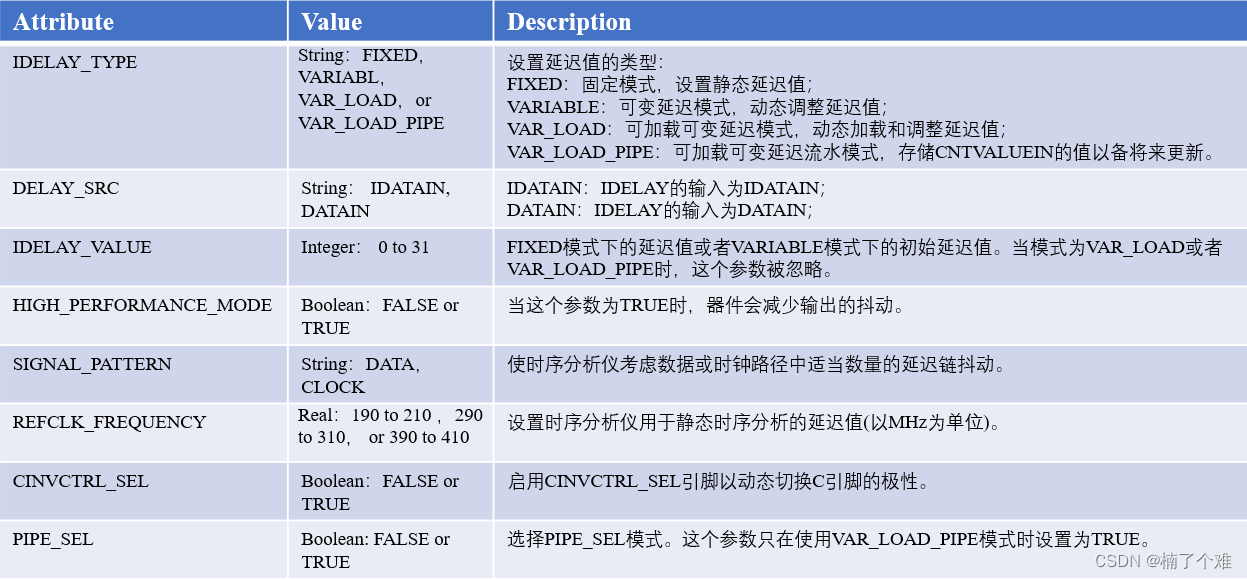

1、IDELAY参数

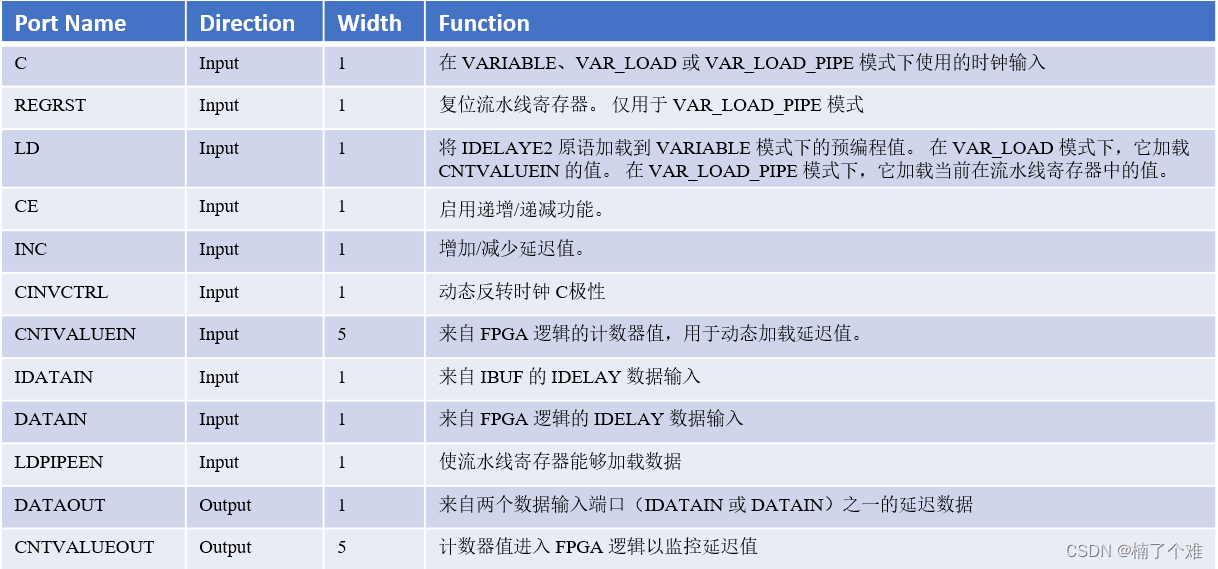

2、IDELAY端口

3、FIXED模式

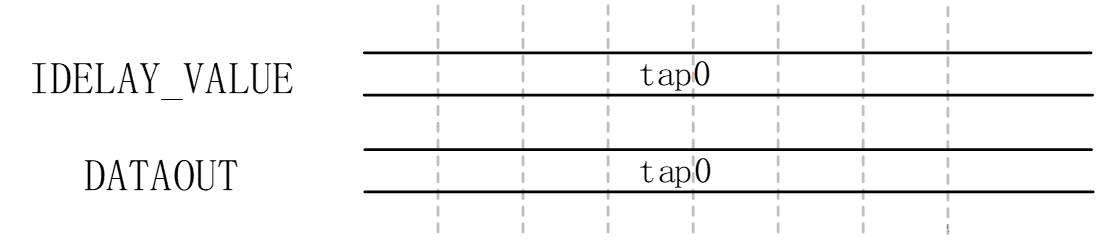

在固定延迟模式中,延迟值在配置时预设为属性 IDELAY_VALUE 确定的延迟值。 配置后,此值无法更改。

FIXED时序

输入输出延迟值为tap0,如果IDELAY_VALUE为0,那么DATAOUTA相对于输入延迟600ps

4、VARIABLE模式

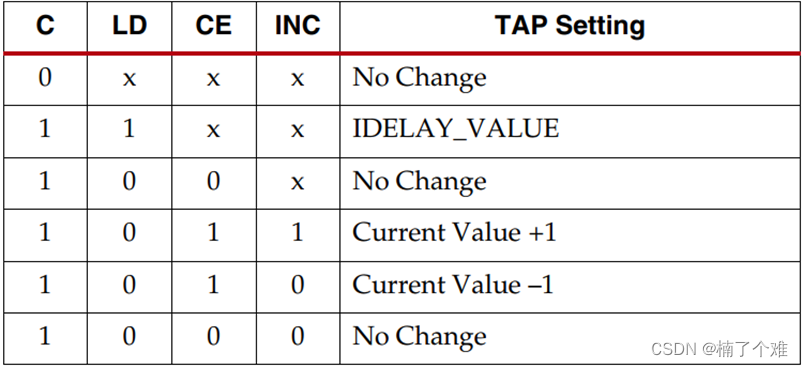

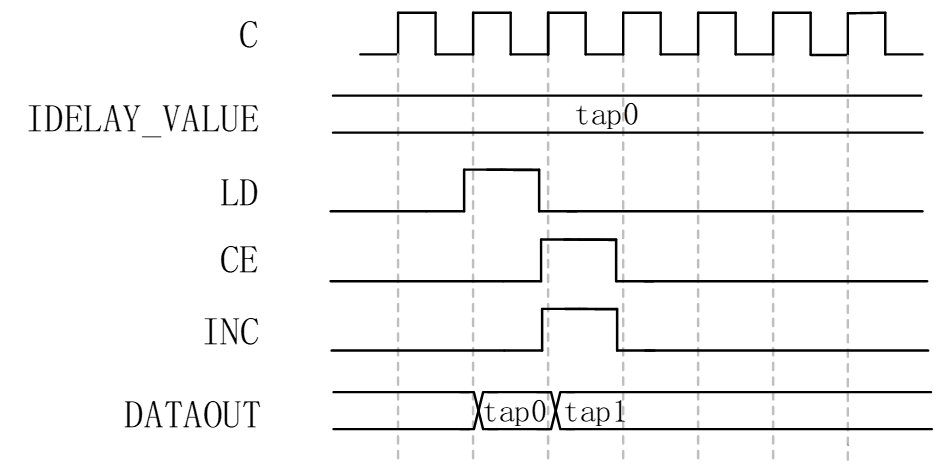

在该模式下,延迟值可以在配置后通过CE和INC端口进行动态配置。

VARIABLE时序:

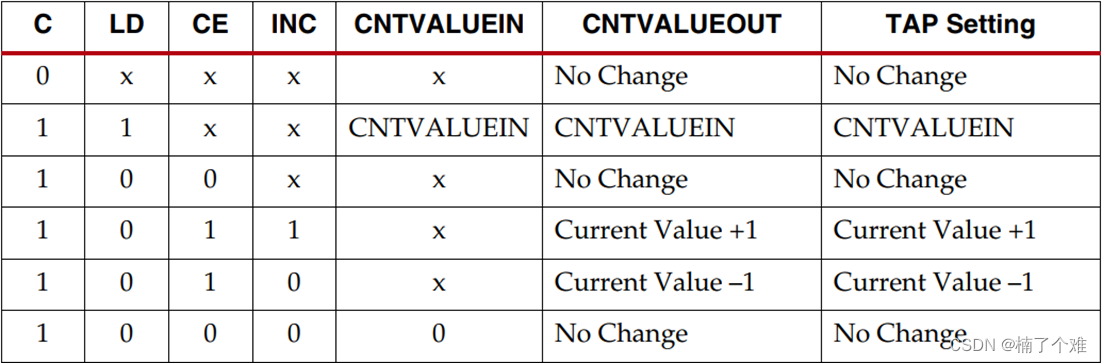

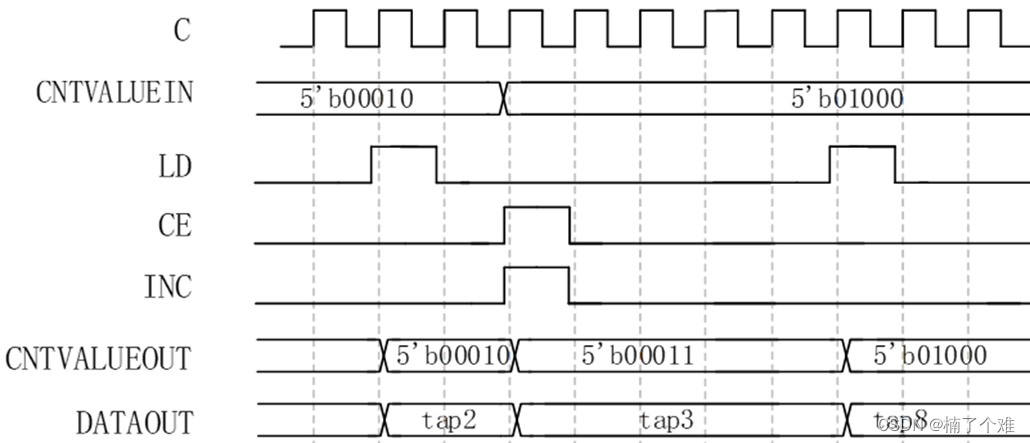

5、VAR_LOAD模式

该模式下功能与VARIABLE模式下类似,只不过可以通过CNTVALUEIN加载延迟节拍数,多了一种延迟加载方法。当LD端口有效时可以加载新的延迟CNTVALUE值到控制模块。

VAR_LOAD时序:

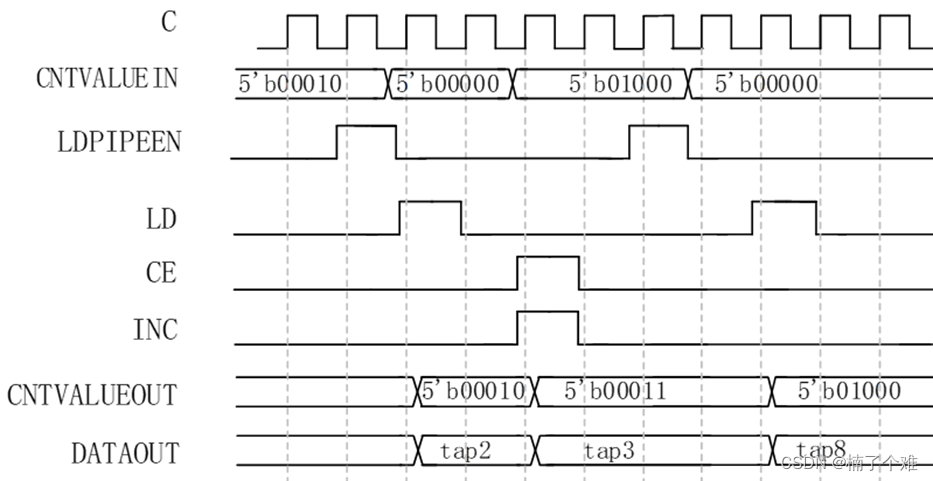

6、VAR_LOAD_PIPE模式

VAR_LOAD_PIPE 类似于 VAR_LOAD 模式,能够存储 CNTVALUEIN 值以备将来更新。

VAR_LOAD_PIPE时序:

7、IDELAY原语

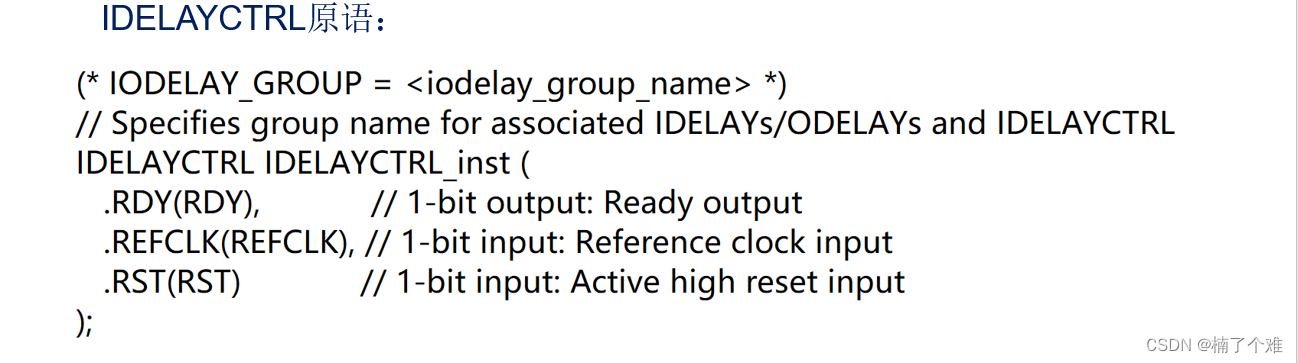

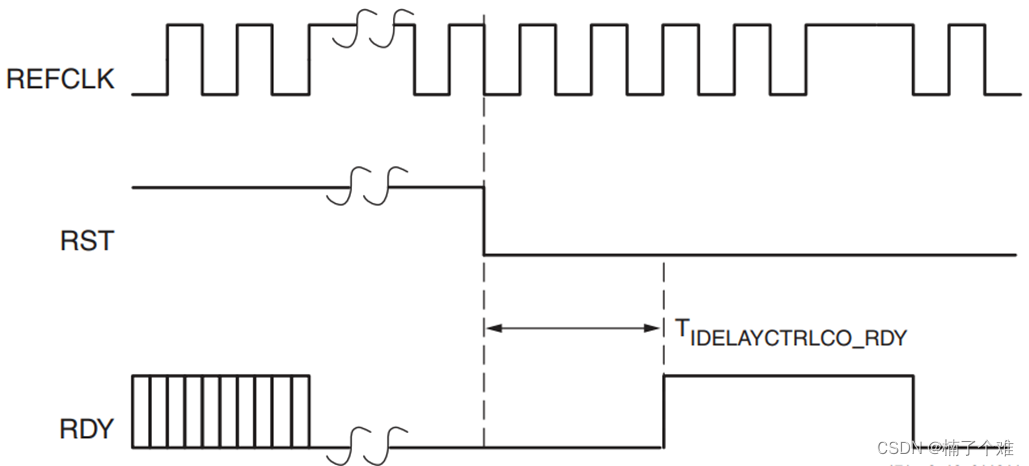

8、IDELAYCTRL

IDELAYCTRL 模块连续校准其区域内的各个 IDELAY/ODELAY,以减少工艺、电压和温度变化的影响。 IDELAYCTRL 模块使用用户提供的 REFCLK 校准 IDELAY 和 ODELAY 。

IDELAYCTRL时序:

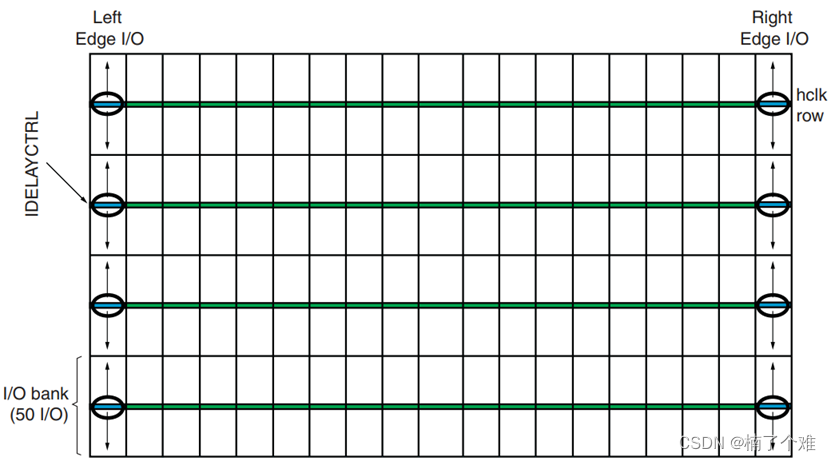

9、IDELAYCTRL 位置分布

IDELAYCTRL 模块存在于每个时钟区域的每个 I/O 列中。 IDELAYCTRL 模块校准其时钟区域内的所有 IDELAYE2 和 ODELAYE2 模块

1132

1132

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?