1、综合

-

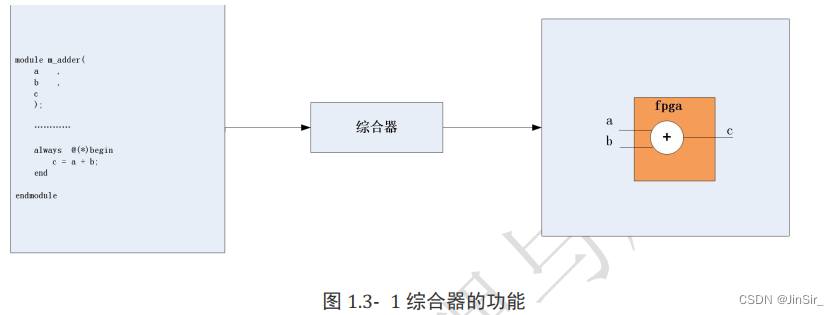

Verilog 是硬件描述语言, 顾名思义, 就是用代码的形式描述硬件的功能, 最终在硬件电路上实 现该功能。 在 Verilog描述出硬件功能后需要使用综合器对 Verilog 代码进行解释并将代码转化成实际的电路来表示, 最终产生实际的电路, 也被称为网表。这种将 Verilog 代码转成网表的工具就是综合器。

2、仿真 -

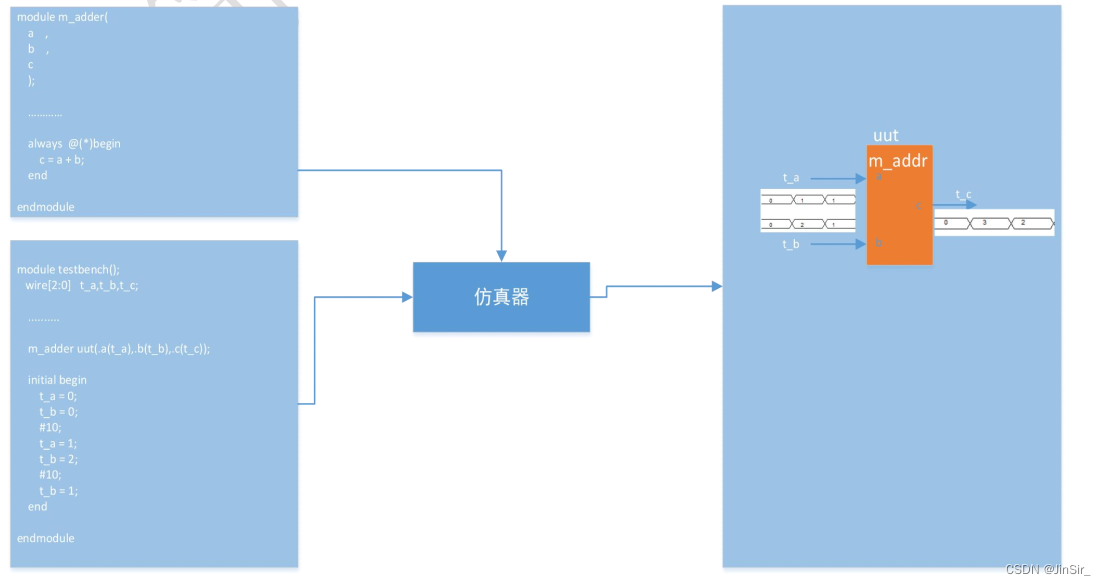

在综合前, 设计师可以在电脑里通过仿 真软件对代码进行仿真测试, 检测出 BUG 并将其解决, 最后再将程序烧写进 FPGA。

-

为了模拟真实的情况, 需要编写测试文件。 该文件也是用 Verilog 编写的, 其描述了仿真对象的 输入激励情况。 该激励力求模仿最真实的情况, 产生最接近的激励信号, 将该信号的波形输入给仿真 对象, 查看仿真对象的输出是否与预期一致。 需要注意的是:在仿真过程中没有将代码转成电路, 仿 真器只是对代码进行仿真验证。 至于该代码是否可转成电路, 仿真器并不关心。

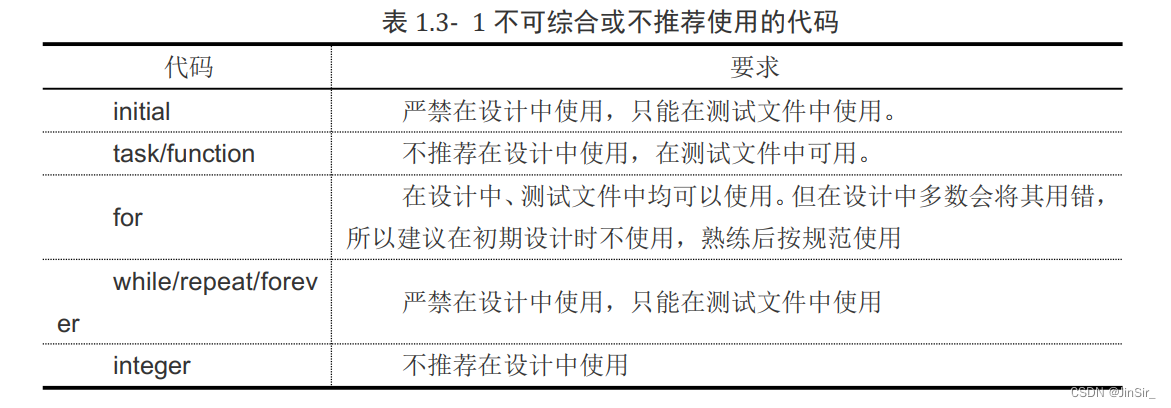

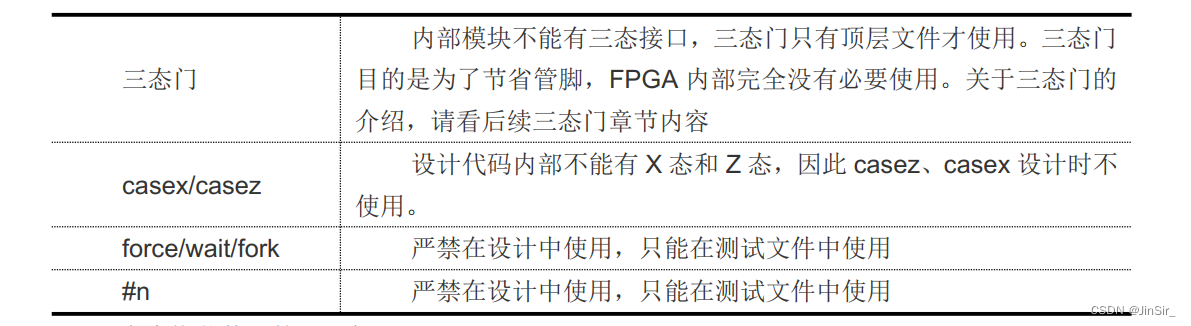

- Verilog 是描述硬件电路的, 其建立在硬件电路的基础之上。而有些语法结构只是以仿真测试为目的,是不能与实际硬件电路对应起来的。也就是说在使用这些语法时,将一个语言描述的程序映射成实际硬件电路中的结构是不能实现的, 也称为不可综合语法。

- 综合就是把编写的 rtl代码转换成对应的实际电路。 比如编写代码 assign a=b&c;EDA 综合工 具就会去元件库里调用一个二输入与门, 将输入端分别接上 b 和 c,输出端接上 a。当然, 工具会对必要的地方做一些优化, 比如编写一个电路 assing a=b&~b, 工具就会将 a 恒接为 0, 而不会去调用一个与门来搭这个电路。

- 综述所述, “综合” 要做的事情有: 编译 rtl 代码, 从库里选择用到的门器件, 把这些器件按照“逻辑” 搭建成“门” 电路。

- 不可综合, 是指找不到对应的“门” 器件来实现相应的代码。 比如“#100” 之类的延时功能,

简单的门器件是无法实现延时 100 个单元的, 还有打印语句等, 也是门器件无法实现的。 在设计的时候要确保所写的代码是可以综合的, 这就依赖于设计者的能力。

1389

1389

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?