目录

近来有空闲,把前几个学期做的实验上传上来。如有错误的地方欢迎大佬批评指正,有更好的方法也期待您的分享~

一、ROM

1. 设计ROM

ROM只能读不能写,因此ROM最原始的就是给一个地址,给一个clock,就输出一个数据。

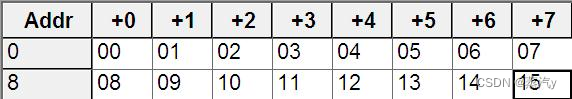

(1)设定数据

ROM是只读存储器,事先必须要有数据。新建Memory File存储器文件,也可以选择hex,也可以选择mif,这里我们选择hex。先建立一个数据,32个words,字的宽度为8。将Memory Radix存储单元的进制改为十六进制,方便输入数据,将Address Radix地址进制改为十进制。把事先要存放的数据把它的机器码写到存储单元,保存。

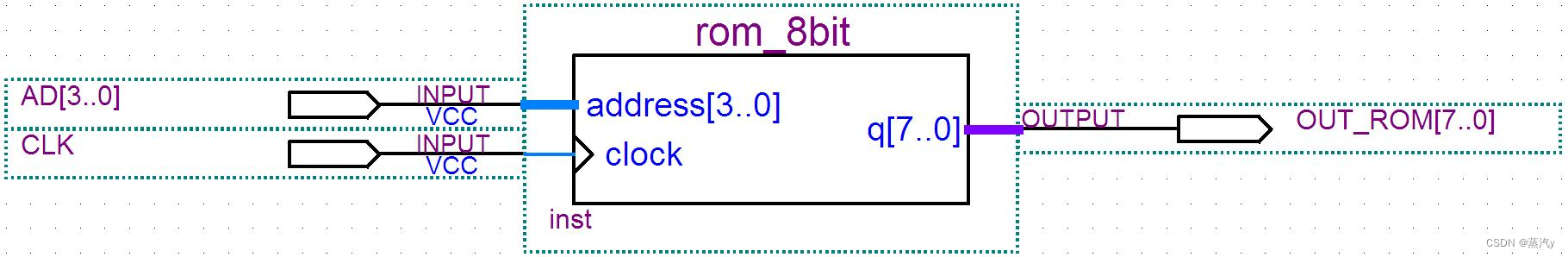

(2)调用宏功能模块的lpm_rom

初始设置宽度8bit,存32个字;单时钟;输出端锁存会差一个时钟,选择不锁存;添加(1)中建立的hex文件;连接输入输出。

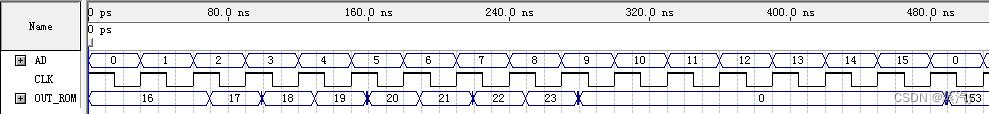

2. ROM功能仿真

设计AD每15ns换一个地址;CLK周期为15ns。

对比预设的hex文件数据,可见OUT_ROM的数据与预设数据一致。

二、RAM

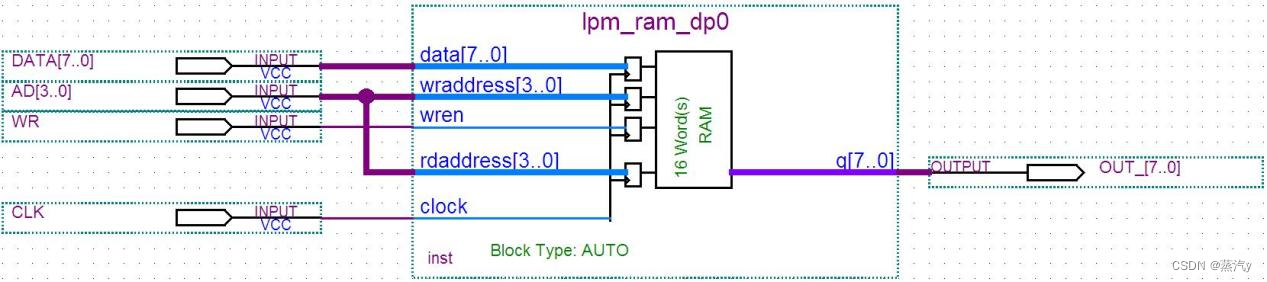

1. 设计RAM

(1)RAM中的宏功能模块中有两个模块可供选择的,一个是lpm_ram_dp,一个是lpm_ram_dp。因为lpm_ram_dq的存储读出和写入的规则跟上课讲的规则不同,所以选用lpm_ram_dp进行实验。

双端口存储器是指两个存储单元同时进行读或者写,这里做一个端口的;存储器存256位,数据a和b的宽度给8位;存储器构成auto默认;配置时钟,双时钟(读和写分开控制),一般来说给一个,第一个clock数据写入ram,写入之后,第一个clock进去是锁存,第二个clock是读出数据,一般来说,锁存地址之后紧接着应该就要输出数据,不能等到下一个clock,所以clock要去掉;为了不让输出差一个周期,输出的时候数据不要锁存;因为该存储器比较简单,所以不需要建立清零信号;连接输入输出。

2. RAM功能仿真

先写入一堆数据,然后再输出看。在0号地址写入00,1号地址写入11,2号地址写入22……设定高电平是写,低电平是读。

经过约50ns延迟,OUT_RAM输出的数据与DATA中预设数据一致。

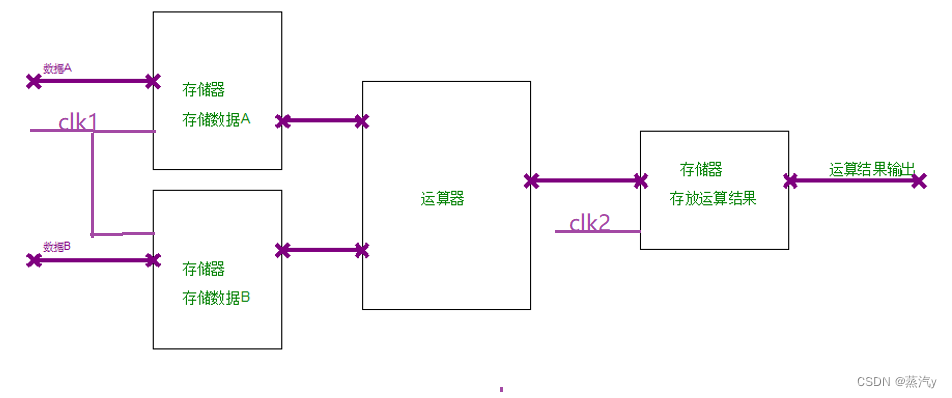

三、超简易CPU(在运算器前后端加存储器)

1. CPU模块图

2. 设计CPU

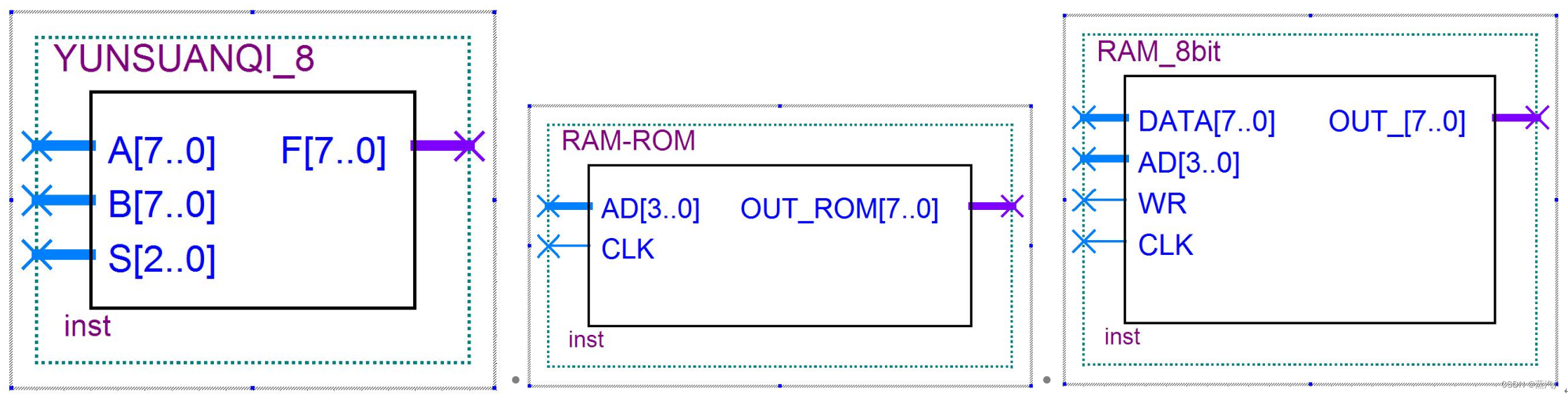

(1)将运算器、RAM和ROM模块化

打开设计的运算器、RAM和ROM文件,点file然后点create/update,然后create symbol files for current file,产生bsf文件,就是运算器、RAM和ROM的模块化原件。

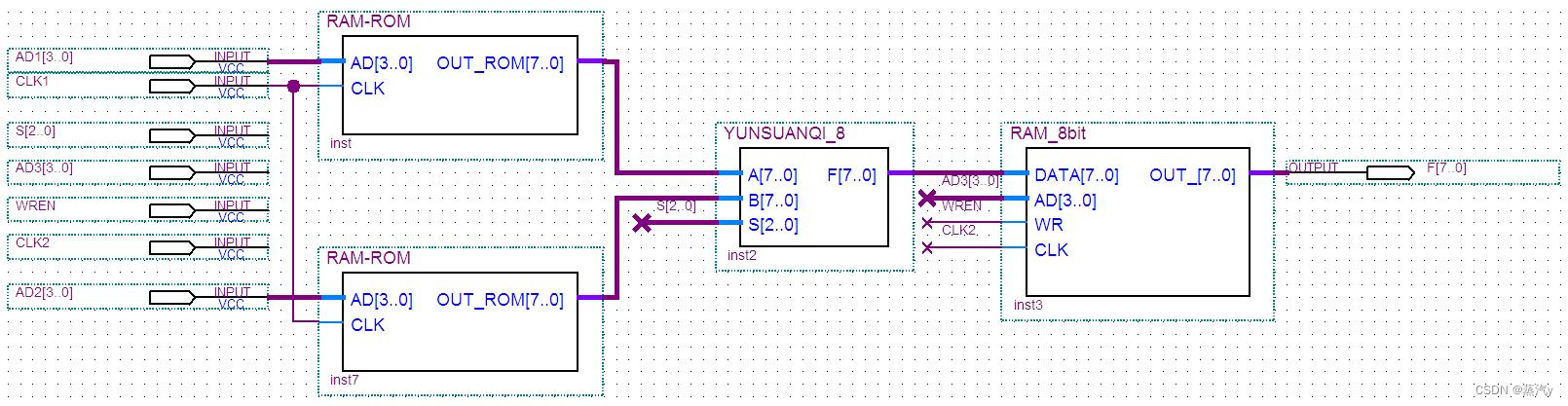

(2)根据模块图连接电路

设计输入和输出: AD1:存储器ROM1的数据存储地址;

AD2:存储器ROM1的数据存储地址;

CLK1:ROM的时钟脉冲;

S:选择运算器ALU的运算方式;

AD3:存储器RAM的数据存储地址;

WREN:存储器RAM的写信号;

CLK2::RAM的时钟脉冲;

F:输出运算的数据。

连接电路。

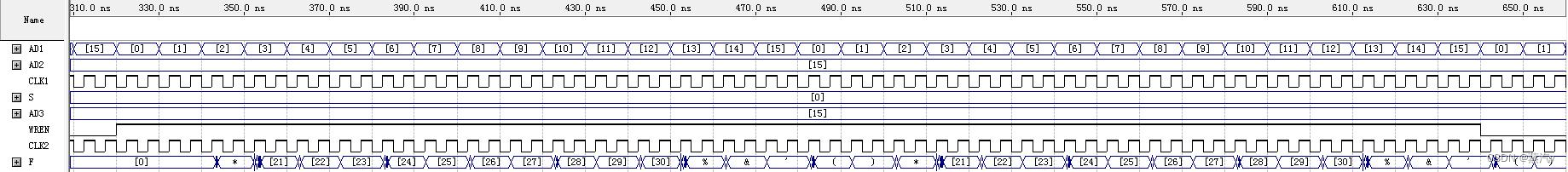

3. 功能仿真

设计AD1每10ns换一个地址;AD2保持[15];S选择[0],做加法运算;AD3保持[15];WREN周期为320ns;CLK1和CLK2周期为5ns。

经过约30ns延迟,F输出的数据与AD1中预设数据加上[15]中的数据运算结果一致。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?