前面几篇文章已经详细介绍了FPGA时序约束基础知识以及常用的时序约束命令,相信大家已经基本掌握了时序约束的方法。

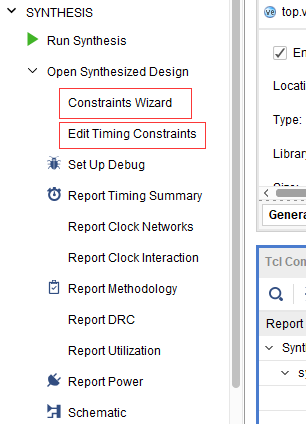

今天介绍一下,如何在Vivado中添加时序约束,Vivado添加约束的方法有3种:xdc文件、时序约束向导(Constraints Wizard)、时序约束编辑器(Edit Timing Constraints )

一、XDC文件

使用VIvado的“Source文件管理器”直接创建新的xdc文件或者添加已有的xdc文件。

具体步骤如下:

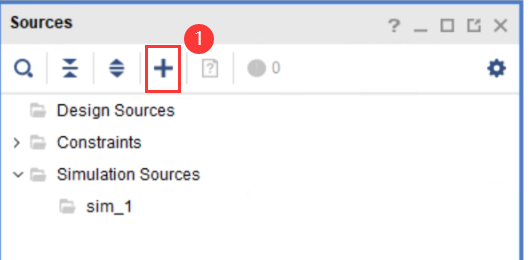

第一步:点击“+”

第二步:选择“Add or create constraints”,点击“next”

第三步:如果是添加文件则点击“Add Files”,如果是新建文件,则点击“Create File”

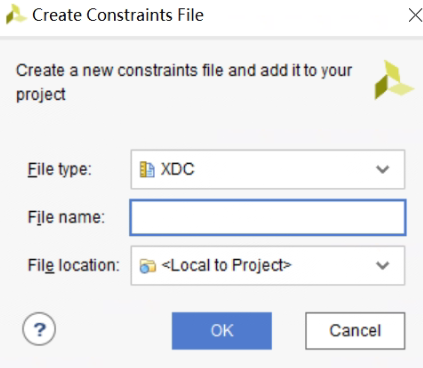

第四步:如果是新建文件,则输入文件名,点击“OK”,再点击“Finish”即可

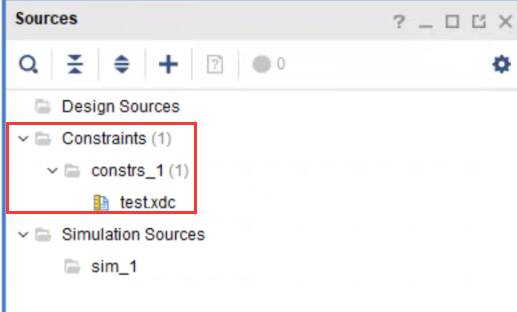

这样就可以,在source界面中的“Constraints”中看到新建的文件。

双击打开新建的xdc文件,写入约束语句即可。

创建XDC文件的方式很灵活,但在添加约束时需要谨慎一些,因为一些错误的约束可能会导致电路出错或性能下降。

二、时序约束向导(Constraints Wizard)

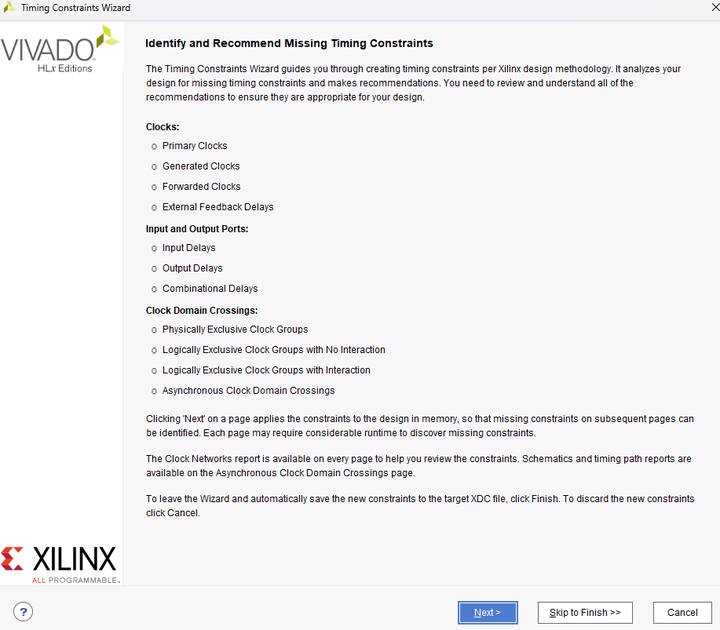

时序约束向导是Vivado提供的一个交互式添加约束工具。

可以帮助用户通过简单的设置界面来自动生成xdc文件中的TIMING约束。

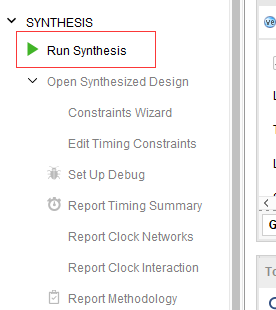

第一步:将HDL代码综合

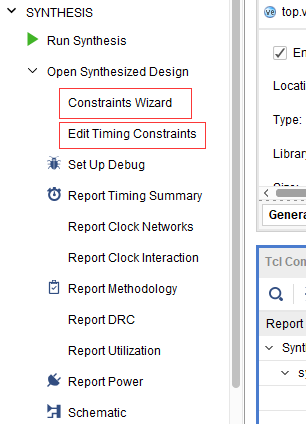

第二步:点击VIvado左边导航栏的“Synthesis”的“Constraints Wizard”。

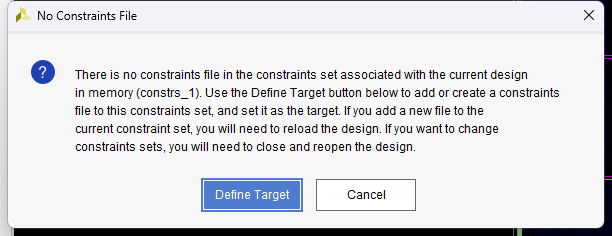

第三步:如果未创建xdc文件,vivado会提示新建新的xdc文件。

第四步:进入时序约束向导界面

时序约束向导是按照主时钟约束、衍生时钟约束、输入延迟约束、输出延迟约束、时序例外约束、异步时钟约束等的顺序来依次创建时钟约束的。

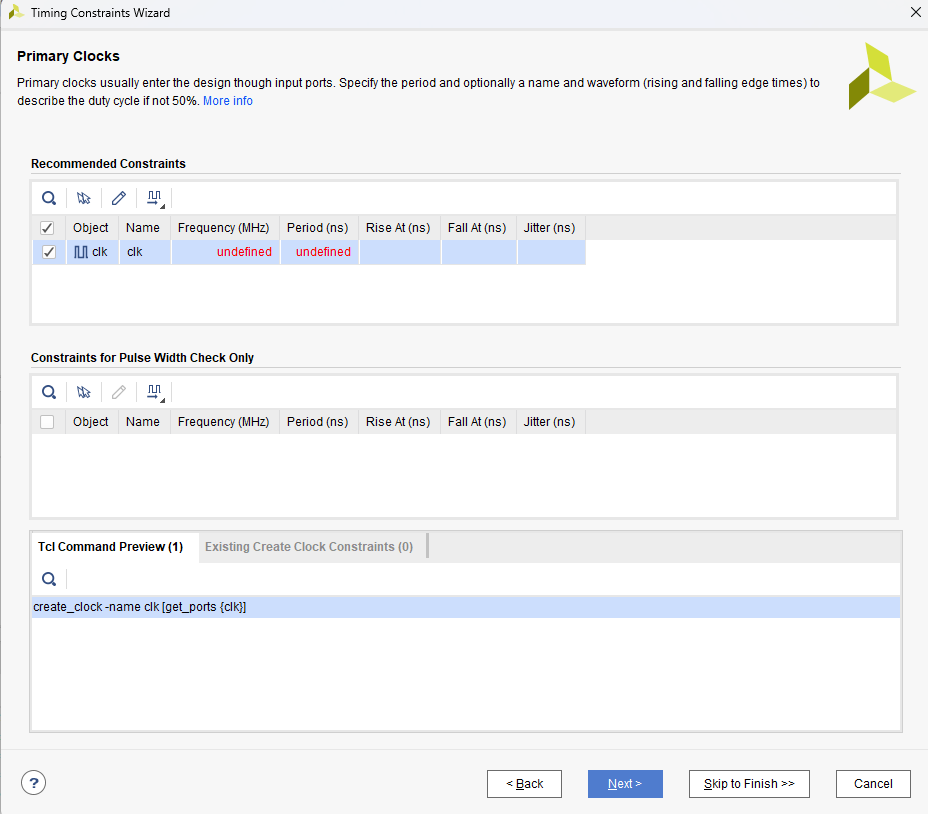

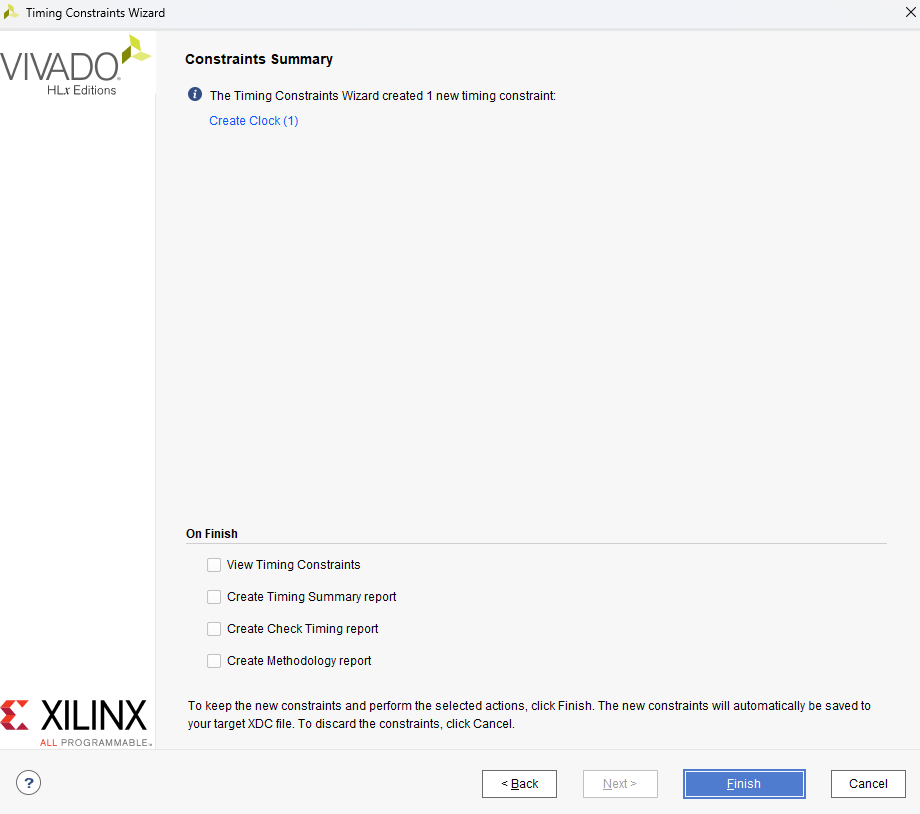

点击下一步,这里只演示填入主时钟,输入时钟周期,点击“skip to finish”。

最后点击finish,生成约束会自动保存到xdc文件中。

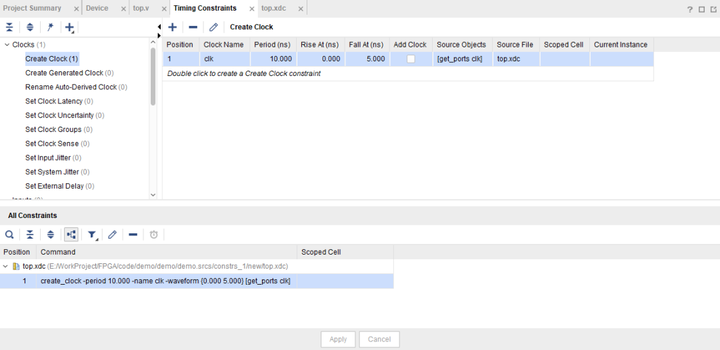

三、时序约束编辑器(Edit Timing Constraints )

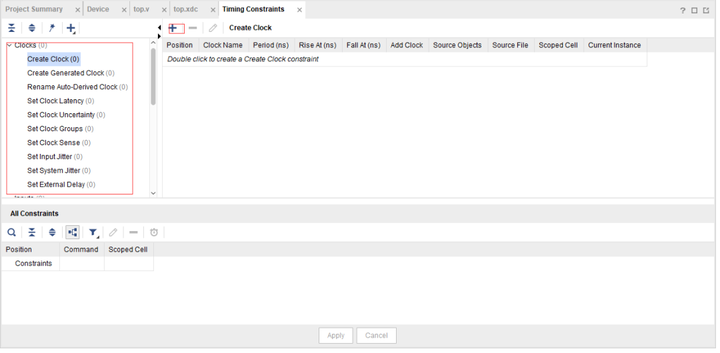

时序约束编辑器是Vivado中提供的可视化界面,用于修改编辑在xdc文件的时序约束,用户通过这个界面可以添加/删除约束、调整约束优先级及修改约束属性。

第一步:将HDL代码综合完后,点击VIvado左边导航栏的“Synthesis”的“Edit Timing Constraints”。

第二步:弹出编辑界面,如下图所示,先在左侧选择时序约束类型,再点击右侧窗口的“+”号,开始添加时序约束命令。

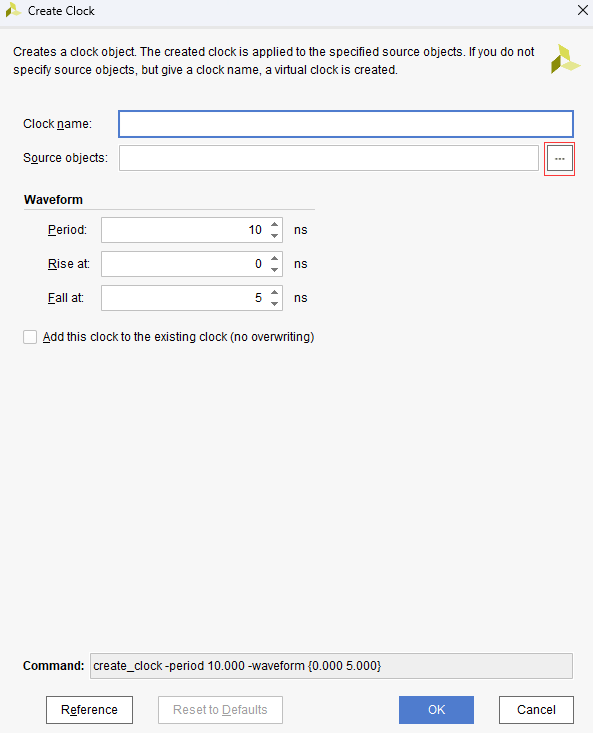

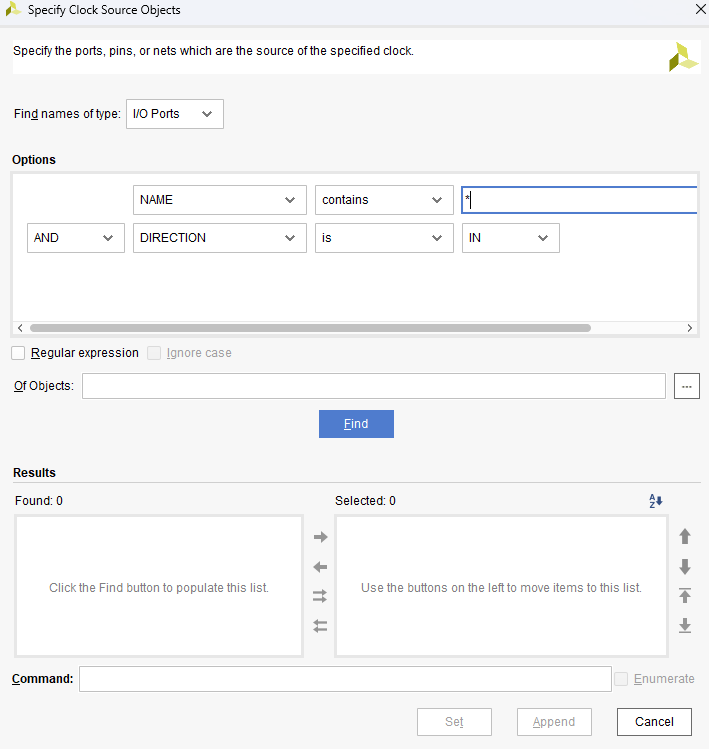

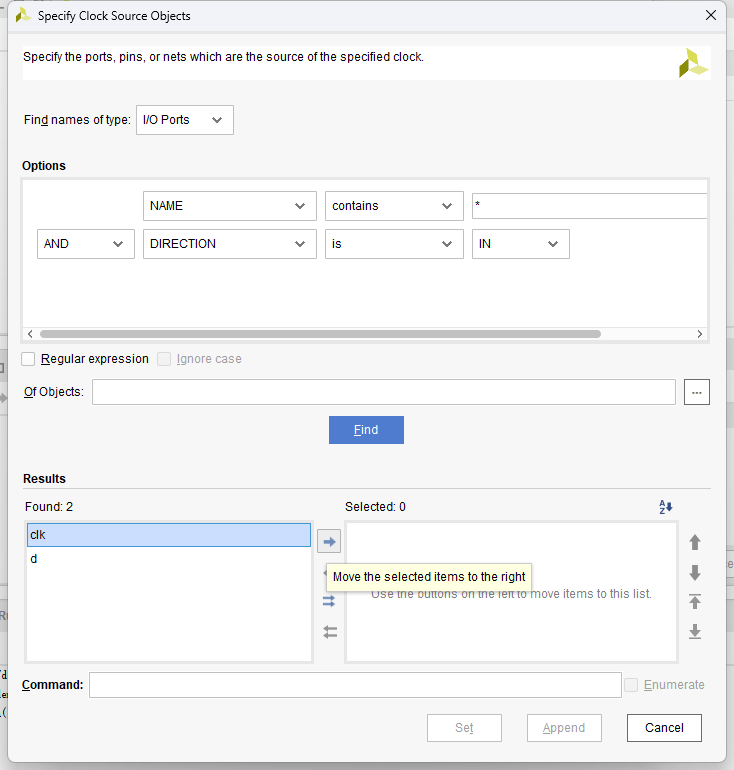

第三步,点击红框中“...”,打开搜索端口界面,再点击“find”按钮,自动弹出搜索到端口号。

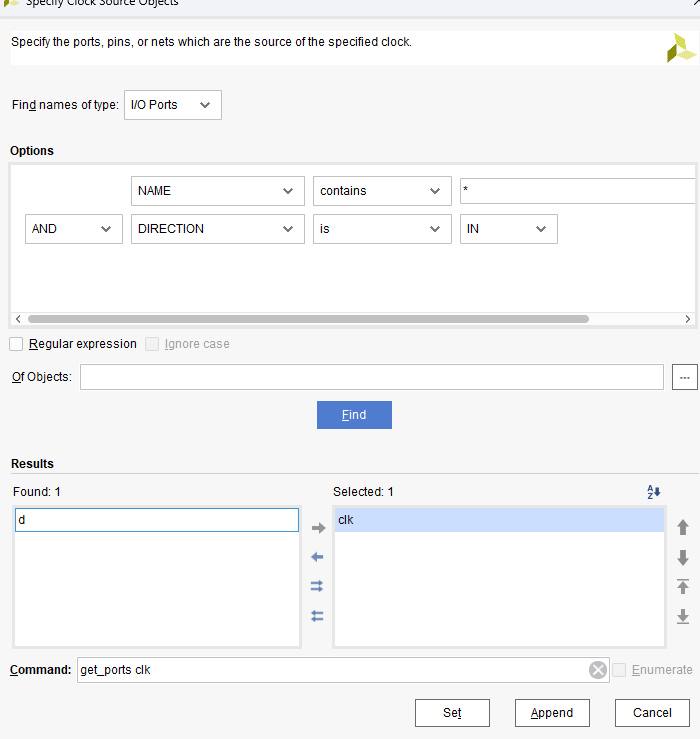

第四步:选中需要添加约束的端口,如“clk”,点击右侧箭头,移动到“选中窗口”,再点击“set”按钮。

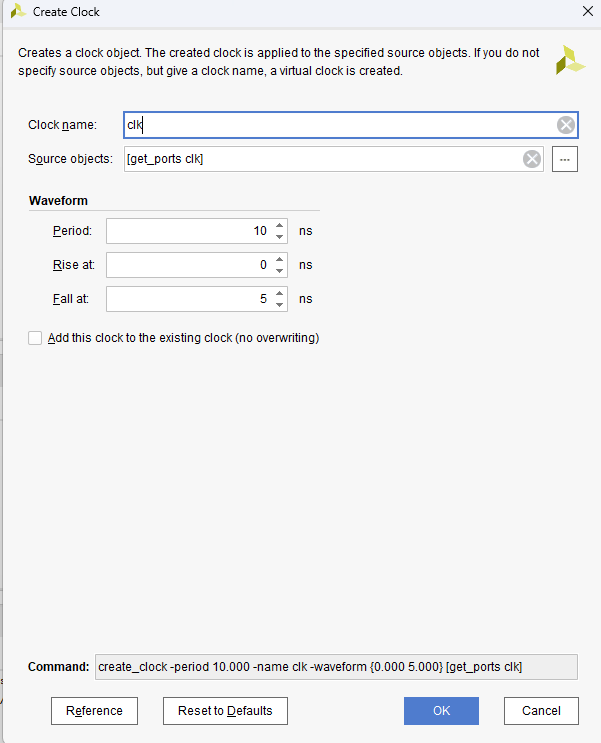

第五步:输入约束端口名,并设置时钟周期和占空比,点击“OK”。

第六步:按“ctrl+s”快捷键保存,最下方的预览窗口会显示设置的时钟约束,而且会自动保存到xdc约束文件中。

与直接xdc文件相比,时序约束编辑器提供了时序约束详细的分类和说明,更容易理解和使用。

四、总结

本文分享了Vivado中常用的添加时序约束的方法,大家可以按照自己的习惯和喜好选择方式即可。

本文将不断定期更新中,码字不易,点⭐️赞,收⭐️藏一下,不走丢哦

本文由FPGA入门到精通原创,有任何问题,都可以在评论区和我交流哦

您的支持是我持续创作的最大动力!如果本文对您有帮助,请给一个鼓励,谢谢。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?