目录

概述

本文主要从结构原理以及应用方面对 MPU 和 Cache 进行分析,通过对cache相关知识体系的学习,以Cache 有基本的了解。便于在具体的实际应用中, 使用带有一级 cache 的 MCU 时,避免出现一些不必要的错误。

1 Cache 及其原理

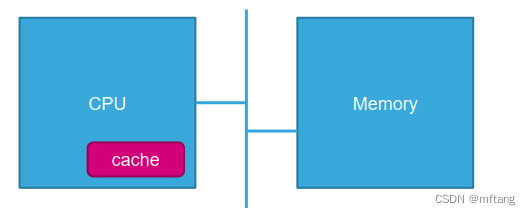

cache 是一种高速缓存,其位于CPU与memory之间的存储设备。

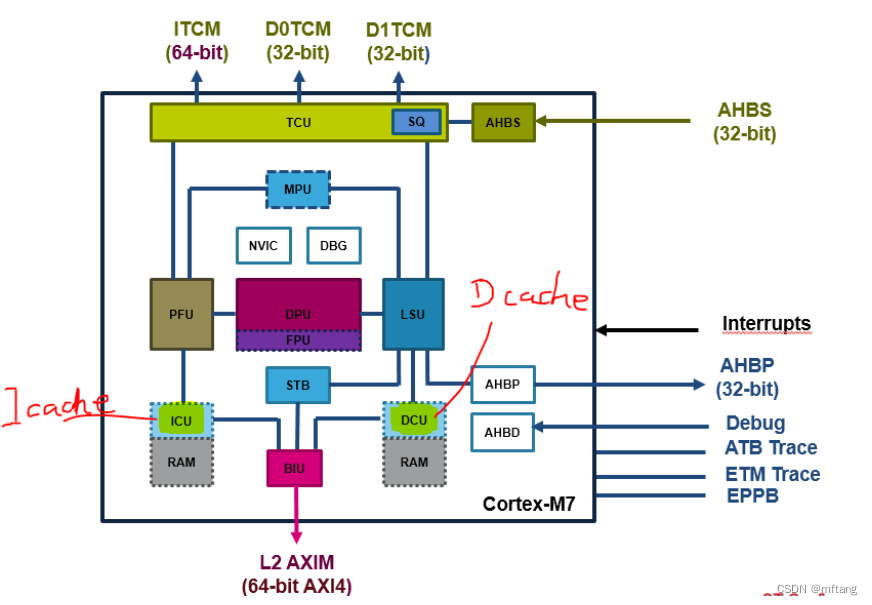

Cache是高速缓存,一般指的是 L1 cache,即和 Core 紧耦合的, 从 STM32F7 系列开始,基于 ARM cortex-M7 内核,增加了对 L1 Cache 的支持。

Cache分为两类:

1)指令 Cache(I-cache)

2)数据 Cache(D-cache)

从上图片可以看出来,无论是指令 Cache(I-cache)还是数据 Cache(D-cache), 一旦使能之后,

就分别与 Core 的 prefetch unit(I-cache)和 load-store unit(D-cache)相连。

Cache的特点:

以 D-cache 为例, 因为直接与 LSU 相连,访问速度会比直接访问 SRAM 或外部 RAM 快很多, 只要保证 cache 有足够高的命中率(由 cache 策略保证), 尽量少的 cache miss, 读/写的速度会有比较大的提高。

2 结构及策略

2.1 Cache类型

1)指令Cache

2)数据Cache

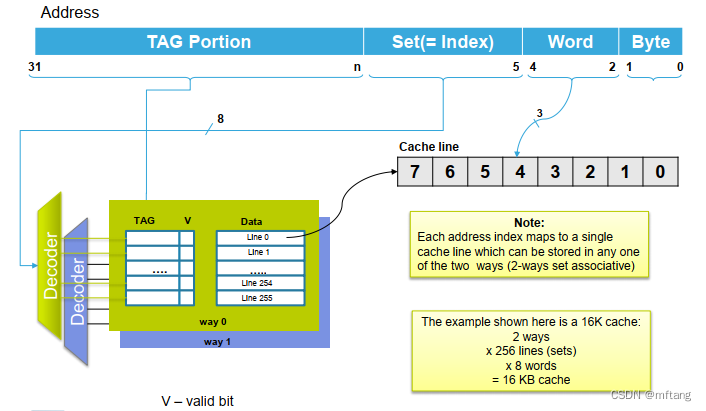

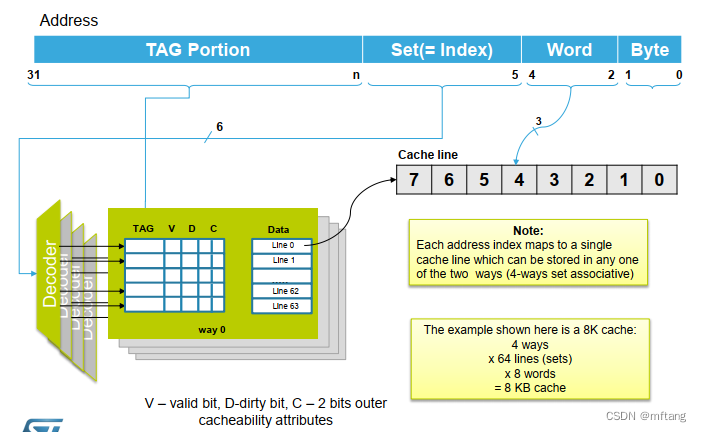

2.2 Cache实例

同样这里以 D-cache 为例, 看一下 D-cache 的构成:包括 Address 和 cache-line, Address 表明其地址

本文详细探讨了Cache的工作原理、不同类型,以及与MPU的交互,重点介绍了Cache一致性问题,特别是在写操作和DMA访问时可能出现的冲突,通过实例分析了配置和解决策略。

本文详细探讨了Cache的工作原理、不同类型,以及与MPU的交互,重点介绍了Cache一致性问题,特别是在写操作和DMA访问时可能出现的冲突,通过实例分析了配置和解决策略。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1103

1103

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?