前言

在刚开始接触进行前端RTL代码设计的时候我遇到一个问题,我不是很清楚我写下的每一句代码对应的逻辑深度与cell count值,这令我很难精准的在设计初期进行逻辑规划和方案优化。

所以呢在我初步具备单独综合的能力之后,就像为之前的自己汇总一下各种操作的逻辑深度和cell count,先从乘法器开始。

过程

简单说就是综合这样一段代码,提取timing和cell数,然后反复修改参数~

module test #(

parameter WIDTH = 32

)(

input clk,

input rst_n,

input [WIDTH -1:0] in_data1,

input [WIDTH -1:0] in_data2,

output [WIDTH -1:0] out_data

);

assign out_data = in_data1 * in_data2;

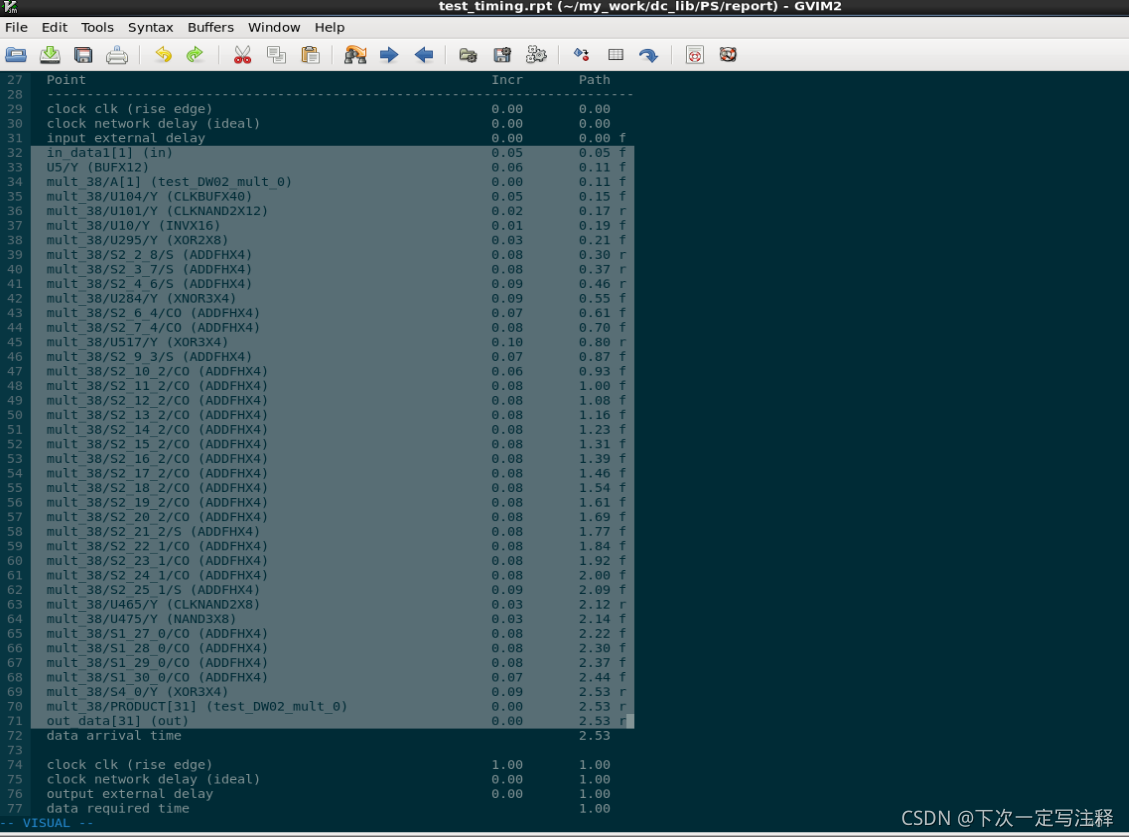

endmoduletiming我并不分关心时序因为这个跟库、约束、工艺等方方面面关联太多了,我需要的是逻辑深度如下面这就是40级逻辑深度:

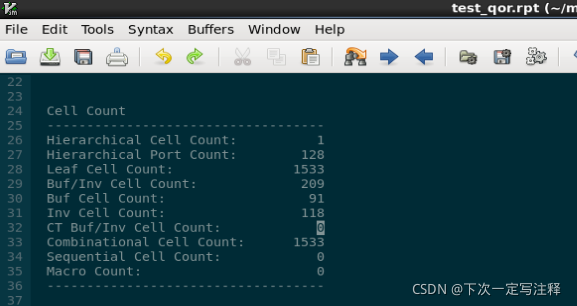

同样看area也没有意义,只需要统计cell cout就是下面这个值:

统计结果

C = A * B

| 输入位宽1 | 输入位宽2 | 输出位宽 | 逻辑深度 | cell count |

| 32 | 32 | 64 | 56 | 3056 |

| 32 | 32 | 32 | 38 | 1533 |

| 16 | 16 | 32 | 31 | 758 |

| 16 | 16 | 16 | 20 | 362 |

| 8 | 8 | 16 | 22 | 231 |

| 8 | 8 | 8 | 16 | 107 |

| 4 | 4 | 8 | 13 | 59 |

| 4 | 4 | 4 | 5 | 26 |

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?