1. 功耗分类

1.1 浪涌电流

浪涌电流指器件上电时产生的最大瞬时输入电流,它在应用中也称为启动电流。基于SRAM的FPGA也有很突出的浪涌电流,因为上电时这些期间没有配置,需要从外部存储器中下载数据来配置其编程资源

1.2 静态功耗

静态功耗也称为待机功耗,包含有电路中晶体管的漏电流所导致的功耗

1.3 动态功耗

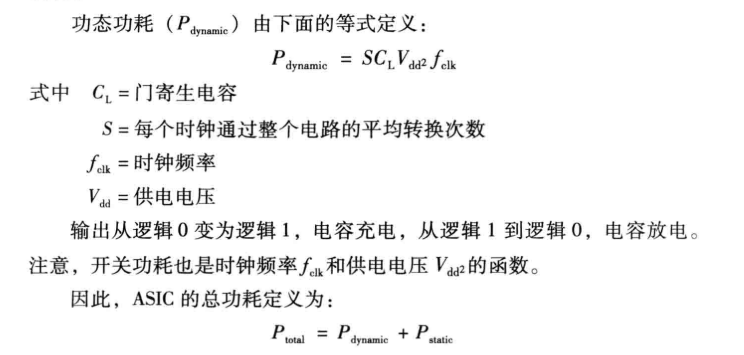

动态功耗也叫开关功耗,是门电路输出切换时,由逻辑转换所引起的功耗

2. 结构级降低功耗技术

- 高级门控时钟

- 动态电压频率调节(DVFS) :读频率不敏感的应用降低时钟频率和供电电压

- 基于缓存的系统体系结构:读大多数DSP应用,FFT算法要求频繁访问系统存储器的数据,如果在系统存储器和处理器之间增加缓存,可以极大地提高FFT的能效

- 使用对数系统比使用线性系统更好

- 异步时钟设计

- 电源门控

- 多阈值电压:高阈值电压单元较慢,但是漏电较少

- 多电压供电

3. 寄存器级RTL降低功耗

-

用格雷码编码最适合低功耗设计,因为格雷码在状态跳转时只会有一个寄存器发生翻转

-

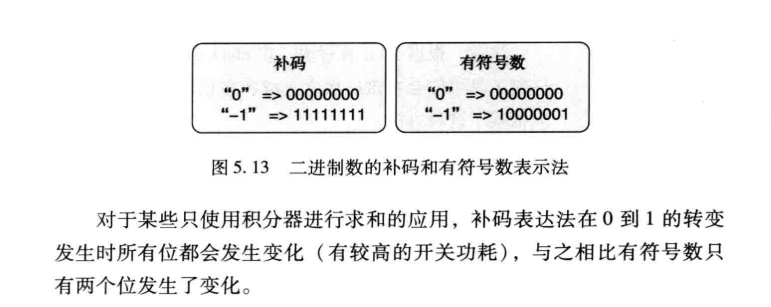

用有符号数代替补码表示

-

用独热码表示多路选择器

-

用行波计数器组成等效计数器

4. 硬件优化

- 版图优化,长布线会增加功耗

- 减少氧化层的厚度

5.低功耗技术小结

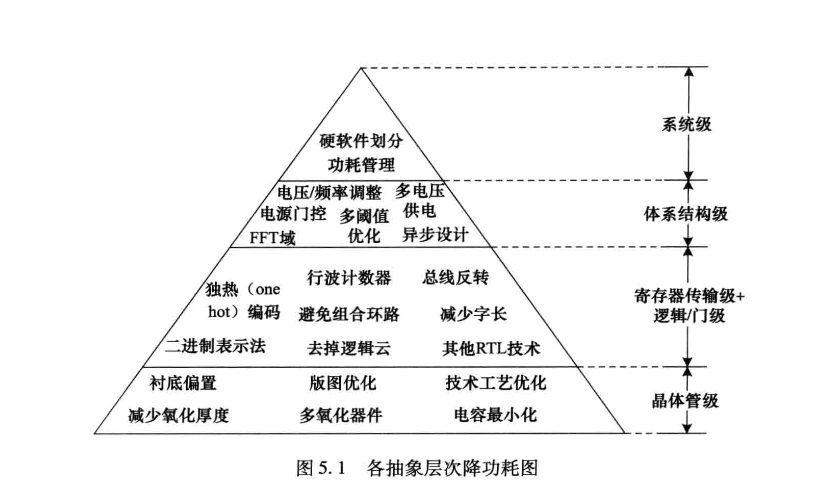

在系统级,逻辑级和物理级进行优化,层次越高对功耗降低越有效

- 在系统级优化主要包括1. 多电压供电;2.门控时钟;3.异步设计;4.多阈值电压供电;

- 在寄存器级优化主要包括1.在状态机编码时采用格雷码;2. 用有符号数替代补码表示;3. case语句作选择信号时用独热码,输出辉更快,更稳定

- 物理级,主要是通过1.提高工艺;2. 版图优化

2188

2188

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?