AXI 的英文全称是 Advanced eXtensible Interface,即高级可扩展接口,它是 ARM 公司所提出的AMBA(Advanced Microcontroller Bus Architecture)协议的一部分。AXI 协议就是描述了主设备和从设备之间的数据传输方式,在该协议中,主设备和从设备之间通过握手信号建立连接。

AXI 协议是一种高性能、高带宽、低延迟的片内总线,具有如下特点:

总线的地址/控制和数据通道是分离的;

支持不对齐的数据传输;

支持突发传输,突发传输过程中只需要首地址;

具有分离的读/写数据通道;

支持显著传输访问和乱序访问;

更加容易进行时序收敛。

在数字电路中只能传输二进制数 0 和 1,因此可能需要一组信号才能高效地传输信息,这一组信号就组成了接口。AXI4 协议支持以下三种类型的接口:

AXI4:高性能存储映射接口。

AXI4-Lite:简化版的 AXI4 接口,用于较少数据量的存储映射通信。

AXI4-Stream:用于高速数据流传输,非存储映射接口。

AXI4 协议支持突发传输,主要用于处理器访问存储器等需要指定地址的高速数据传输场景。AXI-Lite为外设提供单个数据传输,主要用于访问一些低速外设中的寄存器。而 AXI-Stream 接口则像 FIFO 一样,数据传输时不需要地址,在主从设备之间直接连续读写数据,主要用于如视频、高速 AD、PCIe、DMA 接口等需要高速数据传输的场合

AXI4 接口,它由五个独立的通道构成:

读地址

读数据

写地址

写数据

写响应

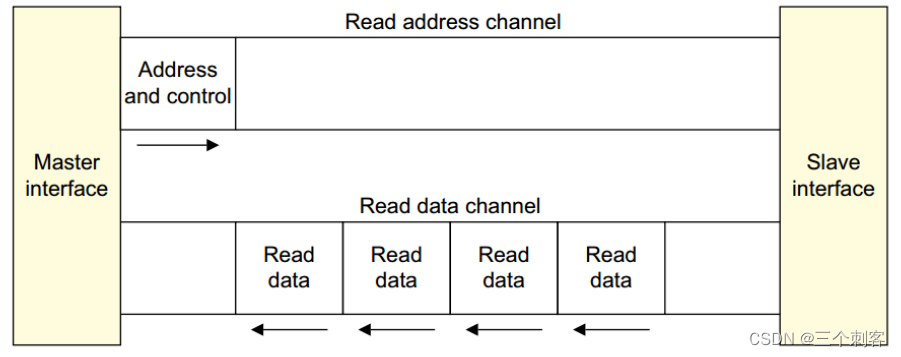

下面是使用读地址和读数据通道实现读传输过程的示意图:

在一个读传输过程中,主机首先在读地址通道给出读地址和控制信号,然后从机由读数据通道返回读出的数据。另外我们需要注意的是,这是一次突发读操作,主机只给出一个地址,从该地址连续突发读出四个数据。

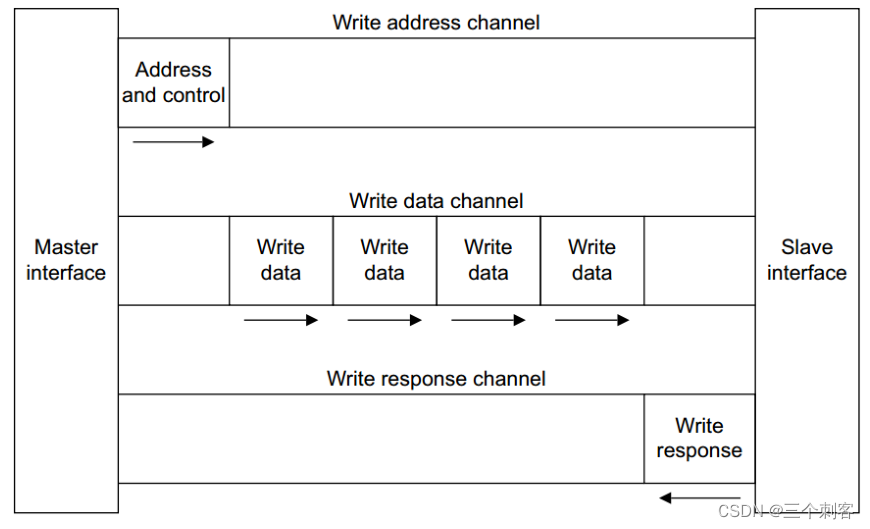

它用到了写地址、写数据和写响应三个通道。主机在写地址通道给出写地址和控制信号,然后在写数据通道连续突发写四个数据。从机在接收数据之后,在写响应通道给出响应信号。

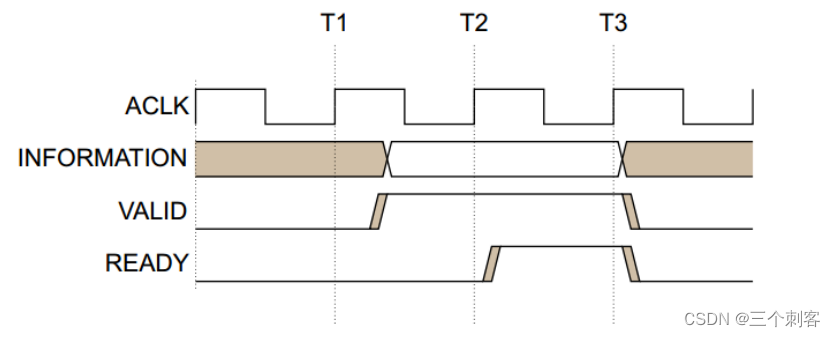

AXI 总线中的每个通道都包含了一组信息信号,还有一个 VALID 和一个 READY 信号。VALID 信号由源端(source)产生,表示当前地址或者数据线上的信息是有效的;而 READY 信号由目的端(destination)产生,则表示已经准备好接收地址、数据以及控制信息。VALID 和 READY 信号提供了 AXI 总线中的握手机制,如下图所示:

ACLK 为时钟信号,在 AXI 协议中,所有的输入信号都在是 ACLK 的上升沿采样,所有的输出信号必须在 ACLK 的上升沿之后才能改变。在 T1 之后,源端将 VALID 拉高,表明 INFORMATION信号线上传输的是有效的地址、数据或者控制信息。目的端在 T2 之后将 READY 拉高,表明它已经准备好接收数据,此时源端必须保持 INFORMATION 数据稳定不变,直到 T3 时刻进行数据传输。

需要注意的是,源端不允许等目的端的 READY 信号拉高之后,才将 VALID 信号置为有效状态。而且,一旦 VALID 拉高,源端必须保持其处于有效状态,直至成功握手(在时钟上升沿检测到 VALID 和 READY同时为有效状态)。

2042

2042

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?