adder.xdc 约束条件 是不需要变动的

lcd_module.dcp 是 LCD 触摸屏调用接口也不需要变动

adder.v文件

module adder(A,B,Cin,S,Cout);

parameter N=32;

input wire [N-1:0] A;

input wire [N-1:0] B;

input wire Cin;

output wire [N-1:0] S;

output wire Cout;

wire [N-2:0]C;

FullAdder FA0 (A[0],B[0],Cin,S[0],C[0]);

FullAdder FA1 (A[1],B[1],C[0],S[1],C[1]);

FullAdder FA2 (A[2],B[2],C[1],S[2],C[2]);

FullAdder FA3 (A[3],B[3],C[2],S[3],C[3]);

FullAdder FA4 (A[4],B[4],C[3],S[4],C[4]);

FullAdder FA5 (A[5],B[5],C[4],S[5],C[5]);

FullAdder FA6 (A[6],B[6],C[5],S[6],C[6]);

FullAdder FA7 (A[7],B[7],C[6],S[7],C[7]);

FullAdder FA8 (A[8],B[8],C[7],S[8],C[8]);

FullAdder FA9 (A[9],B[9],C[8],S[9],C[9]);

FullAdder FA10 (A[10],B[10],C[9],S[10],C[10]);

FullAdder FA11 (A[11],B[11],C[10],S[11],C[11]);

FullAdder FA12 (A[12],B[12],C[11],S[12],C[12]);

FullAdder FA13 (A[13],B[13],C[12],S[13],C[13]);

FullAdder FA14 (A[14],B[14],C[13],S[14],C[14]);

FullAdder FA15 (A[15],B[15],C[14],S[15],C[15]);

FullAdder FA16 (A[16],B[16],C[15],S[16],C[16]);

FullAdder FA17 (A[17],B[17],C[16],S[17],C[17]);

FullAdder FA18 (A[18],B[18],C[17],S[18],C[18]);

FullAdder FA19 (A[19],B[19],C[18],S[19],C[19]);

FullAdder FA20 (A[20],B[20],C[19],S[20],C[20]);

FullAdder FA21 (A[21],B[21],C[20],S[21],C[21]);

FullAdder FA22 (A[22],B[22],C[21],S[22],C[22]);

FullAdder FA23 (A[23],B[23],C[22],S[23],C[23]);

FullAdder FA24 (A[24],B[24],C[23],S[24],C[24]);

FullAdder FA25 (A[25],B[25],C[24],S[25],C[25]);

FullAdder FA26 (A[26],B[26],C[25],S[26],C[26]);

FullAdder FA27 (A[27],B[27],C[26],S[27],C[27]);

FullAdder FA28 (A[28],B[28],C[27],S[28],C[28]);

FullAdder FA29 (A[29],B[29],C[28],S[29],C[29]);

FullAdder FA30 (A[30],B[30],C[29],S[30],C[30]);

FullAdder FA31 (A[31],B[31],C[30],S[31],Cout);

endmodule

module FullAdder(A,B,CarryIn,Sum,CarryOut);

input wire A;

input wire B;

input wire CarryIn;

output wire Sum;

output wire CarryOut;

assign Sum=A^B^CarryIn;

assign CarryOut=(A&B)|(A&CarryIn)|(B&CarryIn);

endmodule

testbench

module testbench;

reg clk;

reg [31:0] A;

reg [31:0] B;

reg Cin;

wire Cout;

wire [31:0] S;

adder adder_0(A,B,Cin,S,Cout);//实例化

always #10 clk=~clk;

initial //初始化仿真

begin

clk=1'b0;

A=32'h232234;B=32'h3013121;Cin=1'b0;//32表位数,h 16进制

#100;A=32'h543;B=32'h171234;Cin=1'b0;

#100;A=32'h2554;B=32'h18122;Cin=1'b0;

#100;A=32'h3456;B=32'h193112;Cin=1'b0;

#100;A=32'h4765;B=32'h20321;Cin=1'b0;

#100;A=32'h5784;B=32'h30412;Cin=1'b1;

#100;A=32'h622;B=32'h40421;Cin=1'b1;

#100;A=32'h7999;B=32'h5032;Cin=1'b1;

#100;A=32'h8532;B=32'h630;Cin=1'b1;

//其他测试用例

$finish;

end

endmodule

adder_display.v 👇

module adder_display(

//时钟与复位信号

input clk,

input resetn, //后缀n表示低电平有效

//拨码开关,用于选择输入数 和 产生 cin(你试过的,动了之后结果多了1嘛)

input input_sel, //0 输入加数1, 1:输入加数2

input sw_cin,

//led灯显示cout

output led_cout,

//触摸屏相关借口,无需更改

output lcd_rst,

output lcd_cs,

output lcd_rs,

output lcd_wr,

output lcd_rd,

inout[15:0] lcd_data_io,

output lcd_bl_ctr,

inout ct_int,

inout ct_sda,

output ct_scl,

output ct_rstn

);

//--调用加法模块begin

reg [31:0] adder_A;

reg [31:0] adder_B;

wire adder_Cin;

wire [31:0] adder_S ;

wire adder_C;

adder adder_module(

//需要补充的部分

.A(adder_A),

.B(adder_B),

.Cin (adder_Cin ),

.S (adder_S),

.Cout (adder_Cout )

);

assign adder_Cin = sw_cin;

assign led_cout = adder_Cout;

//---加法模块end

//---------------------调用触摸屏模块begin--------------------//

//---实例化触摸屏begin

//这小节无需更改

reg display_valid;

reg [39:0] display_name;

reg [31:0] display_value;

wire [5 :0] display_number;

wire input_valid;

wire [31:0] input_value;

lcd_module lcd_module(

.clk (clk ), //10Mhz

.resetn (resetn ),

//调用触摸屏的接口

.display_valid (display_valid ),

.display_name (display_name ),

.display_value (display_value ),

.display_number (display_number),

.input_valid (input_valid ),

.input_value (input_value ),

//lcd触摸屏相关接口,不需要更改

.lcd_rst (lcd_rst ),

.lcd_cs (lcd_cs ),

.lcd_rs (lcd_rs ),

.lcd_wr (lcd_wr ),

.lcd_rd (lcd_rd ),

.lcd_data_io (lcd_data_io ),

.lcd_bl_ctr (lcd_bl_ctr ),

.ct_int (ct_int ),

.ct_sda (ct_sda ),

.ct_scl (ct_scl ),

.ct_rstn (ct_rstn )

);

//----实例化触摸屏end

//-----从触摸屏获取输入begin

//根据实际需要输入的数 修改此小节

//建议对每一个数的输入,编写单独一个always块

//input_sel 为0时,表 输入数为加数1即operand1

always @(posedge clk)

begin

if (!resetn)

begin

adder_A <= 32'd0;

end

else if (input_valid && !input_sel)

begin

adder_A <= input_value;

end

end

//input_sel 为1时,表 输入数为加数2即operand2

always @(posedge clk)

begin

if (!resetn)

begin

adder_B <= 32'd0;

end

else if (input_valid && input_sel)

begin

adder_B <= input_value;

end

end

//----从触摸屏获取输入end

//---输出到触摸屏显示begin

//根据需要显示的数修改此小节

//触摸屏44块区域,可显示44组 32位数据 区域从1开始编号1-44

always @(posedge clk)

begin

case(display_number)

6'd1 :

begin

display_valid <= 1'b1;

display_name <= "ADD_1";

display_value <= adder_A;

end

6'd2 :

begin

display_valid <= 1'b1;

display_name <= "ADD_2";

display_value <= adder_B;

end

6'd3 :

begin

display_valid <= 1'b1;

display_name <= "RESUL";

display_value <= adder_S;

end

default :

begin

display_valid <= 1'b0;

display_name <= 40'd0;

display_value <= 32'd0;

end

endcase

end

//-----输出到触摸屏显示end

//--------------------调用触摸屏模块end---------------------//

endmodule

一些学习:

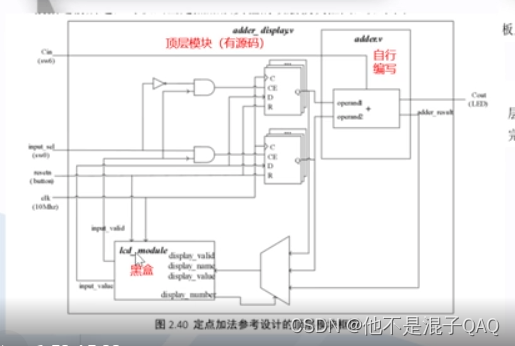

以全加器为基础,实现32位行波进位加法器。

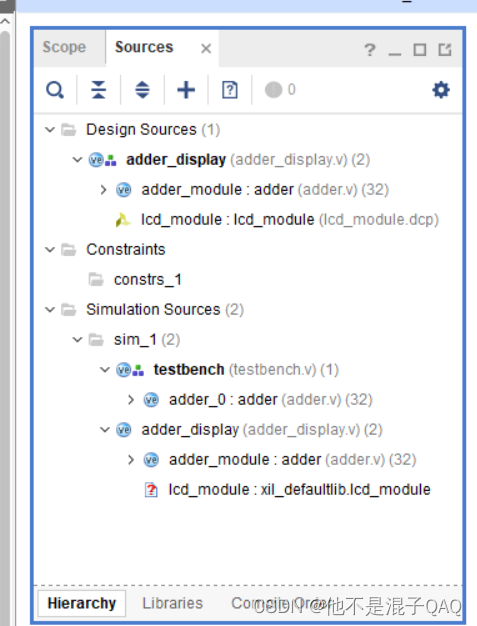

顶层模块adder_display 调用adder.v 也调用显示屏lcd_moudle

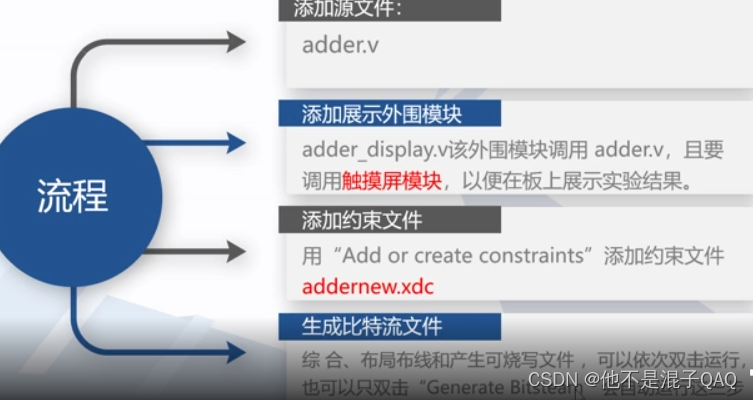

所谓约束文件就是将顶层模块的输入输出端口与FPGA板上的IO接口引脚绑定,以完成在板上的输入输出 约束文件 .xdc 这里是addernew.xdc

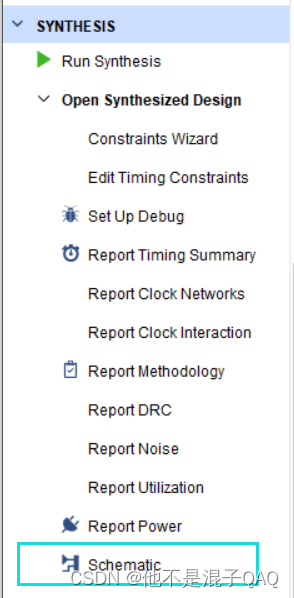

当你完成了一个设计之后,查看原理图,可以看下电路图(虽然我现在也看不懂。。

在这里呢哦

在这里呢哦

关于模块的调用可以看下 Verilog数字系统设计教程(第2版) 的p45页

1054

1054

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?