MIPI DSI

文章目录

概述

MIPI

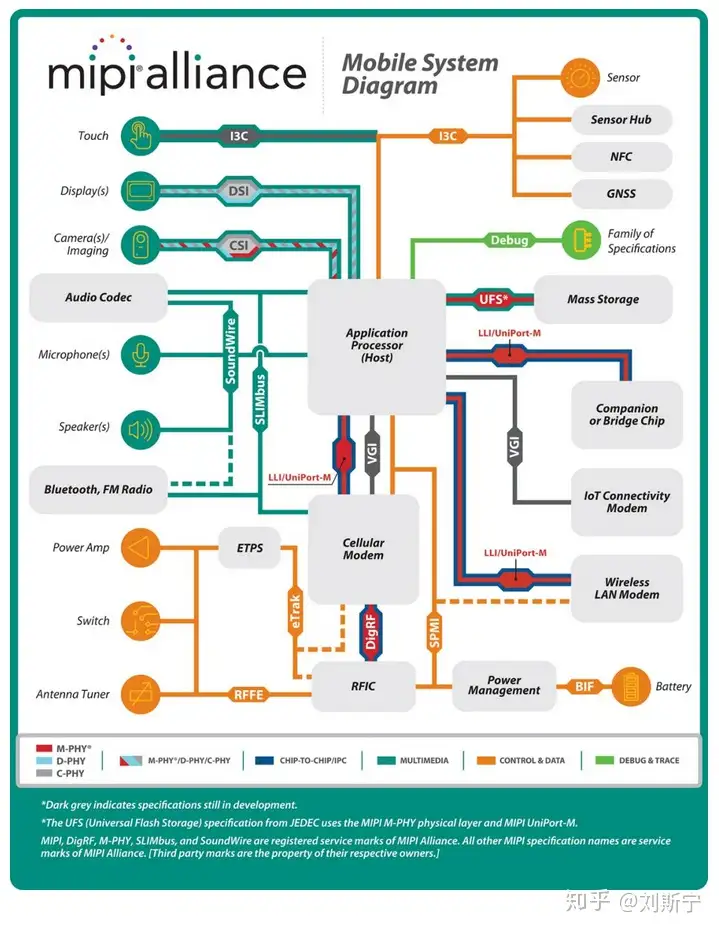

MIPI (Mobile Industry Processor Interface)即移动产业处理器接口,2003年由ARM、Nokia、ST和TI等公式成立的一个联盟,所以大家在看MIPI相关文档的时候长看到MIPI Aliance。MIPI 官方网址。当前MIPI联盟已经有很多成员, 比如ARM、ST、高通、TI、苹果、海思等,基本上囊括了主流的移动处理器生产厂家。

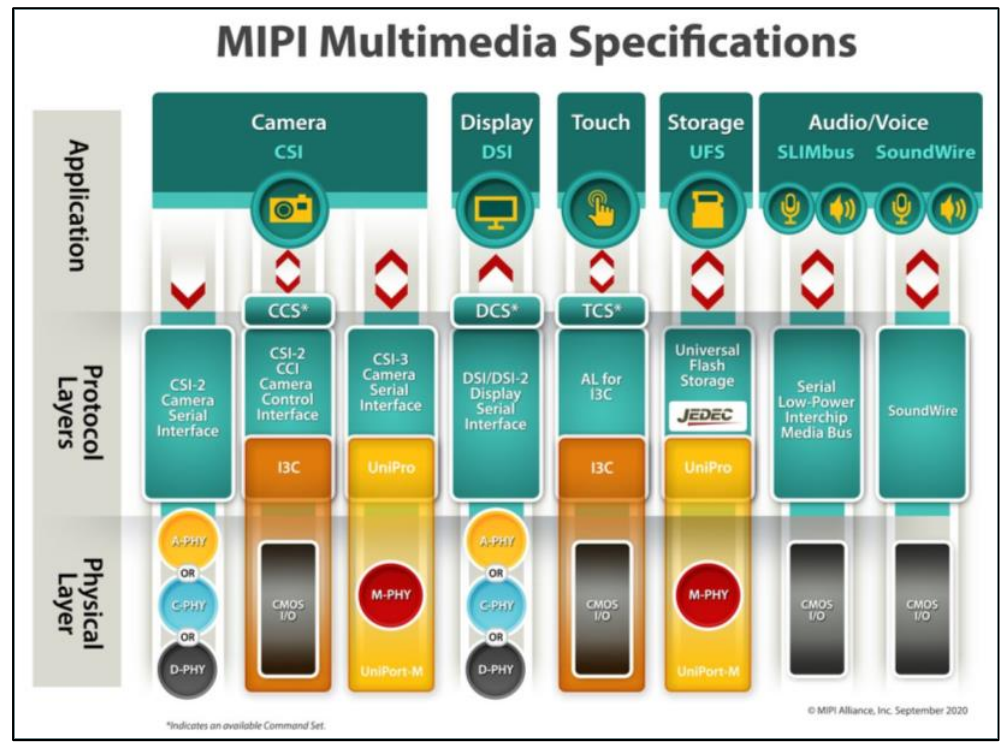

MIPI协议实际上是一系列接口的协议,基本囊括:液晶、摄像头,触摸屏,传感器,FLASH ,RF, Audio等手机里面的所有设备。

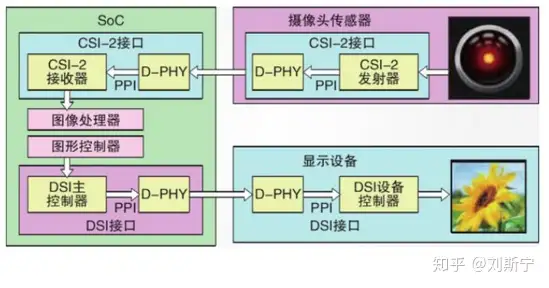

MIPI是一个比较新的标准,其规范也在不断修改和改进,目前比较成熟的接口应用有CSI(摄像头接口)和DSI(显示接口),分别针对Camera或Display应用,都有复杂的协议结构。MIPI CSI-2 和 MIPI CSI-3 是MIPI 摄像机接口最初标准的升级版本,这两个版本都在持续演进中。两个版本都具有高级的架构设计,为开发人员,制造商和最终的消费者提供更多选择和更大的价值,同时保持标准接口的优势。下图说明了CSI和DSI设备的典型应用场景。

MIPI DSI

液晶显示屏中所用的MIPI接口,其专业名称叫DSI,全称Display Serial Interface。顾名思义,该接口是指用于显示模块的一个串行接口,基于MIPI协议而产生,兼容DPI(显示像素接口,Display Pixel Interface)、DBI(显示总线接口,Display Bus Interface)和DCS(显示命令集,Display Command Set,就是移植液晶下发参数所用的那些命令了)。相对于一般的RGB接口,DSI有成本低,高速率的优势。

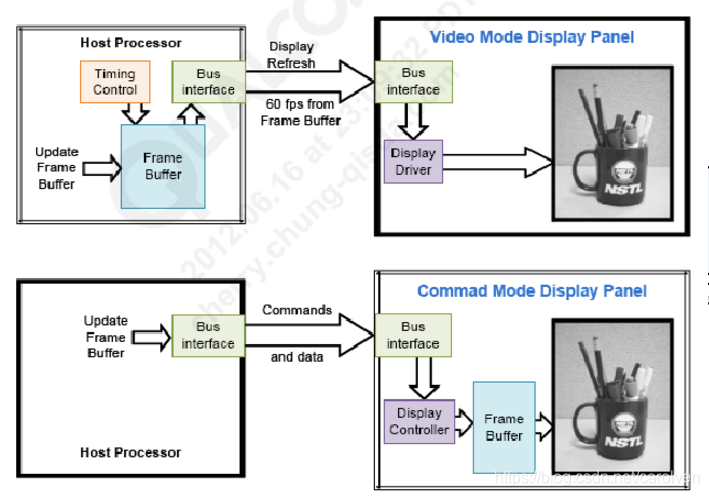

•DBI(Display Bus Interface, Display Pixel Interface), Parallel interfaces to display modules having display controllers and frame buffers。MIPI总线控制器使用显示命令报文来向显示器发送像素数据流。显示器应该有一个全帧长的帧缓冲器来存储所有的像素数据。一旦数据被放在显示器的帧缓冲器中,定时控制器就从帧缓冲器中取出数据,并自动把它们显示在屏幕上。MIPI总线控制器不需要定期刷新显示器。

DPI(Display Bus Interface, Display Pixel Interface), Parallel interfaces to display modules without on-panel display controller or frame buffer。类似RGB屏幕,需要不间断的提供刷新数据。

上面的是DPI,下面的是DBI

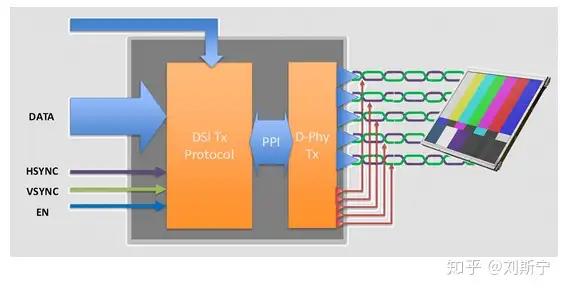

分层

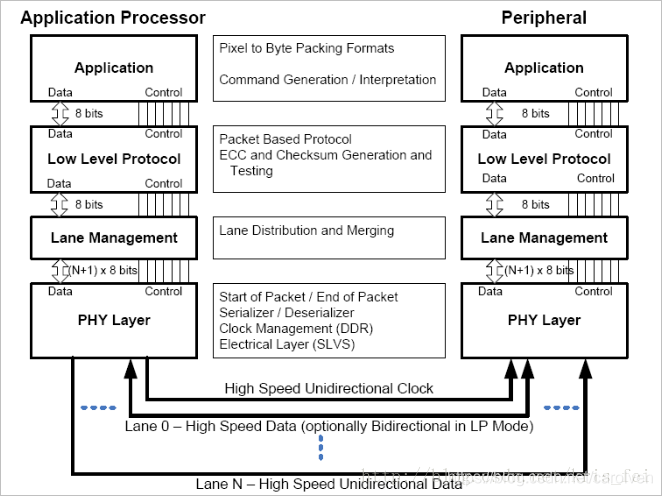

MIPI从下往上依次为物理层、通道管理层、协议层、应用层,四层各司其职,共同实现DSI协议。

物理层:硬件电路控制,将所有的数据转换为电平信号,以输出或者输入。这一层之间的连接就是DSI的接口连接了

通道管理层:对数据进行管理,将数据分给给Data通道或者从Data通道接收到后进行重组,以便交给下一层

协议层:对数据进行封包、检验等

应用层:初始化参数或者图像数据就在这一层发送或者接收。

下图是MIPI分层的直观说明:

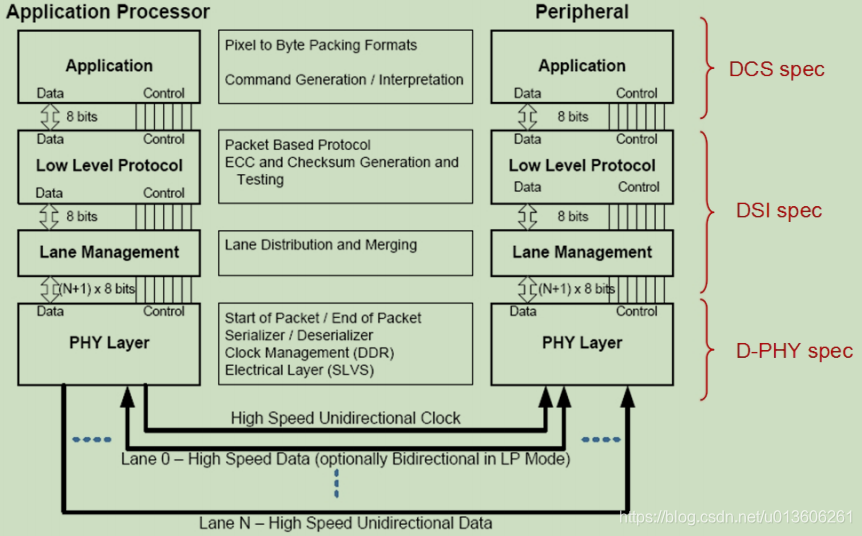

下图是MIPI -DSI的分层:

其中DCS层是指(Display Command Set)不同的屏,在应用层的命令;

DSI 层,规定了数据传输格式,数据的长帧和短帧格式,视频数据如何传输;

D-PHY层,物理接口。Lane的电平,时钟,高速传输和低速传输模式;

物理层

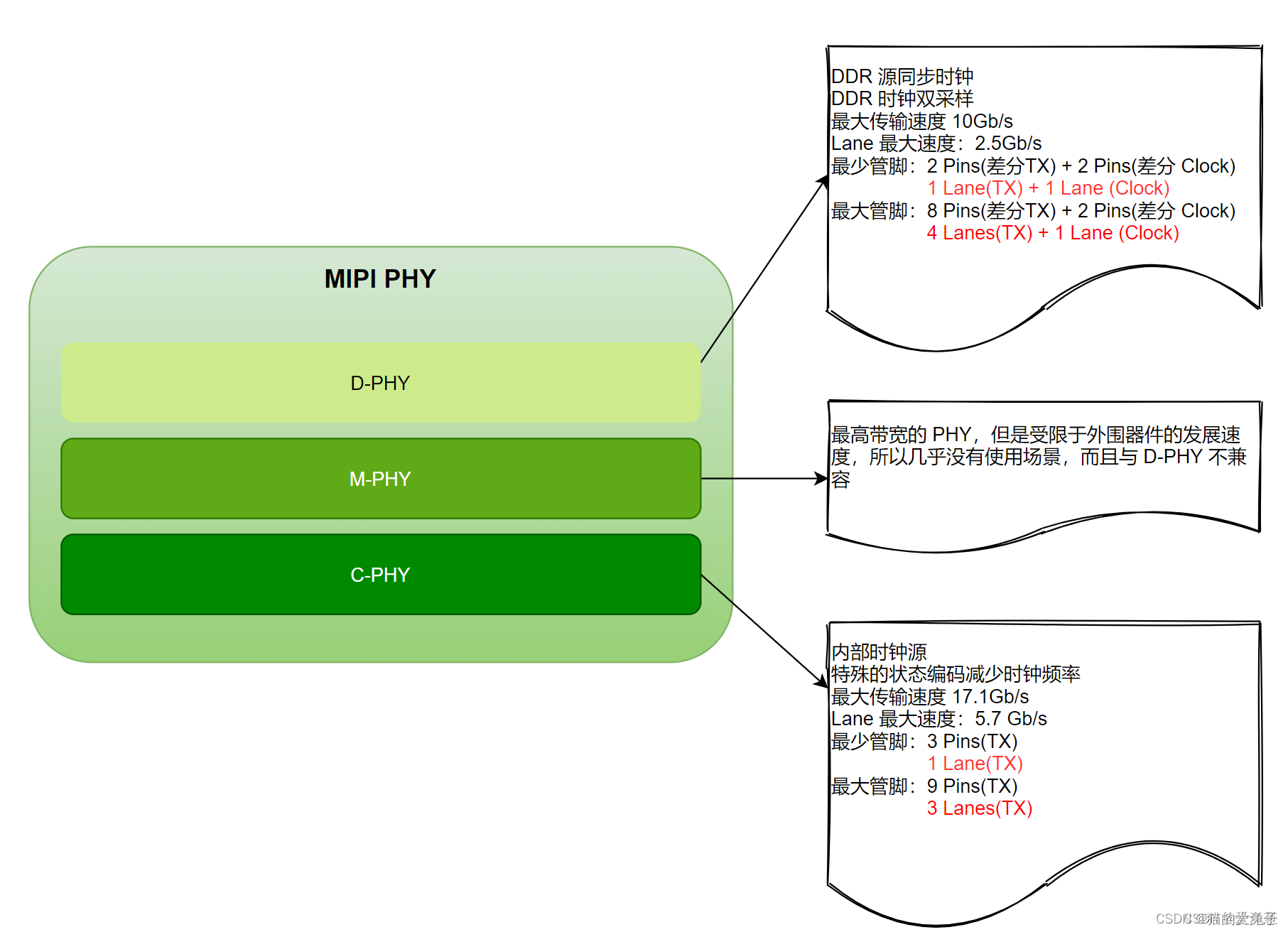

MIPI的物理层有 D-PHY, C-PHY 和 M-PHY几种格式。

1、D-PHY MIPI 简介

D-PHY的逻辑层主要是面向摄像头(CSI)、显示屏(DSI)等用途,D-PHY中的D是罗马数字500的意思,D-PHY最初版本是可以支持500Mbits/s。D-PHY采用差分信号传输方式(不全是差分,LP是单端传输),每条lane由2根信号线组成,分别是P和N,clock lane是必不可少的,data lane的数量可以根据数据传输的吞吐率来选择,至少要有一个data lane。

2、C-PHY MIPI简介

C-PHY类似于D-PHY,其逻辑层主要也是面向摄像头(CSI)、显示屏(DSI)等用途,C-PHY中的C指的是Channel-limited。C-PHY总共有3条lane,每条lane使用3根信号线,3条信号线彼此差分。C-PHY没有单独的clock,时钟信号是包含在通讯的时序中。

3、M-PHY MIPI简介

M-PHY支持所有芯片到芯片的应用,以及高性能的摄像头和内存应用。M-PHY中支持的芯片到芯片应用协议包括DigRF、LLI,以及用于高性能相机应用的CSI-3等。M-PHY使用嵌入式时钟。当前很少用到,比较超前。

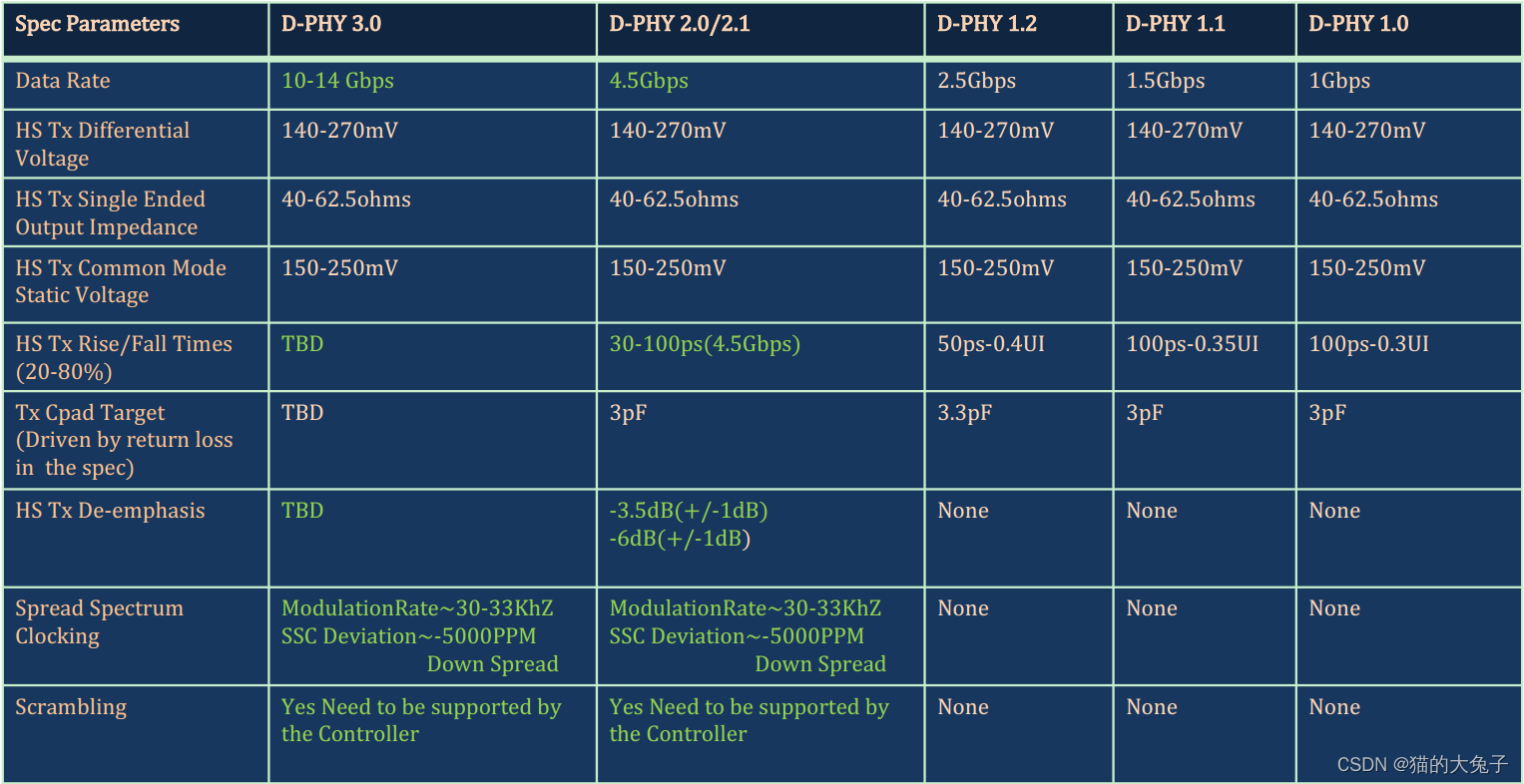

本篇介绍的是 D-PHY,在 MIPI 的官网上可以看到 D-PHY 其实也分了很多的版本,也就是说,现在 MIPI 联盟中,发展了几个 PHY 的标准,而这几个 PHY 的标准又各自有不同的版本。具体如下:

目前MIPI DSI中常见的还是D-PHY,下面的介绍的都是D-PHY

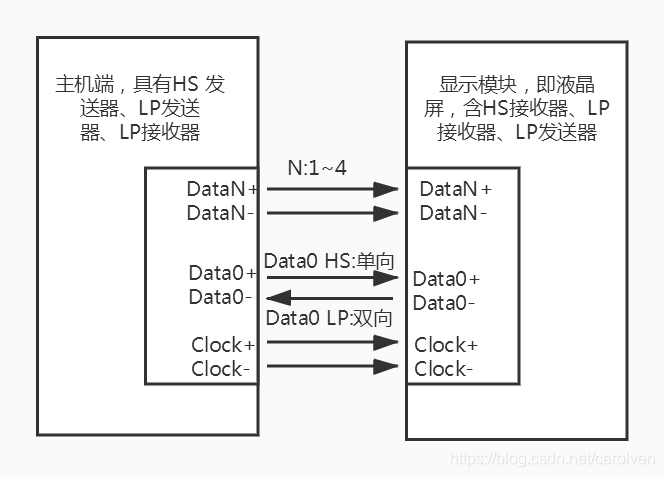

D-PHY的配置包括一个单向的clock lane和一个或多个data lanes(最多4个data lanes)。data lanes 有两种类型:

(1)双向口:能双向传输

(2)单向口:只能单向传输

所有的data lanes都支持高速传输和正向时的低速传输 。

双向的data lanes 必须包含下面的一个或两个反相通信功能:

(1)High-Speed Reverse Data Communication :高速反相数据传输

(2)Low-Power Reverse Escape Mode (including or excluding LPDT):反向低功耗 Escape Mode模式(包含或只有低功耗数据传输)

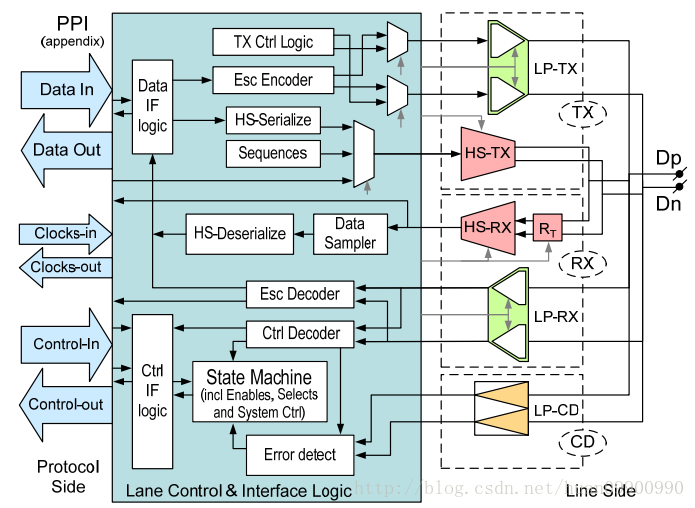

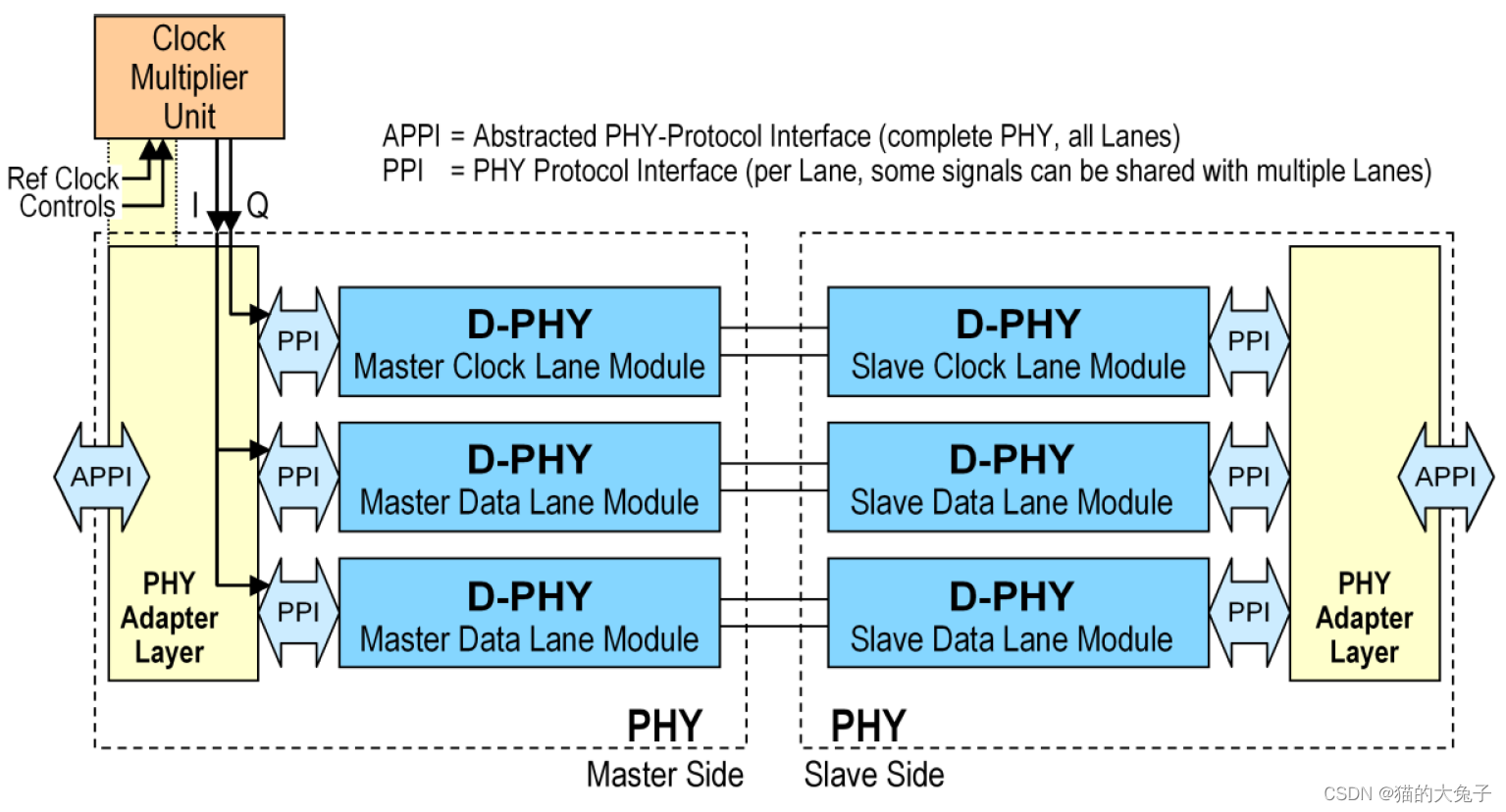

下图是一个通用的Lane Module 内部结构图

其主要由:

- 一个高速收发模块(HS-TX,HS-RX),

- 一个单端低功耗收发模块(LP-TX,LP-RX)

- 一个LP-CD(Contention Detection)低速通信冲突检测,因为是半双工通信,需要检查冲突;

- 控制和接口逻辑模块(Lane Control &Interface Logic)组成。

D-PHY在使用的过程中,类似于其他总线也有Master和Slave之分,如在用Soc驱动LCD时使用D-PHY MIPI信号,这时Soc就是Master,LCD就是Slave。

- Clock Lane是单向的,由Master端发向Slave端。

- Data Lane 可以是单向或双向

对于半双工操作,反向带宽是正向带宽的四分之一。

D-PHY Lane 的模式分为了 2 种,分别是High-Speed 和 Low-Power ,在传输的时候,信号的幅值也不一样。

High-Speed 用于高速的数据传输,在

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5408

5408

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?