⑥再次启动传送带,将检测合格的频率计移动到包装工位,并统计和显示合格产品的数量;2s后传送带停,回到初始状态。

2.频率计检测设计要求

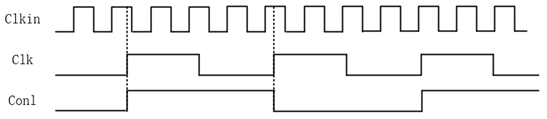

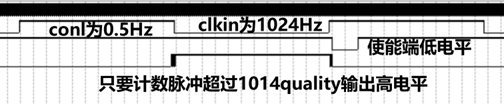

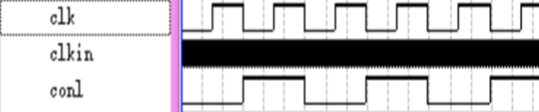

频率计是用来测量给定信号频率的仪器。其基本原理是在给定的标准时间内(通常是1s),通过计数器检测输入信号的脉冲个数。如图2所示,Clkin是待测信号,Clk是频率计工作时钟,Conl是频率计产生的测控信号,测控信号通常设置为2s的周期,占空比为50%。测量的原理:统计在Conl为高电平时Clkin有多少个周期的脉冲信号。

1.确定VHDL描述与原理图相结合完成设计

根据该检测控制系统的设计要求可知,该系统可以由三个子部分组成,即频率检测部分、系统主控制部分和七段数码管显示部分。因此,可以分别将三个部分用VHDL描述,进而将三个部分分别封装成元件,以供最后原理图调用连接完成设计。

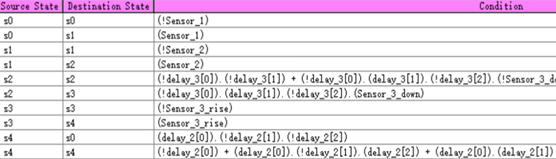

2.确定状态情况

根据整体控制系统设计要求可知,该系统的状态可以分为五个,即如下图所示的状态机图。

S0:初始状态(Sensor_1检测到产品进入而进入下一状态)

S1:产品进入传送带传输(Sensor_2检测到产品到达而进入下一状态)

S2:移动电机向下移动,频率测量仪接入产品(延迟3s进入下一状态)

S3:进行检测,移动电机向上移动(Sensor_3检测到电机到达而进入下一状态)

S4:再次启动传送带,更新数据(2s后回到初始状态)

3.数码管显示功能

考虑到该系统需要用七段数码管显示产品是否合格以及合格产品的数量,因此需要相应的数码管显示功能,而此前的实验中有实现此功能的模块,可以将其封装成这里可以调用的元件。

1. 频率检测部分VHDL描述

1.1导入相关的包

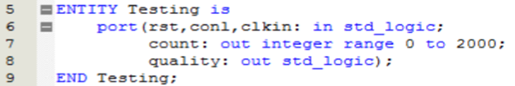

1.2定义相关输入输出

①rst为频率检测功能的使能信号,其值由主控制部分传递过来

②conl为频率计产生的测控信号,一般设置为0.5Hz

③clkin为待测信号

④count为在conl为高电平时clkin的脉冲信号数量

⑤quality为检测结果,其值输出返回给主控制部分

1.3检测脉冲数量进程

①在conl为高电平时候,只要clkin到达一个上升沿时就计数一次

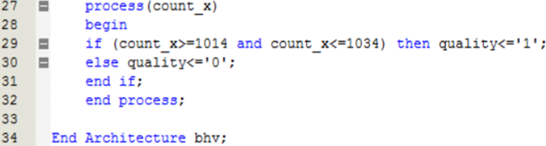

1.4检测结果返回进程

①只要在一个conl为高电平时clkin的脉冲信号数量为1014-1034就返回1。

2. 七段数码管显示部分VHDL描述

2.1导入相关的包(同上)

2.2将四位二进制数转换为七段数码管显示信号

①d由最高位到最低位分别对应一个七段数码管的a到g

②这里只设计了0-9的显示,超过9的情况只需要稍作改进即可

3. 系统主控制部分VHDL描述

3.1导入相关的包(同上)

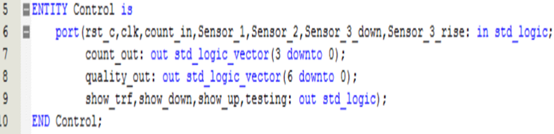

3.2定义相关输入输出

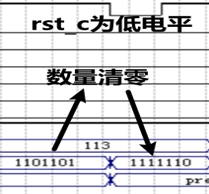

①rst_c为清零复位信号,clk为工作信号

②count_in为频率检测部分传来的检测结果

③Sensor_1、Sensor_2、Sensor_3_down、Sensor_3_rise为模拟传感器信号

④count_out为统计的合格产品数量

⑤quality_out为表示产品是否合格

⑥testing为传递给频率检测部分的使能信号

⑦show_trf为传送带状态,show_down为电机是否下降,show_up为是否上升

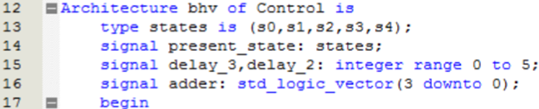

3.3定义状态机情况以及中间信号

①该控制系统存在5个状态

②delay_3、delay_2分别为下面需要用的实现延迟功能的中间信号

③adder为统计合格产品数量的中间信号

3.4状态机情况

①初始为S0状态,当Sensor_1检测到产品进入传送带时候进入下一状态S0

②S1状态传送带动(show_trf输出高电平),当Sensor_2检测到产品到达时进入下一状态S2

③S2状态电机下移(),当Sensor_3_down检测到电机到达时延迟三秒后进入下一状态S3

④S3状态主控制部分给频率检测部分使能信号(testing输出高电平),并且电机上移(show_up输出高电平),当Sensor_3_rise检测到电机到达时进入下一状态S4

⑤S4状态传送带动(show_trf输出高电平)延迟两秒后回到初始状态

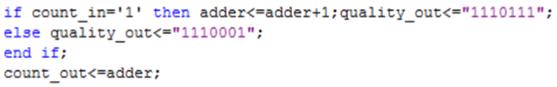

3.5统计合格产品与显示检测产品情况

①如果频率检测部分返回高电平则合格产品数量加一并且显示“A”,否则显示“F”

4.将三个部分的VHDL描述分别都封装成元件

5.连接三个部分封装成的元件

①quality与count_in连接

1.状态机验证

由上面调出的状态机图与前面设计的状态机相同,并且转换情况符合。

2.频率检测仿真波形图验证

3.主控仿真波形图验证

3.1固定输入设计

①clk是频率为1Hz的方波信号

②clkin是频率为1024Hz的方波信号

③conl是频率为0.5Hz的方波信号

3.2检测一次的情况

如图对仿真波形图做了相关说明,从中可以验证得该系统的相关设计要求已经基本实现。

3.3在上一次的基础上再检测一次的情况

3.4清零复位

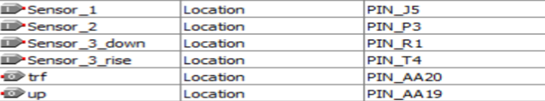

4. 引脚配置

基于实验板的硬件条件,合理规划硬件显示情况,对频率检测程序/主程序进行硬件验证。如下图为相关引脚配置。

①clk、clkin、conl分别加以1Hz、1024Hz、0.5Hz

②count和quality通过七段式数码管输出

③rst_c、Sensor_1、Sensor_2、Sensor_3_down、Sensor_3_rise分别接入推拉式开关

④trf、down、up分别接以发光二极管指示灯输出

1.用原理图设计较VHDL更为直观明了,可以通过电路图清楚其逻辑关系和实现的功能关系。而用VHDL语言设计则较为简便,只需清楚各个接口之间的关系和调用的原则。因此选用VHDL描述结合原理图的方式来设计实现较为合理。

2. VHDL描述的模块化,将实现不同功能的VHDL描述分开在不同的进程里面,实现VHDL的“高内聚低耦合”。

3. 状态机由状态寄存器和组合逻辑电路构成,能够根据控制信号按照预先设定的状态进行状态转移,是协调相关信号动作、完成特定操作的控制中心。交通信号灯可以用状态机的原理来实现,因为信号灯的变化状态是有限的,各个状态可以列举出来,状态间切换由计数器决定。

2200

2200

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?