参考:

一份大厂PCB布局指南参考!

技巧

使用大面积铺铜

铜是一种极好的导热体。由于 PCB 的基板材料(FR-4 玻璃环氧树脂)是一种不良导热体。因此,从热管理的角度来看,PCB的铺铜区域越多则导热越理想。

走线越宽越好

走线越宽电阻越小。

焊接散热焊盘

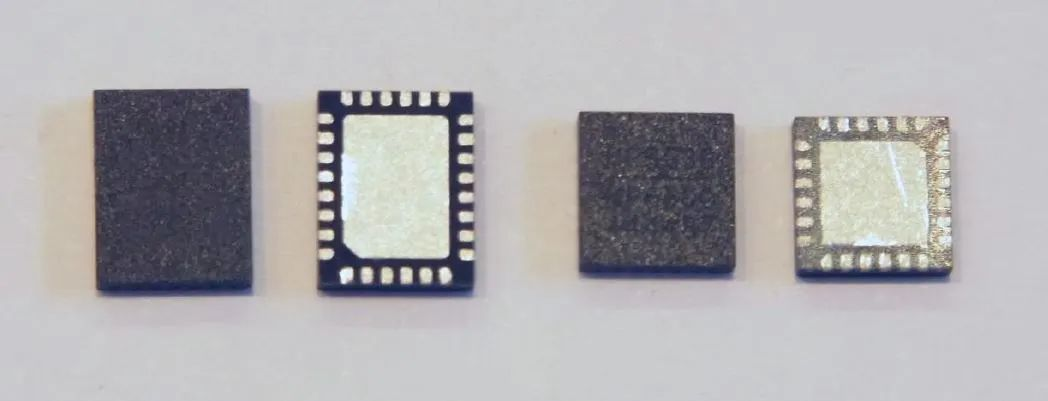

TSSOP 和 QFN 封装中,芯片底部会焊有大片散热焊盘。这里的焊盘直接连到晶元的背面,为器件散热。必须将焊盘很好地焊接到PCB上才能耗散功率。

IC规格书不一定会指定焊盘焊膏的开口。通常,SMT制程工程师对放多少焊料,过孔模具使用什么样的形状都有自己的一套规则。

如果使用和焊盘大小一样的开口,则需要使用更多的焊料。当焊料熔化时,其张力会使器件表面鼓起。另外,还会引起焊料空洞(焊锡内部凹洞或间隙)。当焊料回流过程中助焊剂的挥发性物质蒸发或沸腾时,会发生焊料空洞。这会导致接合处的焊料析出。

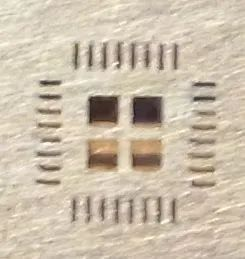

为了解决这些问题,对于面积大于约2mm2的焊盘,焊膏通常沉积在几个小的正方形或圆形区域中。将焊料分布在多个较小的区域里可以使助焊剂的挥发性物质更容易挥发出来,以免造成焊料析出。

热过孔-越多越好

过孔是一种小的镀孔,通常用于将信号走线从一层传递到另一层。 顾名思义,热过孔是将热量从一层传递到另一层。适当地使用热过孔可以有效帮助PCB散热,但也需要考虑实际生产中的诸多问题。

过孔具有热阻,这就意味着每当热量流经时,过孔两端会有一定温差,其测量单位为摄氏度/每瓦特。所以,为最大限度地降低热阻,提高过孔的散热效率,过孔应设计大一点,且孔内的覆铜面积越大越好。

虽然可以在PCB的开放区域使用大的过孔,但是,过孔常常被放在散热焊盘的内部,因为这样可以直接从IC封装散热。在这种情况下,不可能使用大过孔,因为电镀孔过大会导致“渗锡”,其中用于连接IC至PCB的焊料会往下流入通孔,导致焊点不良。

有几种方法可以减少“渗锡”。一种是使用非常小的过孔,以减少渗入孔内的焊料。然而,过孔越小热阻越高,因此想要达到相同的散热性能,需要更多的小过孔才行。

另一种技术是“覆盖”电路板背面的过孔。这需要去除背板上阻焊层的开口,使得阻焊材料覆盖过孔。阻焊层会盖住小的过孔使焊锡无法渗入PCB。

但这又会带来另一问题:助焊剂滞留。如果使用阻焊层盖住过孔,那么助焊剂会滞留在过孔内部。有些助焊剂配方具有腐蚀性,长时间不去除的话会影响芯片的可靠性。所幸大多数现代免清洗助焊剂工艺都是无腐蚀性的,不会引起问题。这里需注意,散热孔本身不具备散热功能,必须把它们直接连接至铺铜区域。

芯片中间的散热焊盘通常为GND,因此可以接入 PCB 接地层。在上图 的 TSSOP 封装的示例中,采用了一个 18 通孔阵列,钻孔直径为 0.38 mm。该通孔阵列的计算热阻约为 7.7°C/W。

通常,这些热通孔使用 0.4 mm 及更小的钻孔直径,以防止出现渗锡。如果 SMT 工艺要求使用更小的孔径,则应增加孔数,以尽可能保持较低的整体热阻。

除了位于板区域的通孔,IC 主体外部区域也设有热通孔。在 TSSOP 封装中,铜区域可延伸至封装末端之外,这为器件中的热量穿过顶部的铜层提供了另一种途径。

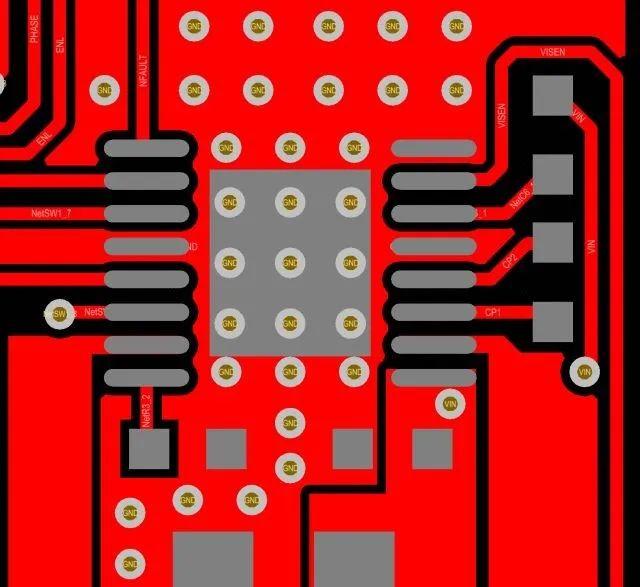

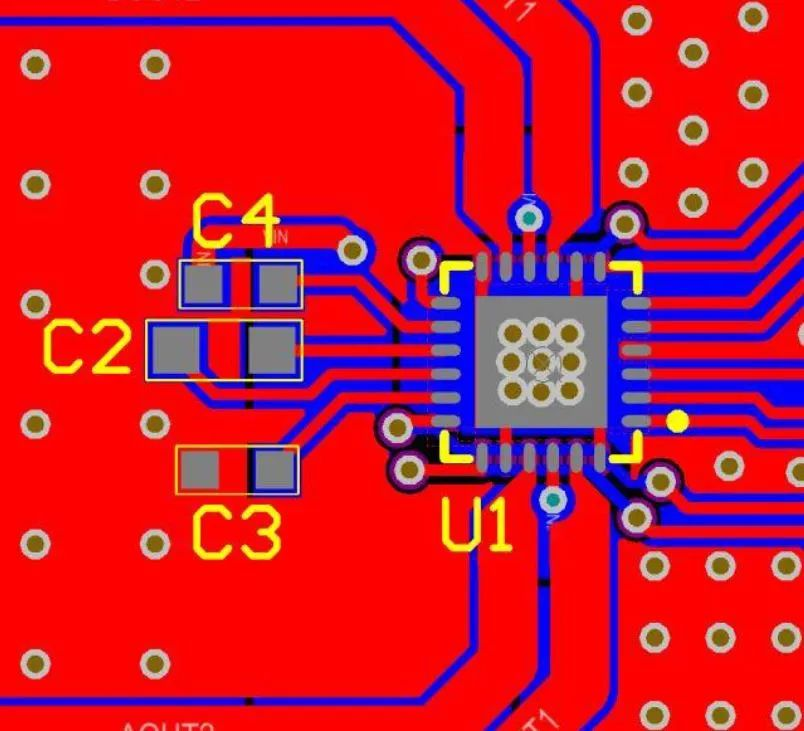

QFN 器件封装边缘四周的板避免在顶部使用铜层吸收热量。必须使用热通孔将热量驱散至内层或 PCB 的底层。下图中的 PCB 布局所示为一个小型的 QFN (4 × 4 mm) 器件。

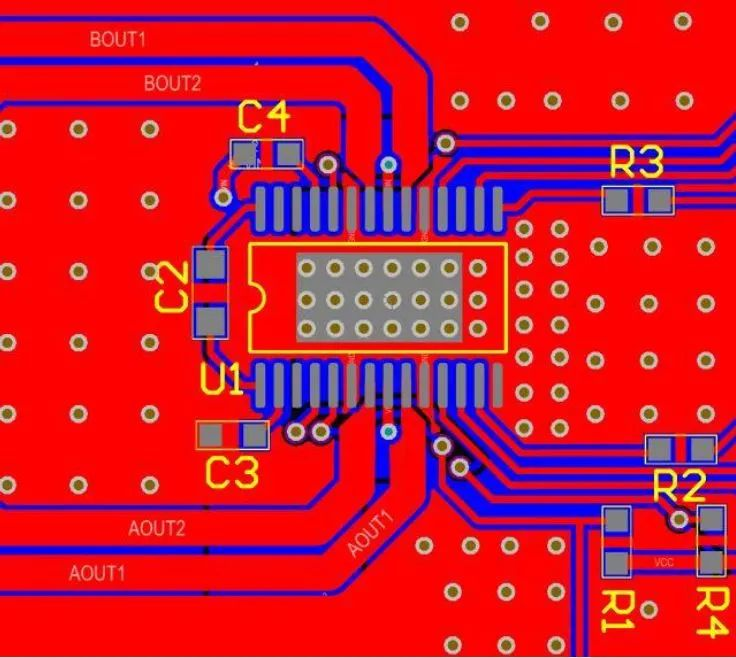

元件贴装

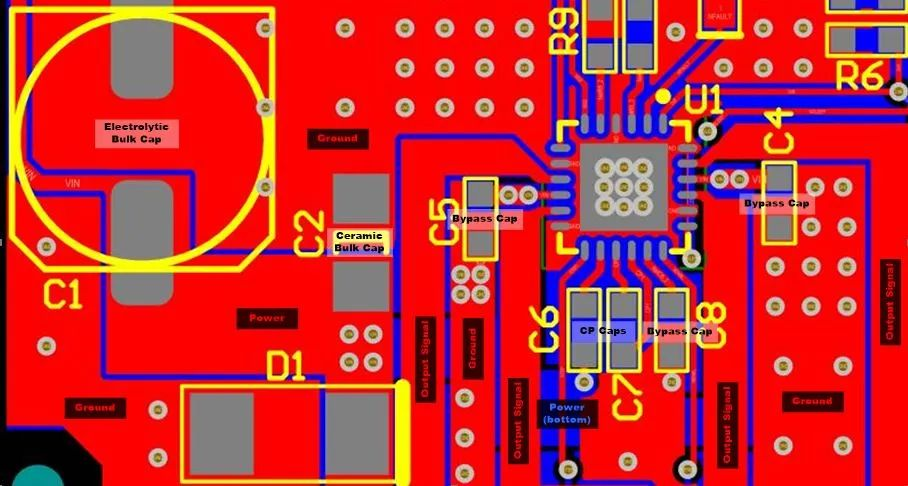

电机驱动IC的元件贴装指南与其他电源IC相同。旁路电容应尽可能靠近器件电源引脚放置,且旁边需放置大容量电容。许多电机驱动IC会使用自举电容或充电泵电容,这些也应放在IC附近。

下图显示了MP6600步进电机驱动的双层板PCB布局。大部分信号走线直接布置在顶层。电源走线从大容量电容绕到旁路,并在底层使用多个过孔,在更换层的位置使用多个过孔。

5907

5907

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?