4.17 CA校验(Command Address Parity)

MR5的A[2:0]用于控制C/A校验的使能,MR5默认不开启CA校验。在使能CA Parity时,必须将Parity Error位设置为0(也就是MR5的A4=0)。当开启CA Parity,命令发送到颗粒有一定的延时,这个延时就是Parity Latency。当CA校验开启后的一段时间内,只允许发送DES命令,以免DRAM出错。CA校验模式仅允许在DLL-on的模式下使用,当DLL off时,不允许开启CA校验。

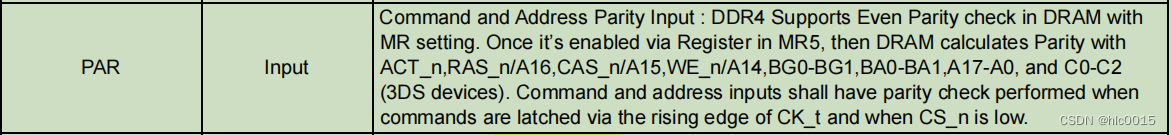

在DRAM管脚上有一个单独的CA校验输入信号,符号为PAR,当在MR5中开启CA校验功能,则CA校验通过ACT_n, RAS_n/A16, CAS_n/A15, WE_n/A14以及其他的地址信号(包括BG0-1, BA0-1, C0-C2)来计算校验值,CKE,ODT和CS_n信号不参与计算。在2.7章节的Pinout Desciption中也有说明,如下图所示。

手册中对CA校验的计算有一个举例,例如在4Gbit的x4单片器件中,CA校验由BG0, BG1, BA1, BA0, A16/ RAS_n, A15/CAS_n, A14/WE_n, A13-A0 and ACT_n信号计算得出,当然,DRAM内部应该将未用到的地址pin视为0。

一般来说,parity一般为偶校验,也就是说,所有用来进行Parity计算的输入,包括Parity信号,应该保持为偶数个1。可以通过改变Parity信号的输入值,来确保所有参与计算的信号其为1的个数为偶数个。

在CS_n拉低时,当DRAM在任何命令中检测到CA校验错误,则会执行以下步骤:

- 忽略出错的命令。在出错的命令之前的命令,也就是位于tPAR_UNKNOWN时间窗口期的命令是否能够被DRAM执行未可知,可能被执行了,也可能没有被执行。当窗口期中的READ命令未被执行,那么DRAM将不会使能DQS的输出。

- DRAM自己会将错误信息写入MPR Page1中。

- 设置MR5中的Parity Error Status位(DRAM自己写1),这个设置必须在ALERT_n信号被DRAM释放之前进行设置也就是需要在tPAR_ALERT_ON + tPAR_ALERT_PW(min)的时间窗口期内进行设置。

- 在tPAR_ALERT_ON时间后置位ALERT_n信号。

- 等待所有正在进行中的命令完成。这些命令是在tPAR_UNKNOWN窗口期接收的。如果在自刷新退出后,parity error出现在tXS_FAST和tXS之间的窗口期中,DRAM将延迟ALERT_n信号的释放。详见图52。

- 在关闭所有打开的page之前等待tRAS_min(ACT到PRE命令的周期)。DRAM在tPAR_ALERT_ON + tPAR_ALERT_PW的时间窗口期不会执行任何命令。这句话是否和前面的发送MRS命令冲突? 其实不冲突,前者是出错后,DRAM自己自动地将MR5中的Parity Error Status置1,而非内存控制器去发送MRS命令。后面也会介绍到外部设置MR5中的Parity Error Status位时,只能写0,不能写1。

- 满足tPAR_ALERT_PW_min时序后,释放ALERT_n。

- 在DRAM跳到Pre-charge状态时,ALERT_n信号释放。

- 在(tPAR_ALERT_ON + tPAR_ALERT_PW)之后,DRAM可以接收其它命令,并进行正常操作。Parity的Latency会影响命令的时序,但如果不对MR5的Parity Error Status清零的话,parity校验将不会继续进行。

- 在(tPAR_ALERT_ON + tPAR_ALERT_PW)窗口期间,DRAM可能会忽略刷新命令,或者说刷新命令是第一个出错命令,所以推荐的做法是内存控制器多发一个额外的刷新命令。

- Parity Error Status位可以在(tPAR_ALERT_ON + tPAR_ALERT_PW)之后的任何时候去读取。

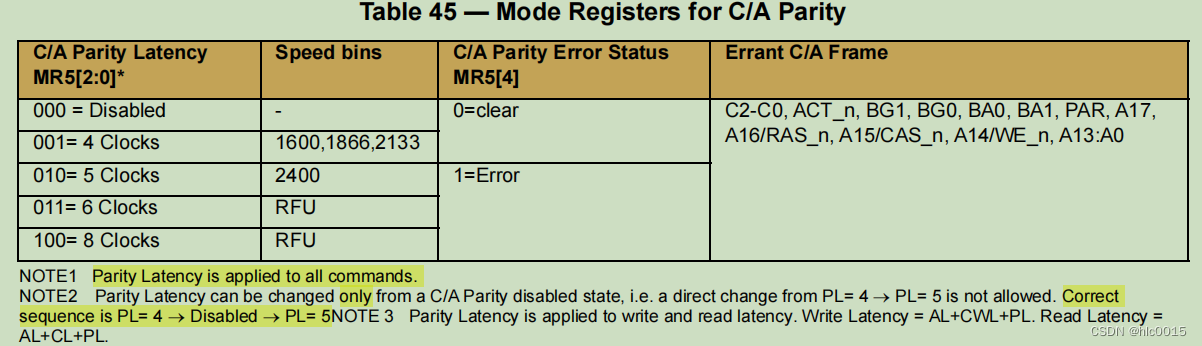

MR5中,CA Parity Latency是write only,Parity Error Status也是write only,且只能写0,不能写1。下表展示了MR5的CA parity相关的bit位。

其中,上表的脚注2对Parity Latency(PL)的切换有详细说明:不能直接从PL=4切换到PL=5,需要在切换间插入一个disable CA parity的设置。PL用于write latency和read latency中。

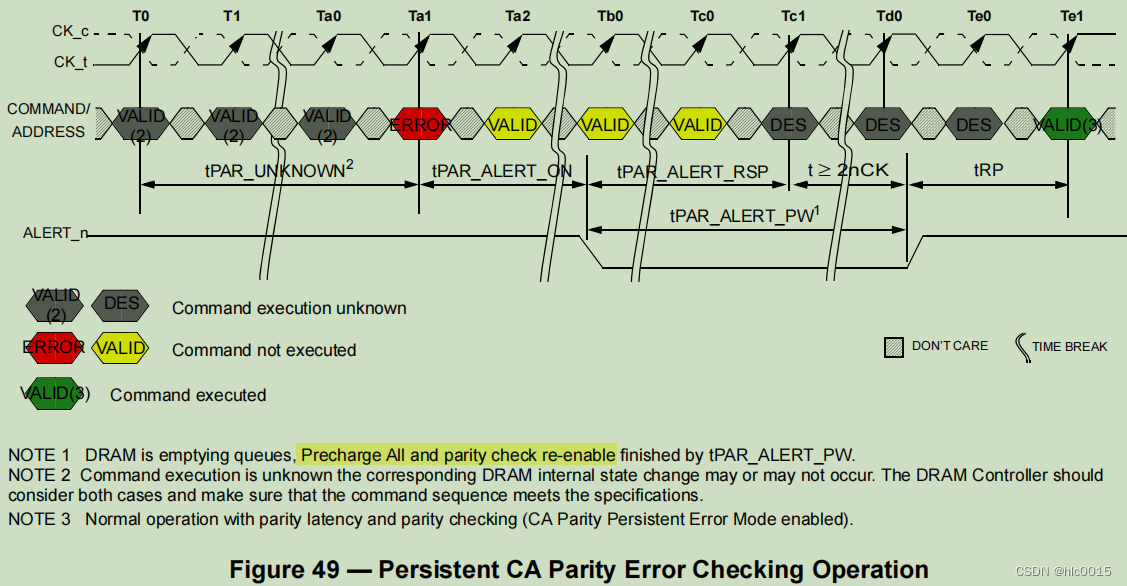

之前提到如果不对Parity Error Status进行清零的话,CA parity校验是不能继续进行的,不过有一种情况除外:当MR5的A9=1(Persistent Parity Error Mode),则在ALERT_n释放后,即使Parity Error Status未清零,也会进行CA校验。但是,这样做有个坏处,即如果之前有误,MPR Page1中肯定会记录Error log,但是下一次再出现错误,MPR Page1中的对应位将视为"Don’t Care"。当当MR5的A9=1时,ALERT_n脉冲的持续时间依旧遵循tPAR_ALERT_PW的最大/最小值。内存控制器一旦监测到ALERT_n信号拉低了,必须立马发送DES命令,其对应的时间参数为tPAR_ALERT_RSP。

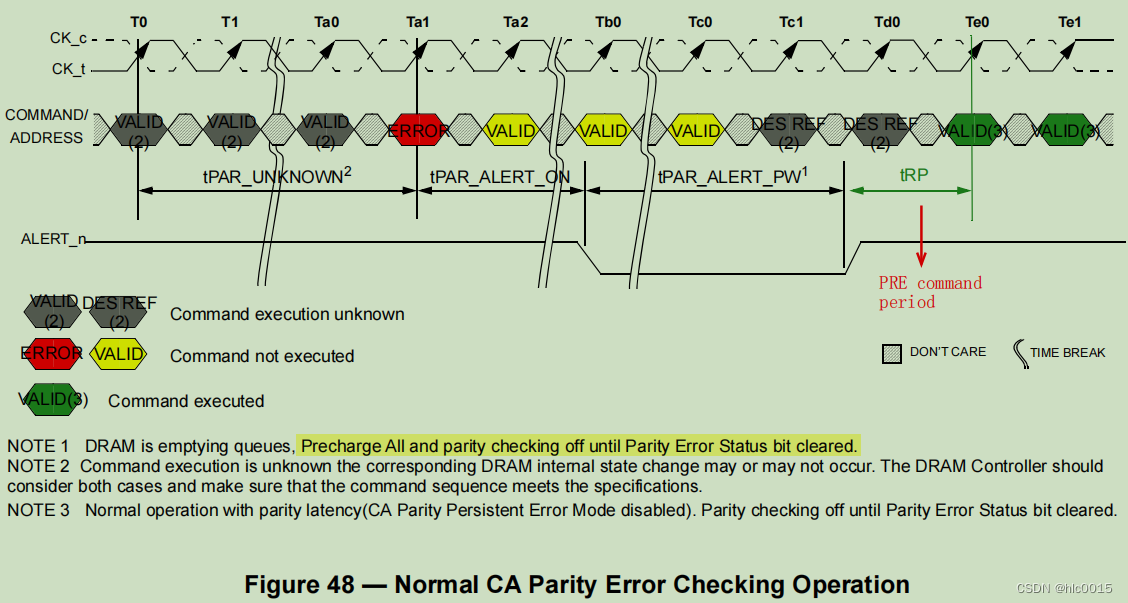

下图是未开启Persistenct CA Parity的Error check操作时序图,其中NOTE3中写得很清楚,Te0处的有效命令的执行仍然要遵循parity latency的时序,但是后续不会进行Parity校验,除非Parity Error Status bit被清零。

下图是开启了Persistenct CA Parity的Error check操作时序图,NOTE3中表示,Te1处的有效命令可以进行Parity校验。

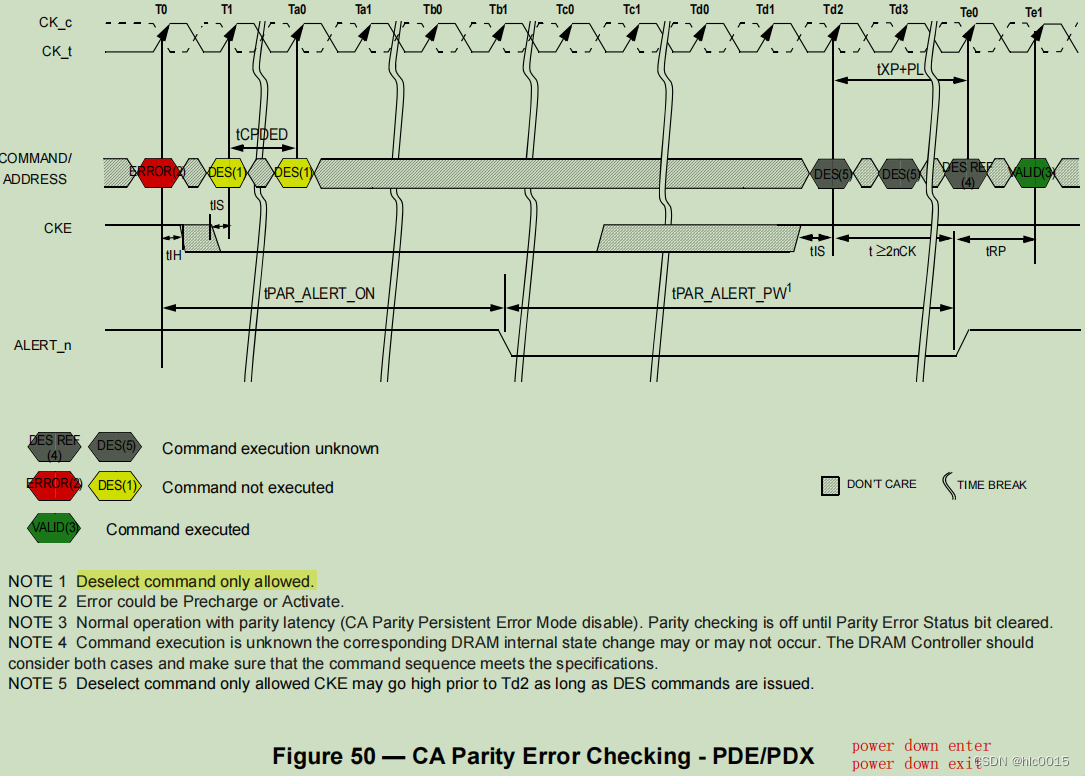

下图为Power Down Entry和Power Down Exit的CA parity Error时序图。

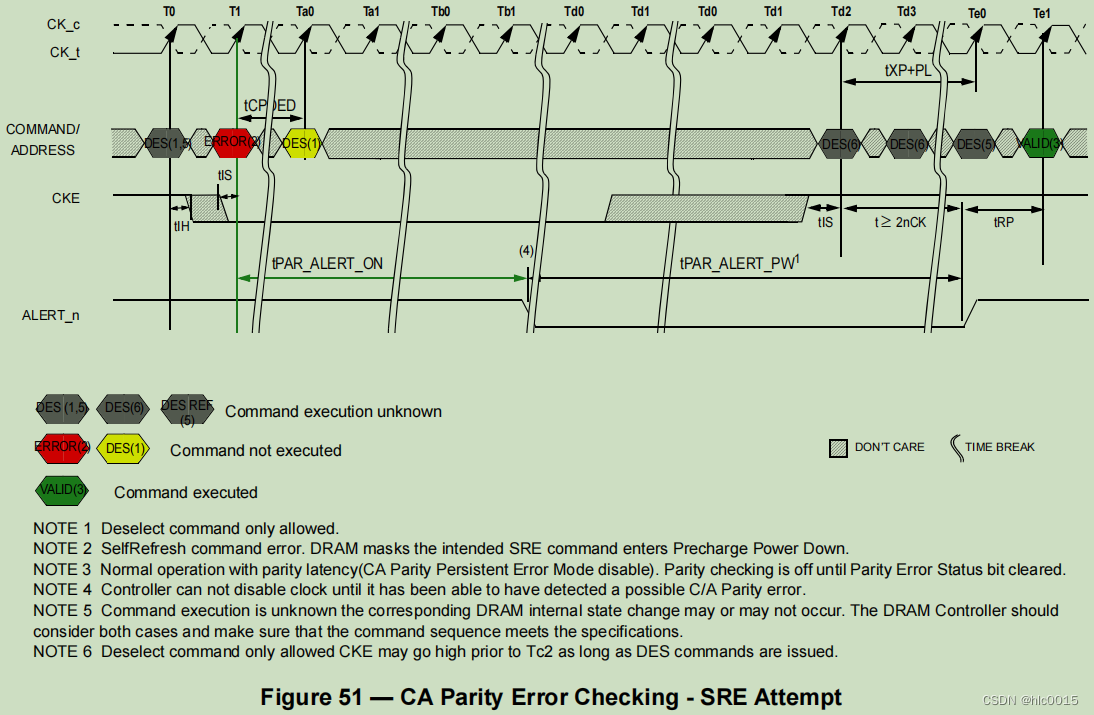

下图为想要进入自刷新时出现CA Parity Error的时序图。其中NOTE2写道,该时序图为进入自刷新时CA校验错误,DARM将会进入Precharge Power Down。此时序图中未打开MR5的A9bit。在探测到CA校验错误前,内存控制器不能关闭时钟(NOTE4)。NOTE6中的Tc2应该改为Td2。

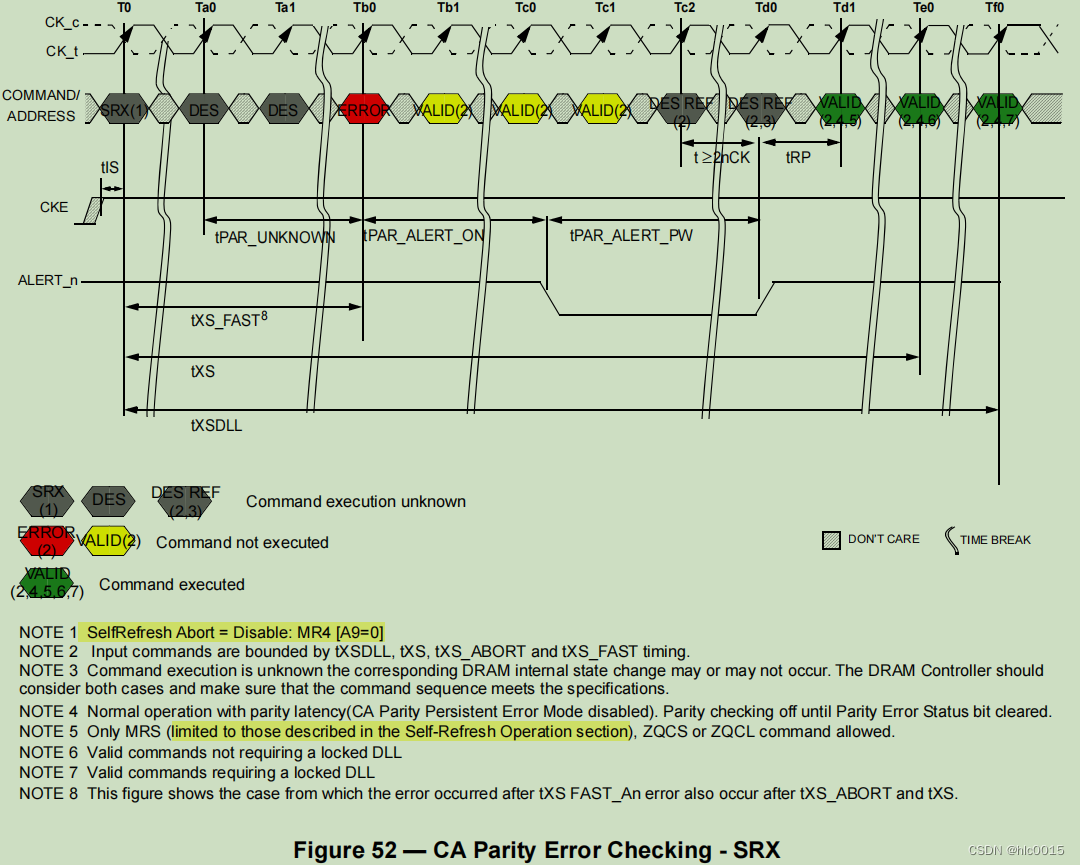

下图为退出自刷新时出现CA Parity Error的时序图。注意,这里是发送SRX命令让其退出自刷新,而不是MRS命令(MR4 A9=1)。

图中有几个注解,其中NOTE5表明在tRP后,即Td1时刻只允许MRS/ZQCS/ZQCL命令;NOTE6表示,Te0时刻的命令不要求锁定DLL;NOTE7表示Tf0时刻要求DLL锁定;NOTE8表示该图是在tXS_FAST时序后出现CA校验Error,但也可以用作tXS和tXS_ABORT时序。

进入和退出CA parity的时序(手册上并未在此处另起标题)

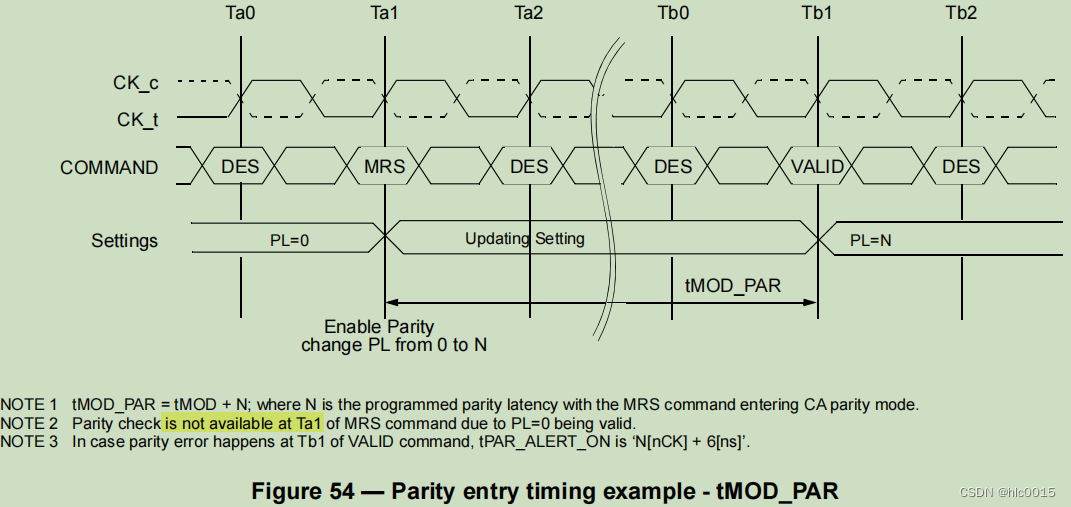

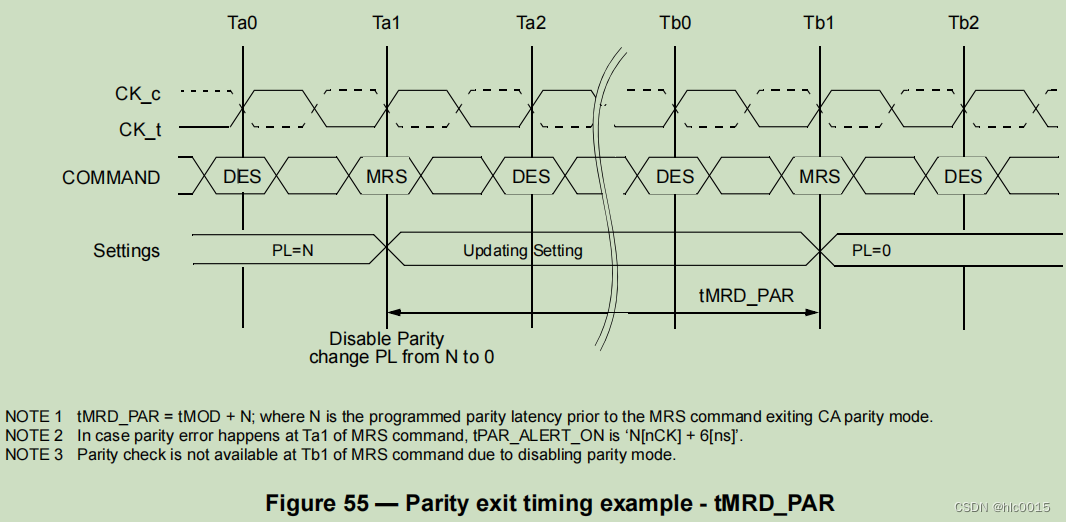

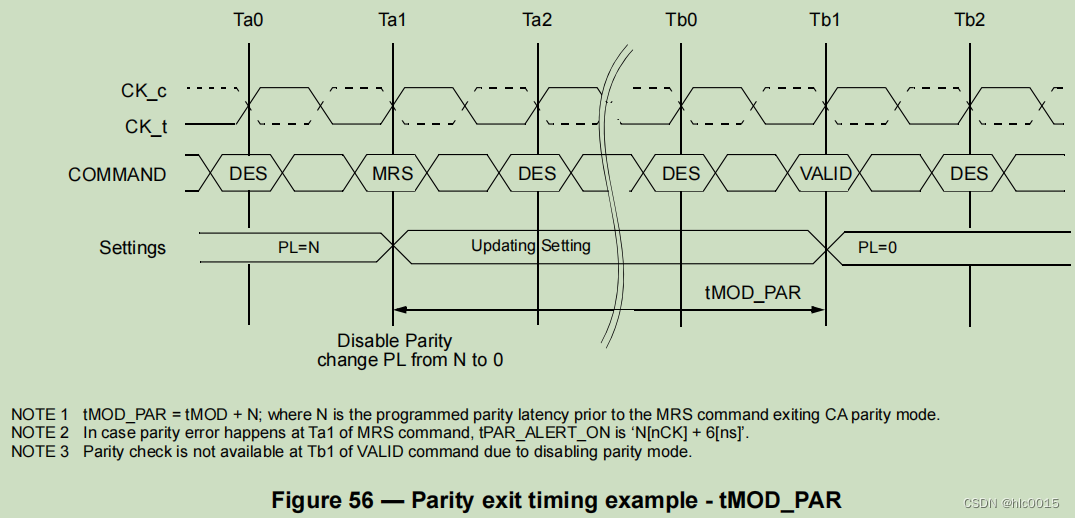

当处于CA Parity模式时,包括进入和退出CA Parity模式,在其它MRS命令发送前,用户必须等待tMRD_PAR时长,或者发送其它命令前,用户必须等待tMOD_PAR时长。其中,

tMOD_PAR = tMOD + PL;

tMRD_PAR = tMOD + PL;

这里没写错,手册上就是这么定义的,两个等式的右边一模一样(手册JESD79-4B)。

对于进入CA parity,其PL延时为发送使能CA parity的MR5寄存器中设定的parity latency。

对于退出CA parity,其PL延时为之前MR5中存储的parity latency值。

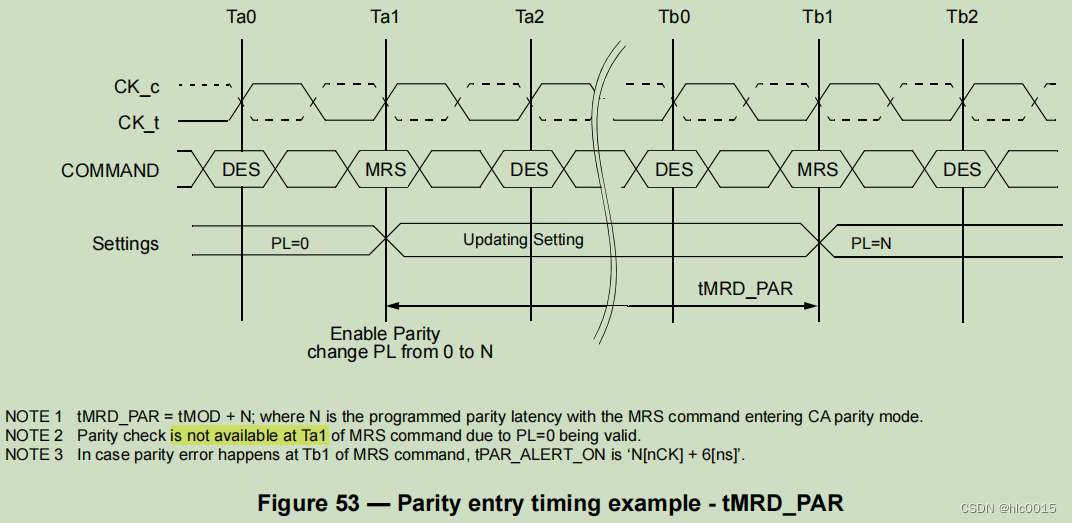

图53展示了进入CA Parity的时序。两个MRS之间的时序为tMRD_PAR。NOTE2很重要,**指明在进入CA Parity时,不进行parity校验。**NOTE3说明,假如刚进入CA parity,下一个命令出错了,则tPAR_ALERT_ON = N[nCK] + 6ns。

图54展示了进入CA parity的时序,俩命令分别为MRS和其它的非MRS的有效命令。其注解和图53的注解类似。

图55展示了退出CA parity的时序。俩命令为MRS命令。NOTE2表明,假设在发送退出CA parity的MRS命令出现校验错误,则其时序依然遵守tPAR_ALERT_ON(= N[nCK] + 6ns)。NOTE3表明,当Ta1时刻发送退出CA Parity的MRS命令后(假设是正常的命令,无误),则Tb1时刻的MRS命令不会进行Parity校验。

图56展示了退出CA parity的时序。俩命令为MRS命令和其它非MRS的有效命令。其注解和图55的注解类似。

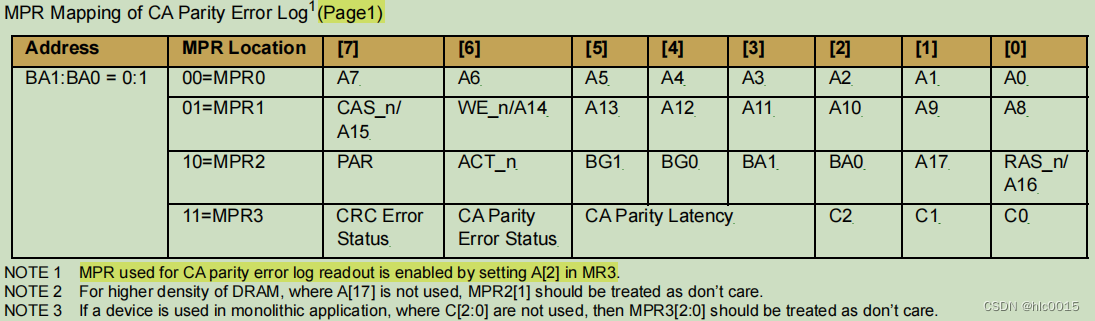

4.17.1 CA Parity的错误log的读出

在MPR的Page1中的CA Parity的错误的位置如下,其在MR3寄存器的描述中一样。

4.18 Gear down模式(其意义何在?)

通过MR3 A3 bit来控制SDRAM是否进入gear down模式。gear down模式只能在初始化和SRE(退出自刷新)时使用。SDRAM模式位于1/2的rate(1N,即时钟周期为1N)模式,处于此速率模式下的DRAM利用低频率的MRS命令,后续跟随一个同步脉冲来将1/4(2N,即时钟周期为2N,周期长了一倍)rate速率下的CS_n,CKE和ODT信号对齐到合适的时钟边沿。对于1/2 rate模式下,不需要额外的MRS命令与同步脉冲来进入geardown模式。

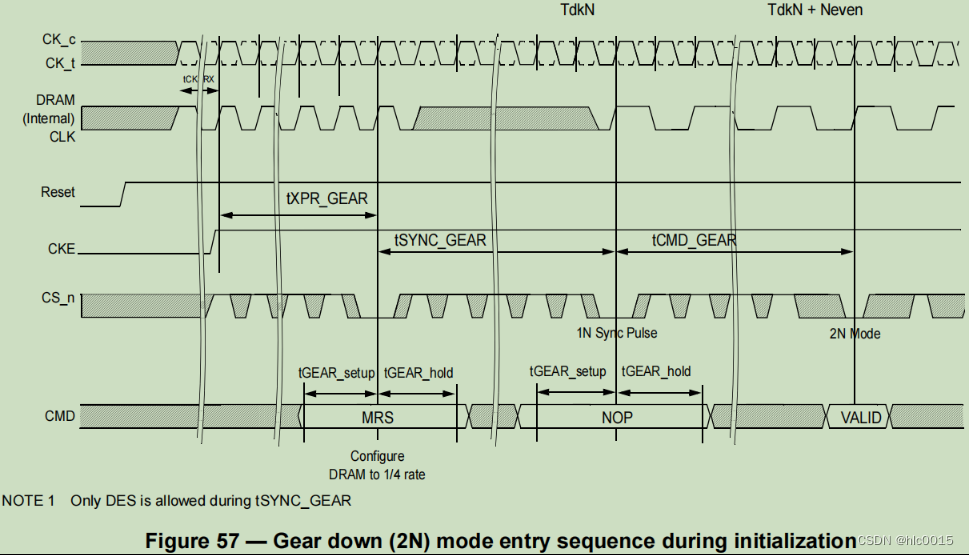

在初始化时进入geardown模式:

- 在上电和复位的情况下,DRAM默认处于1/2速率模式。

- 将Reset设置为无效。CKE置位有效来使能DRAM。

- 发送低频率的MRS命令,该MRS命令设置MR3的A3=1,持续周期为N*tCK时长,但CS_n只有1N周期时长。

- 内存控制器发送1N周期的同步脉冲信号,与此对应的为N*tCK个NOP命令。tSYNC_GEAR时长是偶数个时钟周期,即同步脉冲距离MRS命令有偶数个时钟周期。

- 采样到上一步的1N周期的同步脉冲后的tCMD_GEAR时长后,此后的初始化序列,包括tDLLK和tZQinit,便从2N模式开始(即1/4rate模式)。

图57展示了初始化时进入2N模式的时序图,其中,在tSYNC_GEAR时长内只允许发送DES命令。

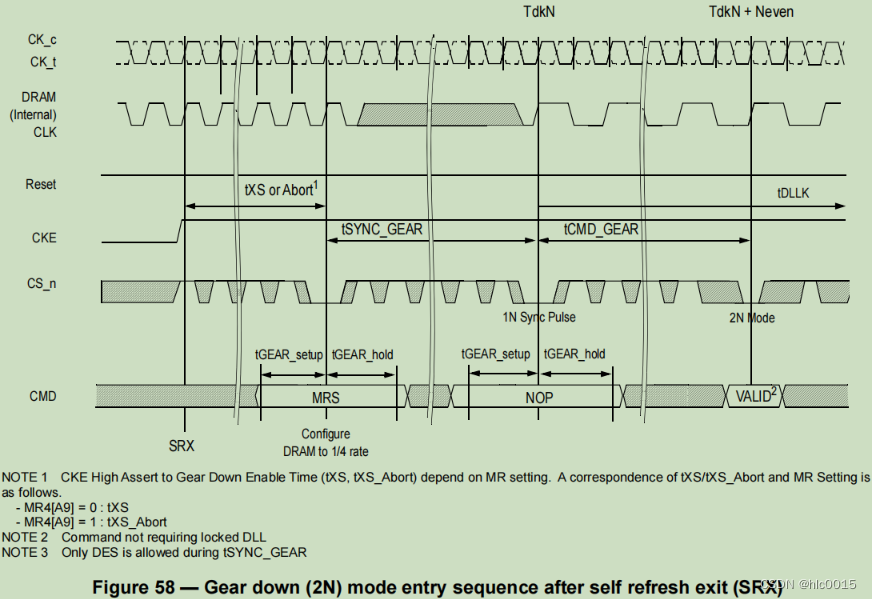

在自刷新退出后,进入gear-down模式的流程如下:

- 在自刷新期间将DRAM复位到1N模式。

- 发送低频率的MRS命令,该MRS命令设置MR3的A3=1,持续周期为N*tCK时长,但CS_n只有1N周期时长,当然,此处的CS_n信号之前,必须满足tXS或tXS_ABORT时序。

- 内存控制器发送1N周期的同步脉冲信号,与此对应的为N*tCK个NOP命令。tSYNC_GEAR时长是偶数个时钟周期,即同步脉冲距离MRS命令有偶数个时钟周期。

- 在同步脉冲信号的tCMD_GEAR时长后,无需DLL锁定的有效命令可以被发送。

- 在同步脉冲信号的tDLLK时长后,需要DLL锁定的有效命令才能被发送。

图58展示了SRX后的gear down时序。

如果在自刷新之后为1/2 rate模式,则自刷新退出时无需N*tCK时长的MRS命令,也无需1N周期的同步脉冲信号。退出自刷新后到第一个有效命令的最小延迟为tXS或tXS_Abort。

在进入自刷新模式时,DRAM可能会从1/4速率模式切换到1/2速率模式(2N to 1N),其会自动复位到1N模式。通过其它命令将速率从2N切换到1N模式(包括利用MRS命令设置MR3的A3从1变为0)意味着DRAM将会丢失数据,并且DRAM会处于不确定状态。这段话的意思是说,只有在自刷新模式下降2N切换到1N才是最安全的方式。

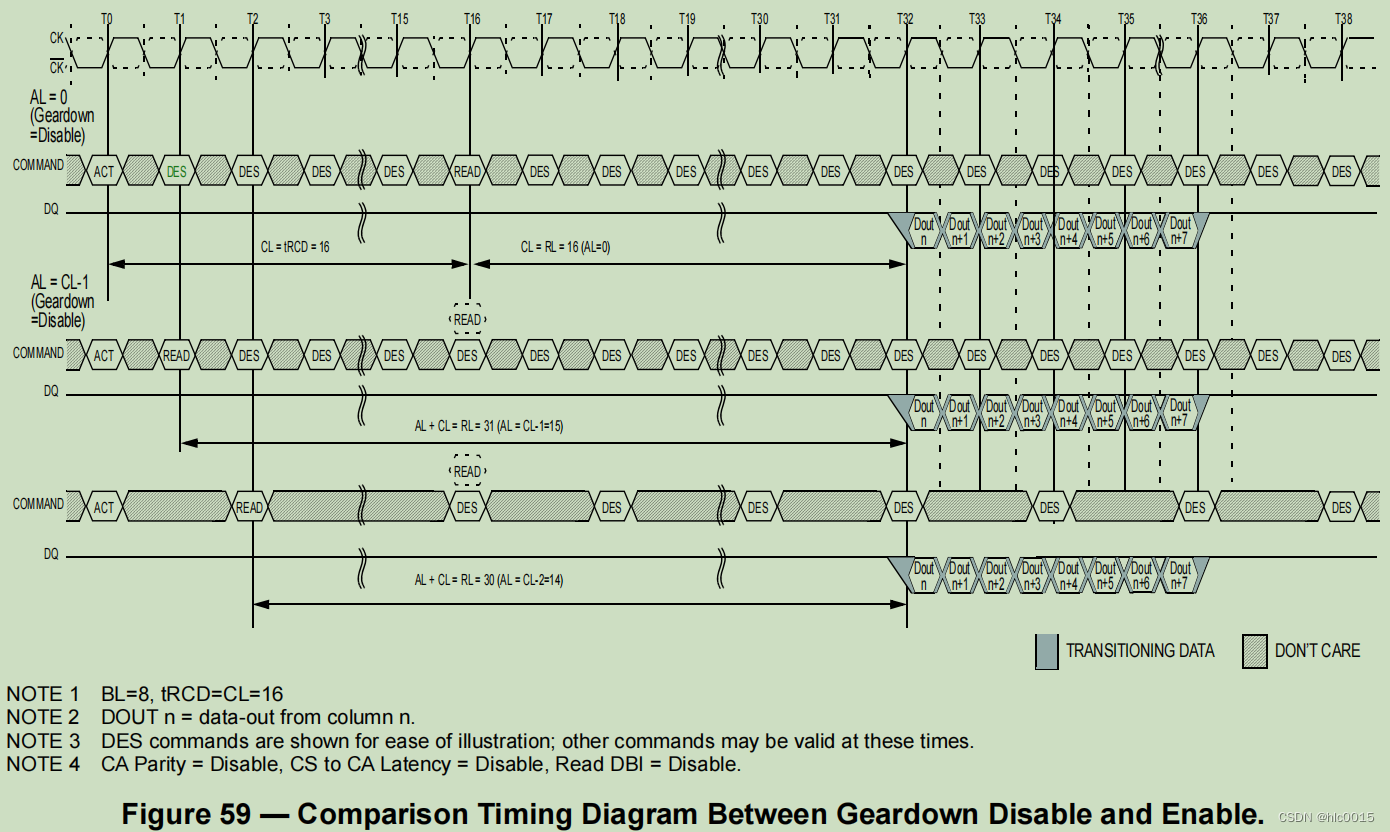

在1/4速率下的geardown模式的操作,MR的设置应该如下:

- CAS latency(MR0 A[6:4,2])应该为偶数个时钟周期。

- 写恢复时钟和读到Precharge(MR0 A[11:9])的时钟周期应该为偶数个。

- Additive Latency(MR1 A[4:3]):0,CL-2

- CAS write latency(MR2 A[5:3]):偶数个时钟周期。

- CS to Command/Address Latency Mode (MR4 A[8:6]): 偶数个时钟周期

- CA Parity Latency Mode (MR5 A[2:0]): 偶数个时钟周期

在发送MRS进入gear down模式之前,CAL和CA parity模式必须被disable。用户可以在tSYNC_GEAR和tCMD_GEAR时序满足后再使能CAL或CA parity。

下图展示了geardown模式enable和disable下的时序。

文章详细阐述了DRAM中的CA校验机制,包括启用条件、校验过程、错误处理及延迟影响。同时介绍了Geardown模式,这是一种在初始化和退出自刷新时使用的低速率模式,通过特定的MRS命令和同步脉冲切换速率。错误日志在MPR的Page1中可读取。

文章详细阐述了DRAM中的CA校验机制,包括启用条件、校验过程、错误处理及延迟影响。同时介绍了Geardown模式,这是一种在初始化和退出自刷新时使用的低速率模式,通过特定的MRS命令和同步脉冲切换速率。错误日志在MPR的Page1中可读取。

611

611

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?