用户界面 PAGE 1

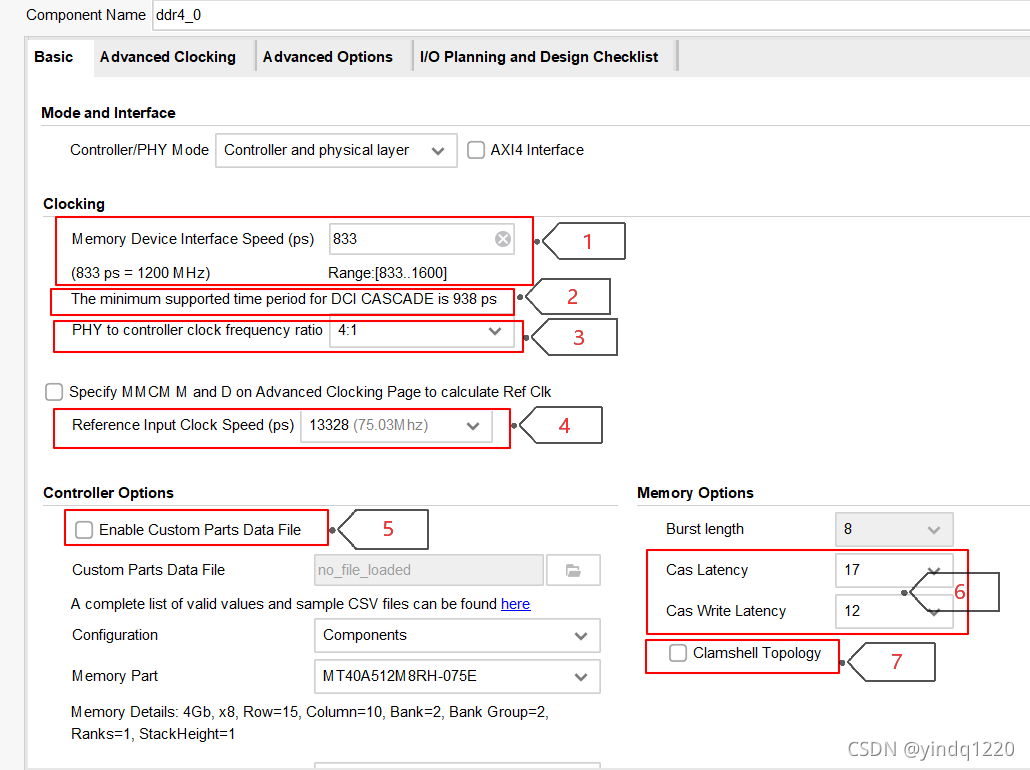

按照图中序号分别记录:

1.memory device interface speed

确认DDR4的运行时钟,框中填写的是DDR4的单时钟周期。例如,2400P DDR4的时钟速率为1200M,时钟周期为833ps。

2.DCI CASCADE(数字控制阻抗,digitally controlled impendence)

DCI CASCADE用于约束单个或多个BANK的输出阻抗,使用该功能时,DDR4的时钟周期不低于938ps,即DDR时钟不高于1066,DDR4吞吐率不高于2133。

3.PHY to controller clock frequency ratio

DDR4与用户界面时钟的比率,此数值默认为4:1。因DDR4中时钟上升沿与下降沿各读写1次(单次时钟共计2次),在4:1的时钟下,用户界面每次需读写8倍的数据宽度。

4.reference input clock speed

定义DDR4 IP核的输入参考时钟周期。

5.enable custom parts data file

当memory part下拉选项中没有需要的DDR型号时,可以自己编写所需的DDR4存储器的CSV参数文件,导入IP核后,即可从memory part中选择相应型号。

6.CAS latency 和 CAS write latency(CL与CWL)

CL和CWL根据选择的DDR4型号进行选择,其中CWL可以从MR2寄存器中定义选择。

DDR是根据行列寻址的,首先需要发送预充电指令,内存开始初始化行地址选通(RAS),列地址选通(RAS)后,同时发送列地址和读写指令,访问对应DDR地址的数据。

CL指的是:列地址和读指令发送后,DDR输出第一个数据之间所需要的时间。

CWL指的是:列地址和写指令发送后,数据写入到DDR所需要的时间。

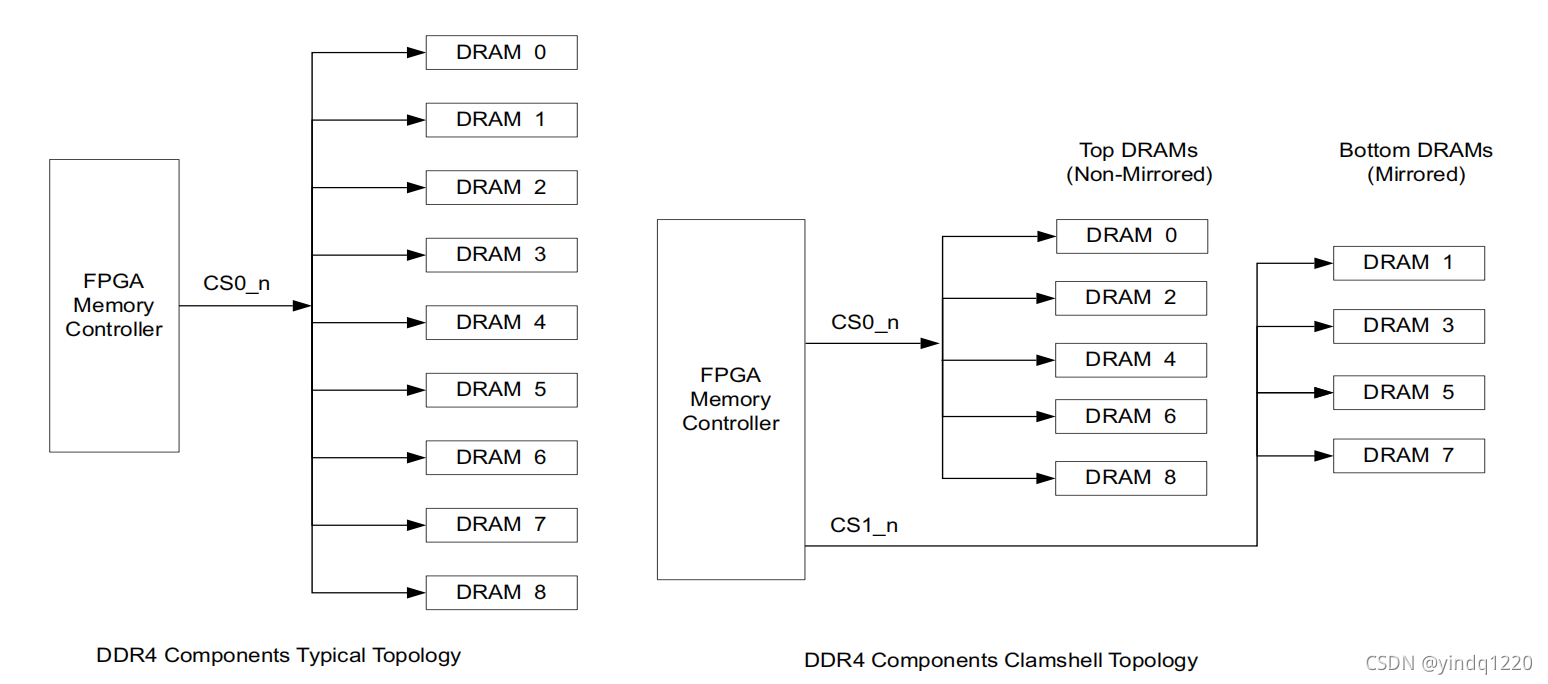

7.clamshell topology

当电路板的正面和反面都存在DDR4颗粒时(镜像对接),勾选此选项。选择此模式的原因是方便PCB布线,通过CS0和CS1分别控制正面和反面的DDR4。

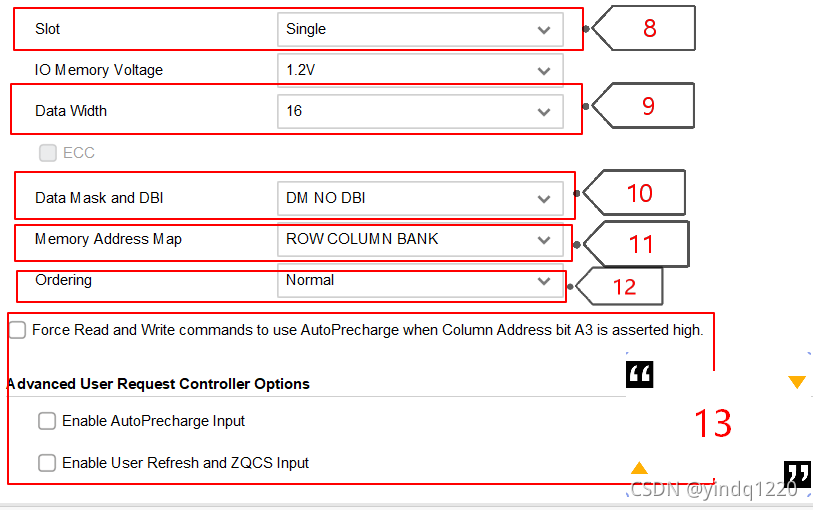

8.slot

用于非component的内存条,包括signal与dual两种,暂未使用到。

9.Data Width

由所选用的DDR颗粒数据宽度和数量决定,若DDR颗粒位宽为16bit,共选用4片DDR4,那么此处数据位宽为64。

10.Data Mask and DBI(Data Bus Inversion,依据DDR特性,DBI存在的意义在于降低功耗)

依据PG105手册选择下拉框,目前默认选择DM NO DBI

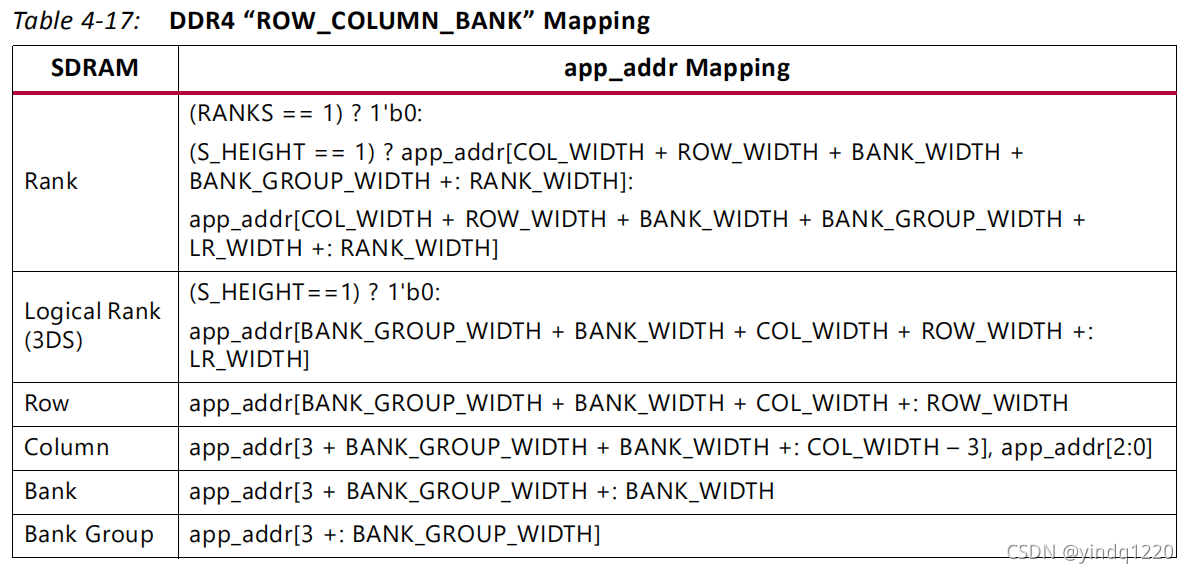

11.memory address map

通过此处选择用户输入地址信号(app_addr)与DDR控制器IP核的地址信号映射关系,默认为 ROW COLUMN BANK的顺序,如下图

12.ordering

命令执行顺序,分为两种情况:a.normal,允许DDR IP核依据内部控制器算法按照优先级别对外部输入的读命令、写命令等进行重新排序;b.strict,要求DDR IP核严格按照输入的命令依次执行,可能会降低DDR IP核的带宽利用率。

13.Force Read and Write commands to use AutoPrecharge,enable autoprecharge input,enable user refresh and ZQCS input

此三个选项需要对DDR、自身应用程序有较深的认识时勾选,目的在于提高读写的效率,由用户自行控制预充电、自刷新、ZQCS保持命令。当不勾选时,IP核自动控制预充电、刷新、ZQCS命令,默认不勾选。

本文详细介绍了DDR4内存配置的关键参数,包括memorydeviceinterfacespeed、DCICASCADE、PHYtocontrollerclockfrequencyratio等,以及如何优化设置预充电、自刷新和ZQCS命令。内容涵盖DDR4的工作原理、时钟比率、数据宽度、地址映射和命令执行顺序,旨在帮助用户理解和配置DDR4内存系统。

本文详细介绍了DDR4内存配置的关键参数,包括memorydeviceinterfacespeed、DCICASCADE、PHYtocontrollerclockfrequencyratio等,以及如何优化设置预充电、自刷新和ZQCS命令。内容涵盖DDR4的工作原理、时钟比率、数据宽度、地址映射和命令执行顺序,旨在帮助用户理解和配置DDR4内存系统。

3008

3008

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?