目录

一 静态时序分析的基础

1.1 同步电路设计

STA分析,也就是静态时序分析,是基于同步电路设计模型的。

在目标DFF的数据输入D端,假设外部也是同一时钟域的DFF的输出(Q端),并且经过若干组合逻辑进入目标DFF,而输出也被认为是驱动后一级、同一时钟域的寄存器。

在不设置约束的情况下,纯组合逻辑的输入->输出不得超过一个T,否则也会被认为是Timing violation(这里,纯组合逻辑的延迟,不应该大于一个时钟周期T;不满足此条件,需要修改设计,设计拆分)。

1.2 Timing path

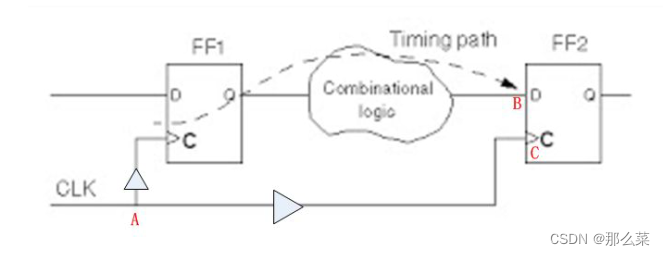

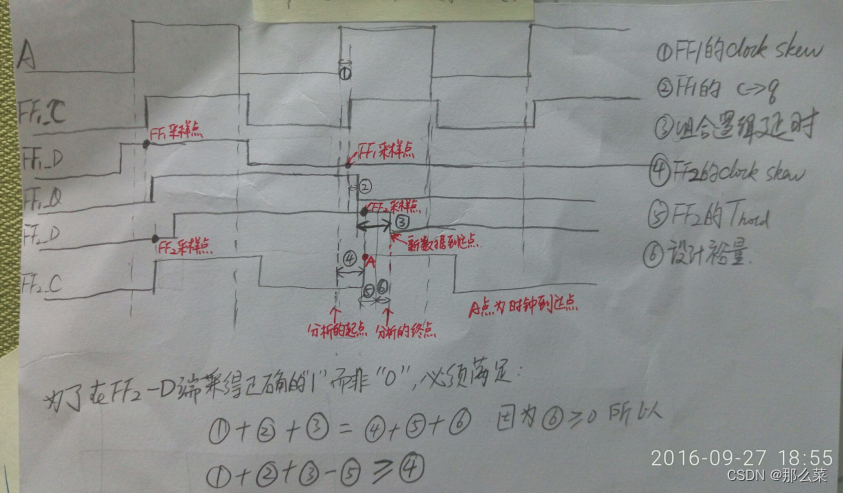

Timing path 就是时间线。Timing就是从起始位置的时间点到终点位置的时间点之间的时间长度。Path是指跟位置相关,即时间起始或终点的位置。Timing path就是某位置的某一时间点到另一位置的某个时间点。对于DFF来说,上升沿类似于一瞬间的脉冲,只有在这短短的一瞬间,数据才允许通过。对于DFF来说,有两个输入点:数据D和时钟CK,有一个输出点:数据Q。由于是时间比较,所以对于D和CK一定要有一个共同的起始时间点,如下图中的A点出现clk上升沿的时刻。如下图,假设我们分析DFF2的数据和时钟到达的时间。二者共同的出发点是A的上升沿,因为A位于时钟通路上,FF1的时钟经过A点到达FF1-C点,在FF1-C上升沿打开FF1,然后数据才能从FF1-Q输出,进而传递到FF2-D。在A点, FF2的时钟沿经过clock tree,达到FF2-C点。

所以数据走过的路程是:Data path: A->clk_tree_buf1->FF1-C -> FF1-Q -> Comb_logic -> B

而对于FF2来说只要满足下个周期的上升沿能够采样即可,所以时钟到达FF2-C的路径是:

Clk path: A -> clk_tree_buf2-> C.

二 建立时间和保持时间定义

对于某个DFF来说,建立时间和保持时间可以认为是此器件固有的属性。有关DFF的内部结构及setup和hold时间对应的逻辑门会在其他文章中进行细致描述。

在理想情况下,只要在时钟沿来临时,有效数据也来临(时钟沿之前或同时),则能够正确采集到数据;而在时钟沿之后(或同时),即使数据发生变化,也不会影响DFF的输出了。

然而在实际中,上升沿打开开关需要时间,逻辑门的状态改变(电容充放电等)都需要时间,因此数据的采集是需要一定时间的,在这个时间内数据不能发生变化。上升沿时候开关关闭也需要时间,如果在这个时间段内数据有变化的话,那么新数据就有可能被传递到下一级,进而发生错误,所以数据必须保持一定时间不变。(细节部分可以参考DFF的内部结构)。

总而言之:

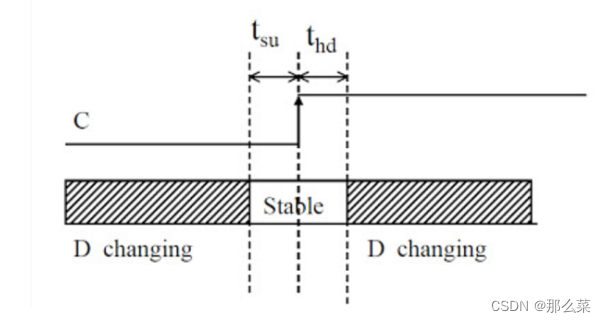

建立时间:在DFF的输入端口上看,在clk上升沿来之前,数据必须提前一个最小时间量“预先准备好”,这个最小时间量就是建立时间

保持时间:在clk上升沿来之后,数据必须保持一个最小时间量“不能变化”,这个最小时间量就是保持时间

三 建立时间和保持时间的计算问题

满足建立和保持时间要求,电路状态改变就是正确的,电路功能就不会发生错误;如果不满足,电容就没有足够的时间充放电,造输出点的电平可能既非0也非1,造成“亚稳态“输出。如果前级驱动够强劲,电路就能按照趋势变化下去,一定时间后该点的值就会变化为“正确值”,如果驱动不够强劲,电路就会恢复之前的值,最终得到何值是不可控的,所以我们要避免亚稳态。在使用DFF时,必须满足其建立时间和保持时间的要求。

3.1 建立时间计算

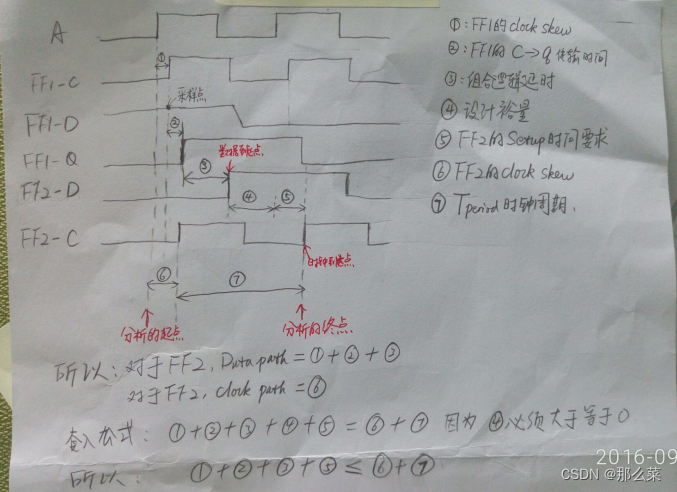

回头分析data path和clk path,假设t0时刻FF1采集到数据并传递给FF2,那么FF2只要在t10上升沿采到数据即可,所以数据有一整个Tperiod的时间来传递到FF2-D端。因为要满足建立时间要求,所以对于FF2来说,数据要比时钟“走得快”:

Tdata_path+ Tsetup <= Tclk_path+ Tperiod

所以

Tclk_delay_FF1 + Tc->q_FF1+ Tcomb_logic+ Tsetup<= Tclk_delay_FF2 +Tperiod

在分析STA时,不满足此公式的即为setup violation。

对应时序图的分析,见下图:

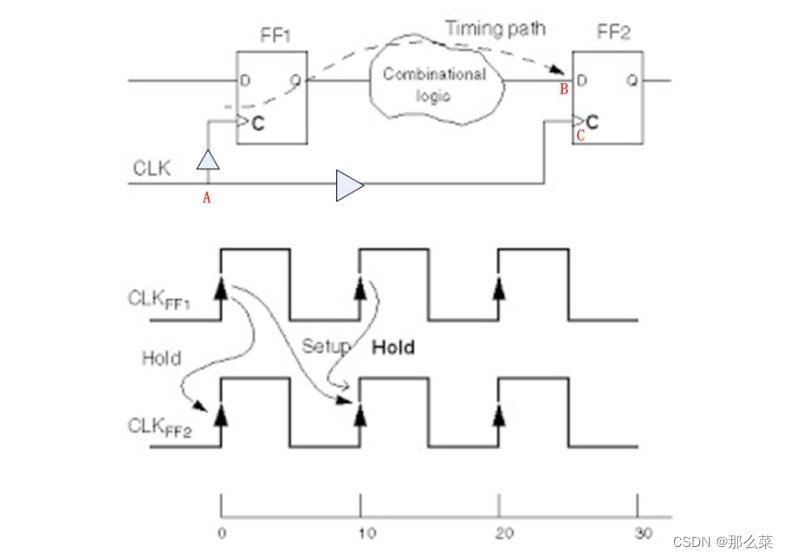

3.2 保持时间计算

保持时间比较难理解,其实质是:当前时钟沿的FF1输出不能太快在当前沿到达FF2。以上图为例,即在t10时刻,为防止FF1采到的新数据太快到达FF2而“冲掉”原来的正确数据,数据必须要在一定时间之后才允许到达,所以保持时间分析,分析的是FF1和FF2的同一个时钟沿。因为datapath和clk_path要满足保持时间要求,所以:

Tdata_path– Thold >= Tclk_path

所以:

Tclk_delay_FF1 + Tc->q_FF1+ Tcomb_logic– Thold>= Tclk_delay_FF2

在STA分析时,不满足此公式的即为Holdviolation。

其中Tclk_skew =Tclk_delay_FF2– Tclk_delay_FF1. 这条公式在分析Tskew时用得上。

对应于时序图,见如下图的分析:

四 实际计算举例

因为在不同的情形下,例如不同的温度,电压,loading等等,每一段电路的delay是不同的,所以对于同一段电路,其delay可以在如下范围中:

Min_delay<= Delay <= max_delay

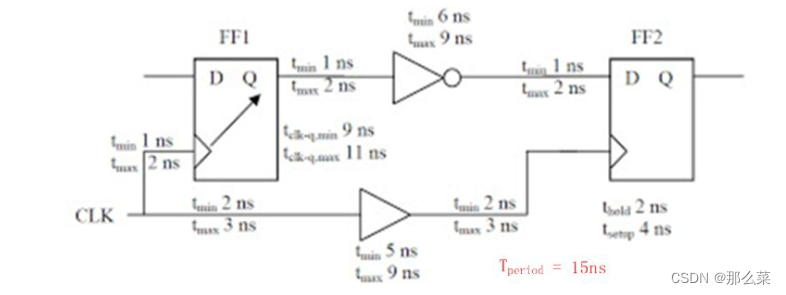

如下图:

4.1 建立时间

公式为: Tclk_delay_FF1 + Tc->q_FF1+Tcomb_logic+ Tsetup <= Tclk_delay_FF2 + Tperiod

应该满足MAX_data_path_delay + Tsetup <= MIN_clk_path_delay + Tperiod,才能保证电路是可靠的。

所以在实际电路中:Tdata_path_max+ Tsetup <= Tclk_path_min+ Tperiod

对应上图,该公式应该是:

2ns+ 11ns + 2ns + 9ns + 2ns + 4ns <= 2ns + 5ns + 2ns + Tperiod

所以: 30 <= 9 + 15.因为违反了该公式,所以该电路出现了setup violation。

4.2 保持时间

公式为: Tclk_delay_FF1 + Tc->q_FF1 + Tcomb_logic –Thold>= Tclk_delay_FF2

应该满足 MIN_data_path_delay – Thold>= MAX_clk_path_delay.才能保证电路是可靠的。

所以在实际电路中:

Tdata_path_min- Thold >= Tclk_path_max

对应上图,该公式应该是:

1ns +9ns + 1ns + 6ns + 1ns – 2ns >= 3ns + 9ns + 3ns

所以: 16ns >= 15ns,满足公司要求,所以该电路无holdviolation。

在某些电路中,可以认为clk tree上面没有延迟,可以认为wire没有延迟,那么setup和hold公式就得到简化。

版权说明:纯为提升自己,不为盈利, 勿喷~

转自Setup 和Hold (建立时间和保持时间)解析_setup hold-CSDN博客

五 其它概念

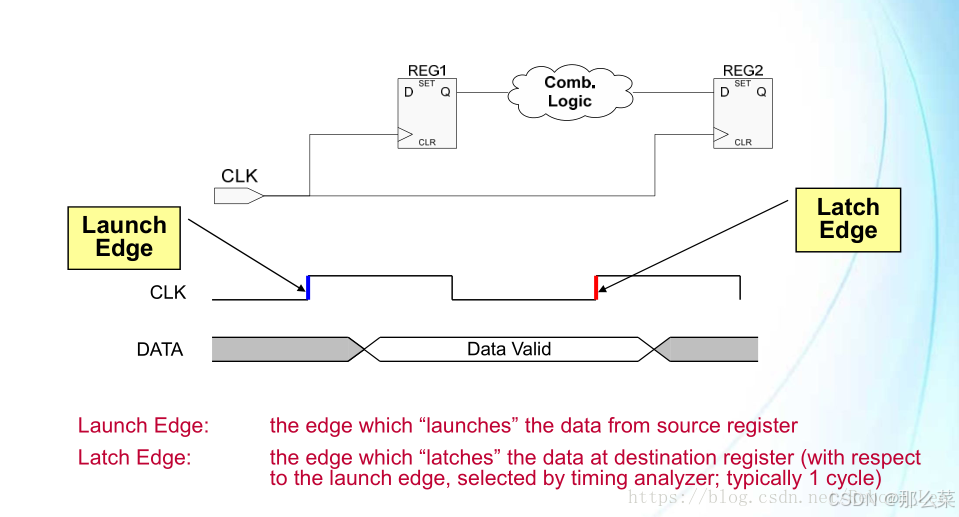

5.1 发射沿 Launch Edge

时序分析起点,第一级寄存器数据变化的时钟边沿,也是静态时序分析的起点

5.2 锁存沿 Latch Edge

时序分析终点,数据锁存的时钟边沿,是静态时序分析的终点

5.3 数据输出延时 Tco

数据输出延时指的是当时钟触发(一般可认为是第一个寄存器的时钟沿触发时刻)开始到有效数据输出**(第一个寄存器的Q端数据开始输出(有可能变化,也有可能不变化))**的器件内部所有延时的总和。

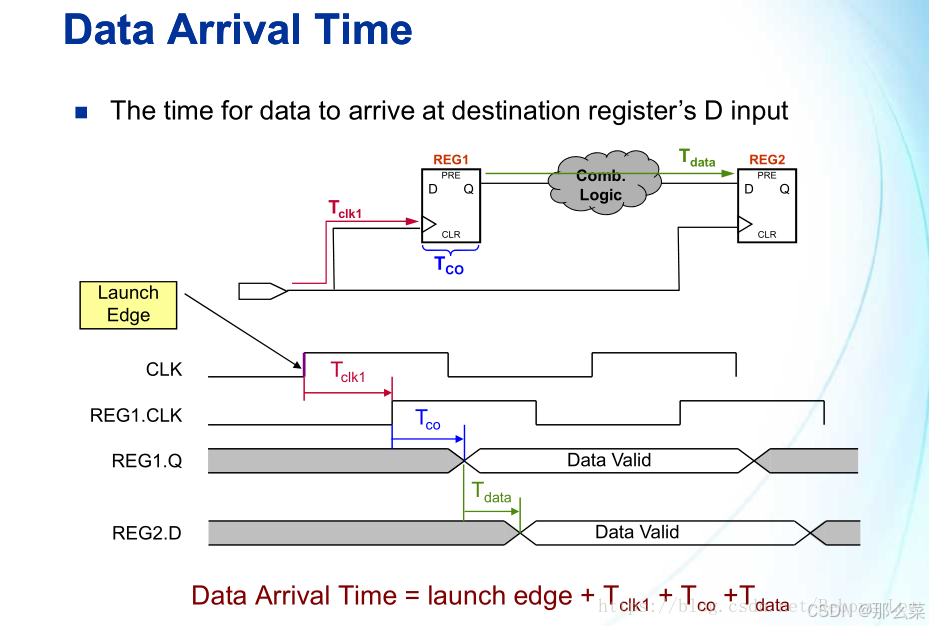

5.4 数据到达时间(数据路径,Data Arrival Time)

输入数据在有效时钟沿后到达目的寄存器所需要的时间,可大致划分为:时钟沿到达第一级寄存器所需时间(Tclk1),寄存器内部延迟时间(Tco),数据输出后传输到第二级寄存器所需时间(Tdata).

其中Tdata可细分为:

组合逻辑延时Tcomb_logic:数据经过组合逻辑部分所需的时间;

线网延时Tnet:数据在线上传输所需的时间,一般较小可以忽略;

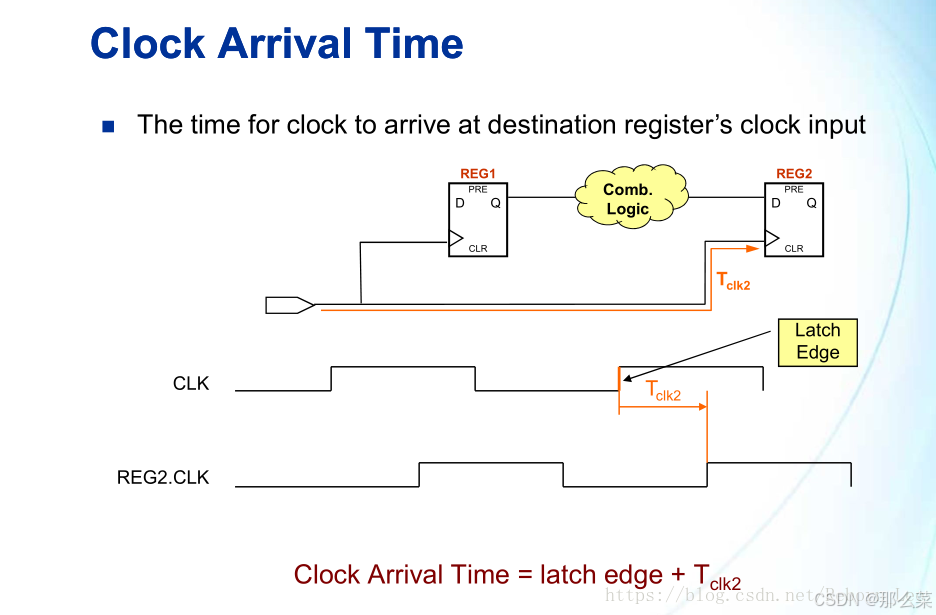

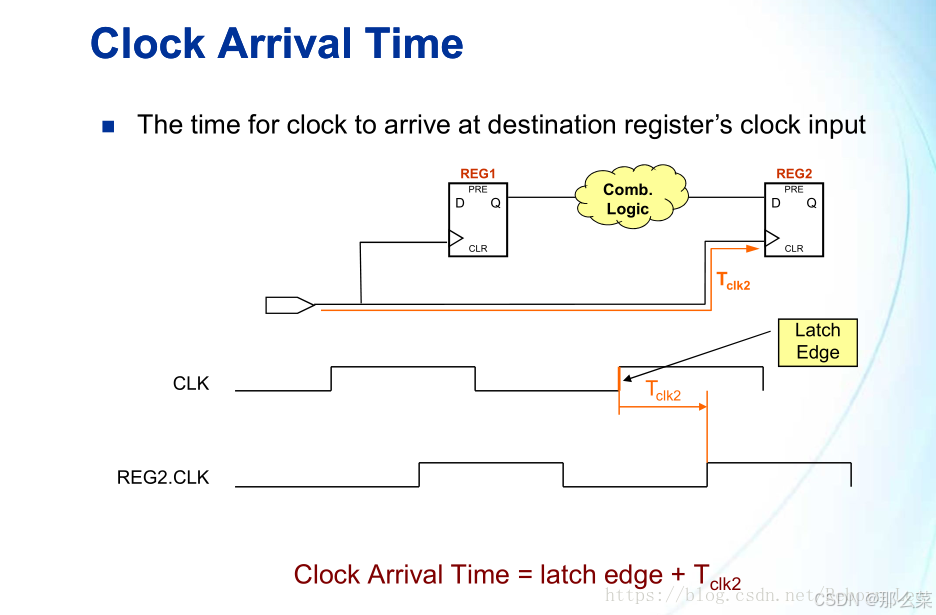

5.5 时钟到达时间(时间路径,Clock Arrival Time)

时钟到达时间就是指时钟从latch edge到达目的寄存器(destination register)输入端所用的时间。

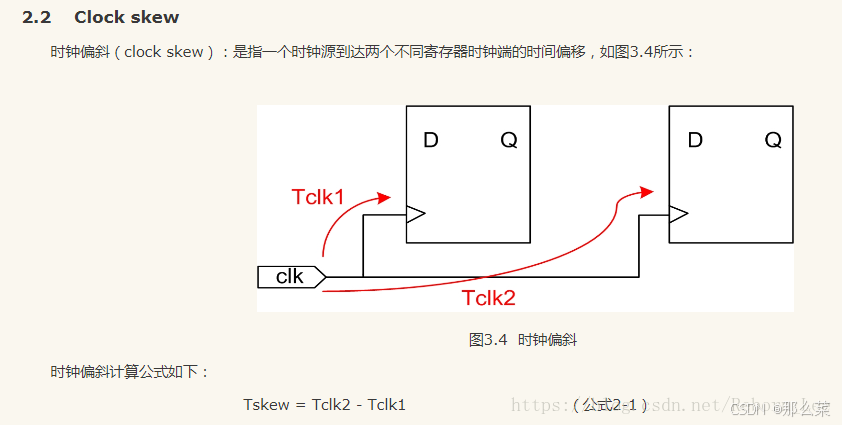

5.6 时钟偏斜(Tskew)

指同一个时钟沿(clk)和分别到达两个寄存器所需的时间之间的差值(Tclk1和Tclk2的差值).

公式为:Tskew=Tclk2-Tclk1.

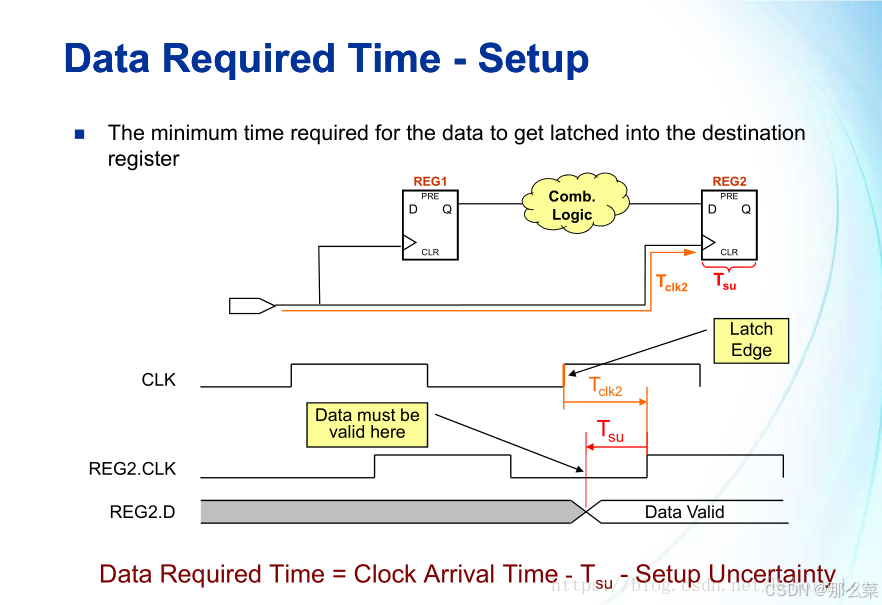

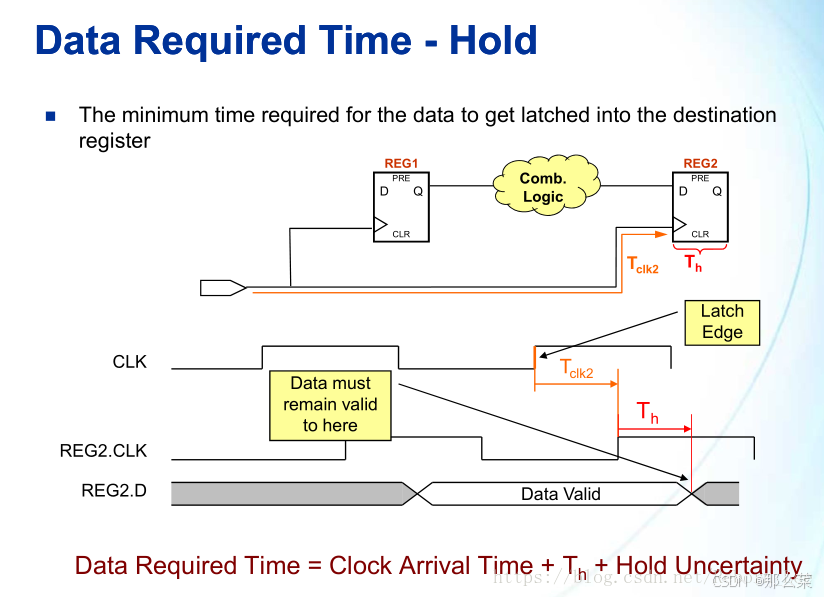

5.7 数据需求时间(Data Require Time)

细分为 :(Setup-Data Require Time)( Hold-Data Require Time )

①Clock Arrival Time = Latch +Tclk2

因此 Data Required Time = Latch+Tclk2-Tsu (忽略建立不定态)

②Clock Arrival Time = Latch +Tclk2.

因此 Data Required Time = Latch+Tclk2+Tsu (忽略保持不定态)

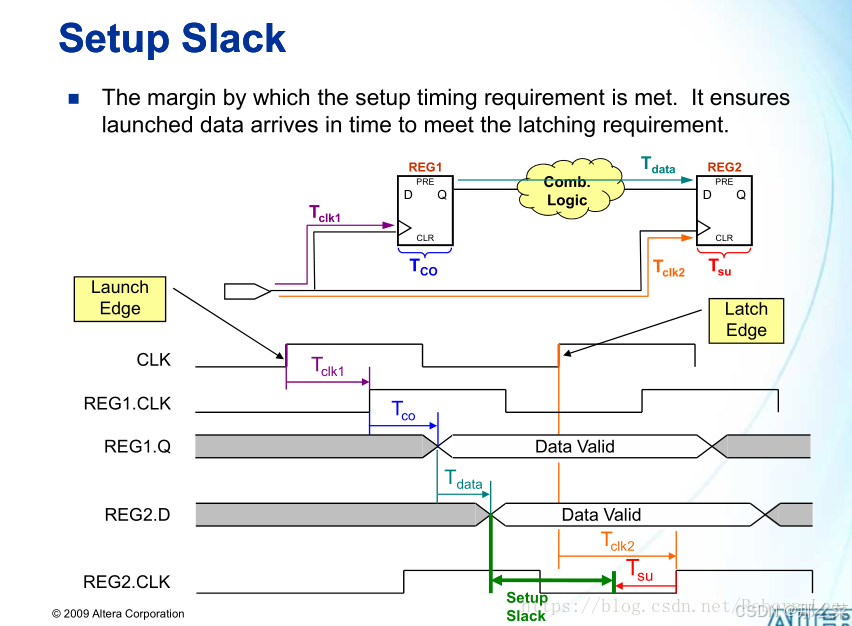

5.8 建立裕量(Setup Slack)

Setup Slack = (Latch Edge + Tclk2 - Tsu)-( Launch Edge + Tclk1 +Tco +Tdata)

(建立数据所需时间)Setup-Data Required Time = Latch Edge + Tclk2 - Tsu

(数据到达时间) Data Arrival Time = Lauch Edge + Tclk1 + Tco + Tdata

因此 Setup Slack = Setup-Data Required Time - Data Arrival Time

=(Latch Edge - Launch Edge)+(Tclk2-Tclk1)-(Tsu+Tco+Tdata)

= Tperiod +(Tclk2-Tclk1)-(Tsu + Tco+Tdata)

这个最终结果说明了源寄存器与目的寄存器之间延迟 Tdata不能太长的原因,延迟越长,slack越小。当建立裕量为正时,满足时序要求,否则不满足。

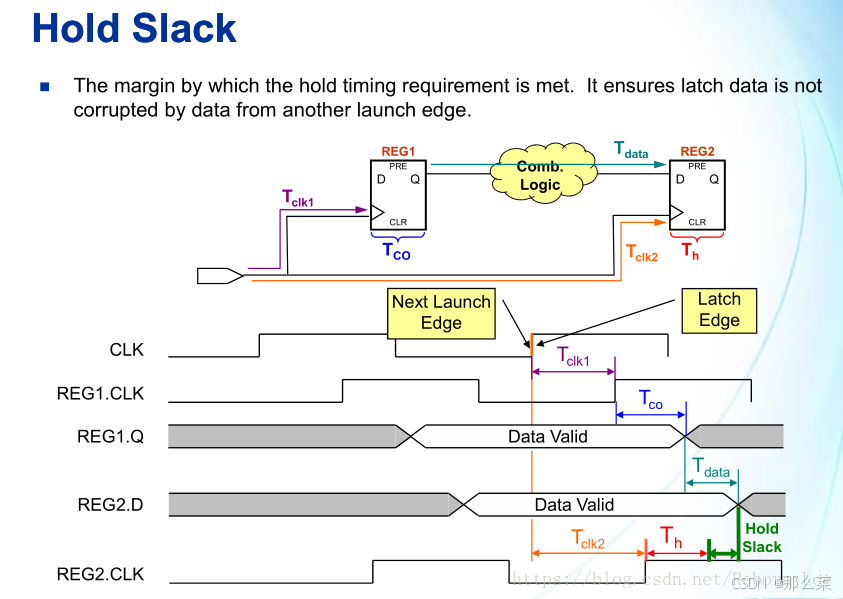

5.9 保持裕量(Hold Slack)

Hold Slack = Data Arrival Time - (Hold-Data Required Time)

同样的可推导:

(数据到达时间)Data Arrival Time = Launch Edge + Tclk1 + Tco + Tdata

(数据需求时间)Hold-Data Required Time = Latch Edge + Tclk2

Hold Slack = Launch Edge + Tclk1 + Tco + Tdata -(Latch Edge + Tclk2)

=-Tperiod +(Tclk1-Tclk2)+Tco+Tdata

从结果可以看出,当源寄存器与目的寄存器之间延迟Tdata太短的话,则保持裕量会很短,因此Hold Slack 越小。

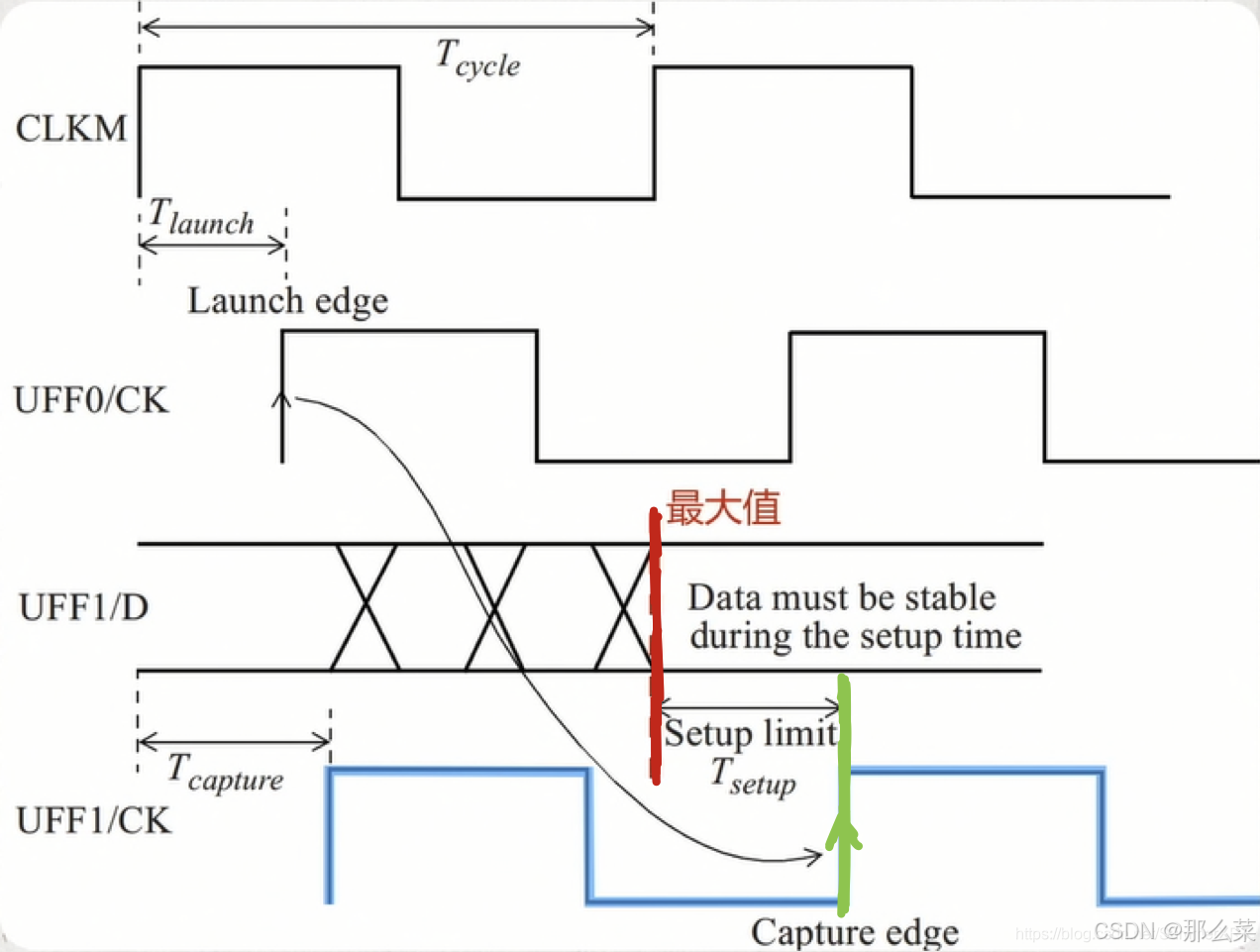

5.9 建立时间和保持时间的检查

解释图中的符号:

Tlaunch:时钟源点到第一个触发器的时钟网络延迟,也就是时钟偏斜(skew);

Tcapture:为时钟源点到第二个触发器的时钟网络延迟,也就是时钟偏斜(skew);

Tck2q:是触发器的延迟,即D端到Q端的延迟,这是由触发器本身的电气特性所决定的;

Tcycle:是时钟周期,即时钟频率 1\fclk;

Tdp:是第一个触发器的输出端到第二个触发器的输入端之间的组合逻辑电路部分的电路延迟;

解释上图,第二个触发器要想满足setup time,就必须要满足:

上图中绿色竖线为时钟源点经过延迟,到第二个触发器的时间(对应绿色路径)

对应红色的路径部分,经过组合逻辑,到达第二触发器的Q端,最晚只能到达上图的红色竖线部分,否则就没办法,满足建立时间。

由此,我们可以推迟公式:

Tlaunch + Tck2q + Tdp ≤ Tcapture + Tcycle - Tsetup

因为Tlaunch和Tcapture都表示为时钟偏斜(clock skew),所以我们合并之后就可得:

建立时间约束:Tsetup ≤ Tcycle +Tskew - Tdp - Tck2q

保持时间约束:Thold ≤ Tdp + Tck2q

其中参数意义:

Tclock:也就是时钟偏斜(clock skew);

Tck2q:是触发器D端到Q端的延迟;

Tcycle:是时钟周期,即时钟频率 1\fclk;

Tdp:是组合逻辑电路部分的电路延迟;

PS:这里可能你会觉得建立时间有点难记,我多啰嗦一句:

Tcycle + Tskew 是表示第二个触发器的时钟到达的时间;

Tdp + Tck2q是表示经过第一个触发器+组合逻辑到达的时间;

二者的差值就是建立时间最大的时间要求

解决建立时间与保持时间不满足的问题

1.建立时间不满足

当建立时间不满足时,即Tsetup值要大于实际的Tcycle +Tskew - Tdp - Tck2q,为了满足建立时间:

可以通过改进工艺,采取具有更小的Tsetup值的芯片;

采用延迟更低的触发器,降低Tck2q;

增大时钟周期Tcycle和时钟偏斜Tskew,但这会降低电路的性能;

尽量减小两个触发器之间的组合逻辑电路的使用,从而降低Tck2q。

2.保持时间不满足

当保持时间不满足时,也就是Thold要小于Tdp + Tck2q,可以通过:

理论上,可以增加Tdp和Tck2q来解决,也就是增加触发器的D端到Q端的延时,以及两级触发器之间的组合逻辑电路部分。

目前大部分芯片的Thold时间都可以做到0ns。所以当保持时间不满足时,通常采用的做法是在传输路径上插入buffer,在不影响逻辑功能前提下,只具有增加延迟的作用。

PS:尤其注意,保持时间Thold和时钟频率之间是没有关系,故降低时钟速度不能解决保持时间不满足的问题,很多面试题喜欢在这里挖坑。

恢复时间 Recovery time

是指异步控制信号(如寄存器的异步清除和置位控制信号)在“下个时钟沿”来临之前变无效的最小时间长度。

去除时间 Removal time

是指异步控制信号(如寄存器的异步清除和置位控制信号)在“有效时钟沿”之后变无效的最小时间长度。

时序路径

每个时序路径都有一个起点和终点。一般起点是时序单元的时钟引脚 或者设计的输入端口;终点是时序单元的数据输入引脚或者 设计的输出端口。所以一共有四种时序路径。

名词解释:

发射沿(launch edge):有效时钟的第一个上升沿;

采样沿(latch edge):有效时钟的第二个上升沿;

采样沿和发射沿差值可以粗略认为是1个时钟周期(不考虑时钟抖动jitter)。

Tclk1:时钟源扇出信号到寄存器1(REG1)的时钟端所需时间;

Tclk2:时钟源扇出信号到寄存器2(REG2)的时钟端所需时间;

所以时钟源的布局布线很重要,这就是为什么FPGA中推荐用PLL输出时钟,而不是自己进行时钟分频。

Tco:寄存器时钟输出延迟,即有效时钟输入到输出之间的延迟。

Tdata:2个寄存器之间组合路径延迟和布局布线延迟。

Tc:时钟周期大小(Tclk)。

Ts:建立时间大小;

Th:保持时间大小;

Thold_slack:保持时间余量(也就是要大于0);

Tsetup_slack:建立时间余量(也就是大于0)。

建立时间:

采样沿到达时间:Tlatch = Tc + Tclk2;

第一次数据到达时间:Tarrive = Tclk1 + Tco + Tdata;

建立时间大小:Ts = Tlatch - Tarrive = Tc + Tclk2 - Tclk1 - Tco - Tdata = Tc + Tdelta - T1.

其中,Tdelta代表Tskew,也就是2个寄存器之间时钟到达差值,T1代表从REG1到REG2数据接收端的整个时间延迟,当然,不化简也是可以的。

保持时间:

第一次采样沿到达时间:Tlatch = Tc + Tclk2;

第二次数据到来时间:Tdata2 = Tclk1 + Tco + Tdata + Tc(Tdata_valid) ;

保持时间大小:Th = Tdata2 - Tlatch = Tclk1 + Tco + Tdata - Tclk2 = T1 - Tdelta。

————————————————

版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

原文链接:https://blog.csdn.net/qq_44933149/article/details/126430341

1685

1685

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?