1. 上/下拉电阻定义

在电子元器件间中,并不存在上拉电阻和下拉电阻这两种实体的电阻,之所以这样称呼,原因是根据电阻不同使用的场景来定义,其本质还是电阻。就像去耦电容,耦合电容一样,也是根据其应用场合来取名,其本质还是电容。

上拉电阻(PU):在某信号(数据、时钟、控制、中断)线上,通过电阻与一个固定的高电平VCC相接,使其电压在空闲状态保持在VCC电平,此时电阻被称为上拉电阻。

下拉电阻(PD):在某信号线上,通过电阻与一个固定低电平GND相接,使其电压在空闲状态保持GND电平,此时的电阻被称为下拉电阻。

弱拉与强拉: 弱与强是一个相对概念,例如使用1K的上拉电阻和使用100K的上拉电阻,前者称为强上拉(电阻越小,离Vcc越近,拉信号的能力越强),强上拉使得信号抬升速度快,提供的负载电流大,后者称之为弱上拉。强下拉/弱下拉与上拉定义相同。

2. 上/下拉电阻运用

(1)当TTL电路去驱动COMS电路时,如果驱动端TTL电路输出的高电平低于负载端COMS电路的最低高电平(一般为3.5V),这时就需要在TTL的输出端接上拉电阻,以提高输出高电平的值。

(2)OC集电极开路/OD漏极开路门电路。 OC(Open-Collector)和OD(Open-Drain)门电路不具备输出高电平能力,表现为高阻态,但如果在集电极或者漏极上接一个上拉电阻,则OC/OD门电路具备了输出高、低电平的能力。

(3)单片机在驱动类似LED灯负载时,一般会使用上拉电阻去提高I/O的驱动能力。

(4)在COMS逻辑芯片上,由于内部逻辑门会同时开通和关闭,SSN噪声比较大,为了防止电磁干扰造成损坏,不用的管脚除非特殊申明不能悬空,一般上拉到电源或者下拉到地,产生较低输入阻抗,提供泄荷通路。

(5)电平转换芯片电路中,使用上拉电阻进行电平之间的转换。

(6)用在总线或者协议电路上,如IIC、485、JTAG等。提供各路信号确定电平。

(7)终端匹配。上下拉电阻经常用在高速电路中,进行终端匹配,一般分为并联端接和戴维南端接。

(8)在复位电路中,常见的Chip例如PHY的Reset 信号是低电平有效,这就需要在电路设计时将其下拉到地,以保证上电初始时将其按住,不让其工作,然后在板卡上电过程中将其解复位,通过MDC/DMIO去配置这个芯片。

3. 上/下拉电阻选型

(0)前提知识点:吸电流、拉电流和灌电流

电子元器件在广义上分为有源器件和无源器件。有源器件需要电源(能量)才能实现其特定的功能,比如运算放大器在有输入信号的前提下,如果不提供电源,运算放大器无法实现其放大功能。无源器件在工作时,不需要外加电源,只要输入信号就能正常工作,比如在信号线上串联33Ω的电阻,无论是否提供电源,只要有信号经过,电阻就能实现限流的作用。

通常定义流入器件的电流为正,流出器件的电流为负。

器件输入端有电流流进时,称为吸电流,属于被动;器件输出端有电流流出时,称为拉电流,属于主动;器件输出端有电流流入时,称为灌电流,属于被动

上下拉电阻的选型需要从多个角度考虑:

(1)驱动能力。从满足驱动端灌电流门限和负载端的吸电流门限考虑,如果上拉电阻太小,则可能灌电流超过驱动端的输出灌电流门限,如果上拉电阻太大,则可能驱动能力不足,输出电压达不到负载端的输入要求(门电路)或者输出电流达不到负载要求(例如LED)。

(2)功耗。从节约功耗及芯片的灌电流能力考虑应当足够大;电阻大,电流小,功耗低。

(3)信号速率(频率特性)。对于高速电路,过大的上拉电阻可能边沿变平缓(可将后级认为是容性负载,上拉电阻越大,形成的RC延时电路的充电时间常数越大,信号的上升/下降边缘更加平缓)

例如在OD门电路上拉电阻选型中,需要兼顾驱动能力、功耗和信号速率。

在信号速率考虑上,对于容性负载OD门下降沿比上升沿快(因为下降沿是芯片内部晶体管有源驱动,速度快,而上升沿是外部上拉无源驱动,需要对容性负载充电,速度慢),因此,如果对延时有要求,则建议用下降沿输出(I2C总线的开始和结束信号就是下降沿采样的)。

4. OD门上拉电阻阻值计算实例

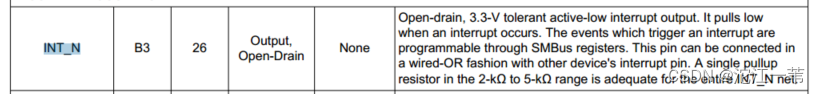

任务来源:板级电路上ASIC 的Serdes输出多路高速信号,每一路通过Retimer 中继到板卡外部接口,多路Retime芯片的INT_N管脚通过线与逻辑上拉电阻的方式连接到主控FPGA的一个IO口,要求对这个上拉电阻进行选型。

分析: INT_N是OD门输出,由每一个Retimer 输出到主控芯片的中断信号(Interrupt Signal),当信号被触发时输出为低。同时PU电阻功耗与整板功耗相比微乎其微,因此电阻不用考虑信号速率与功耗,需要重点考虑上拉电阻要满足驱动能力的要求。

电路模型简化成下图所示

计算

(1)RL max

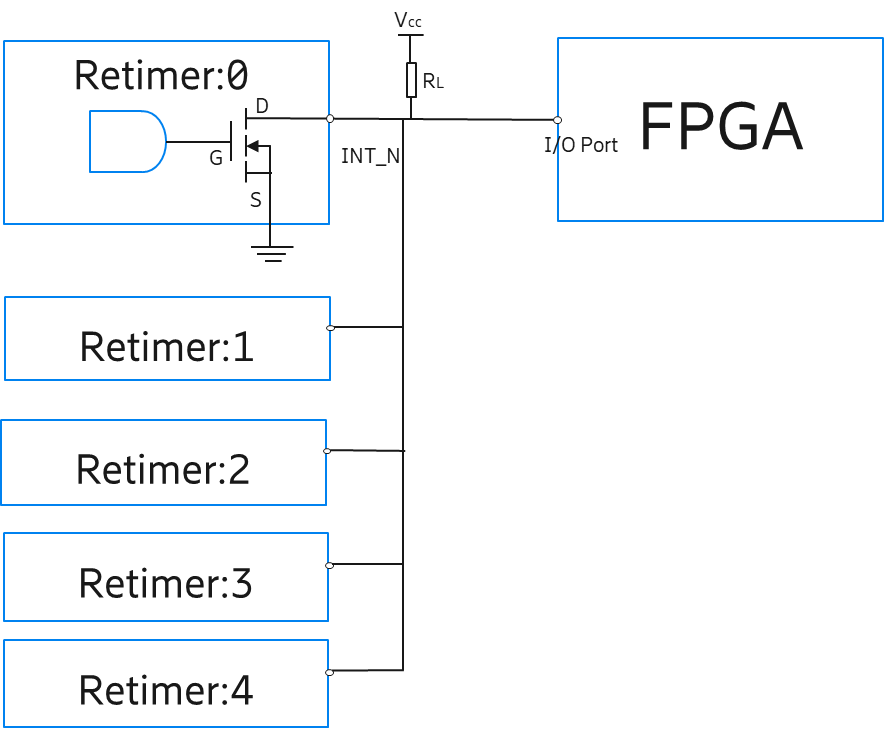

当所有OD门同时截止,均输出高电平,内部管截止时漏电流为Ioh,同时负载FPGA的输入端的吸电流为Iih。此时电流流向如图所示

根据KCL定律,可以得到流经电阻RL 的电流方向 Ir= m*Ioh + Iih, m=5

(Iih 为负载端口输入为高电平时的最大输入电流)

要求输出的高电平不得低于负载输入高电平时的下限Voh,上拉电阻不能过大,可以得到

Vcc — (m*Ioh + Iih)RL ≥ Voh,

则 RL ≤ (Vcc —Voh) / ( mIoh + Iih)

(2)RL min

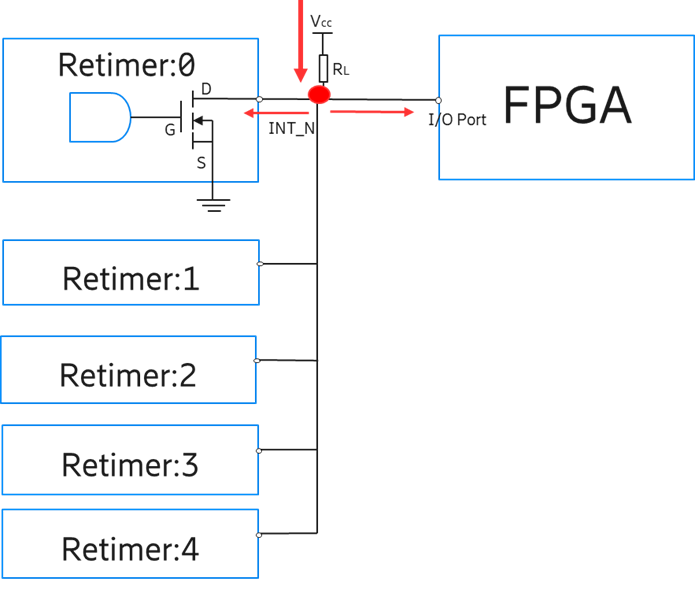

当输出为低电平时,并且并联的OD门当中只有一个门的输出MOS导通,则负载电流将全部流入该导通管,同时负载FPGA端的IO口电流不能超过低电平输出电流的最大值Iil.为了保证驱动端电流不超过OD门MOS管允许的最大饱和电流,RL值不能太小。此时电流流向如下图所示

根据KCL定律,流到导通MOS管的电流 I in = Ir+ Iil,

(Iil 为负载端口为低电平时的最大输出电流)

要求保证该电流不超过MOS管允许的最大饱和电流Iol,可以得到

(Vcc — Vol ) / RL + Iil ≤ Iol,

则 RL ≥ (Vcc —Vol) / ( Iol — Iil)

综合以上,RL取值范围是

(Vcc —Voh) / ( m*Ioh + Iih) ≥ RL ≥ (Vcc —Vol) / ( Iol — Iil)

在本案例中,m=5, Vcc = 1.8V

在CMOS 电平标准中, Voh = 0.7Vcc , Vol = 0.3Vcc

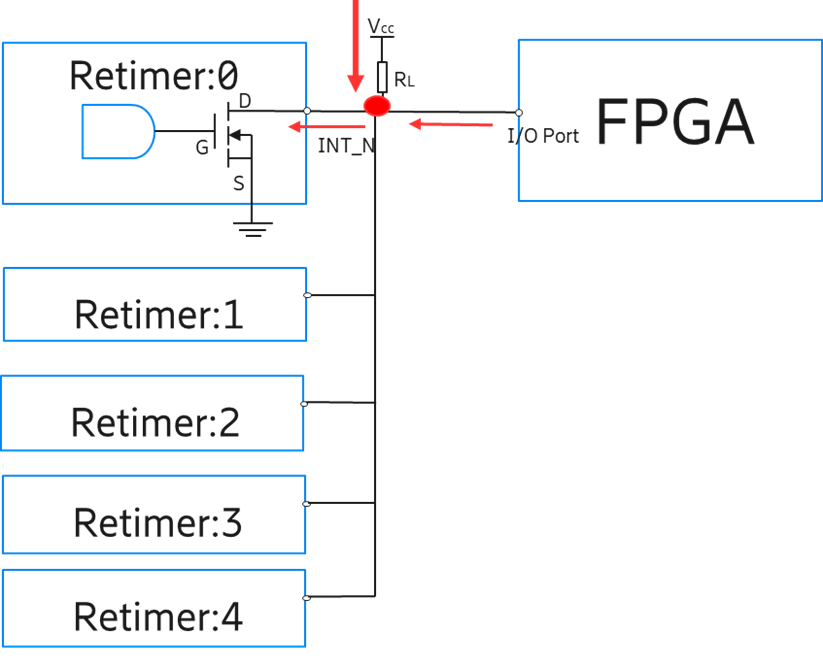

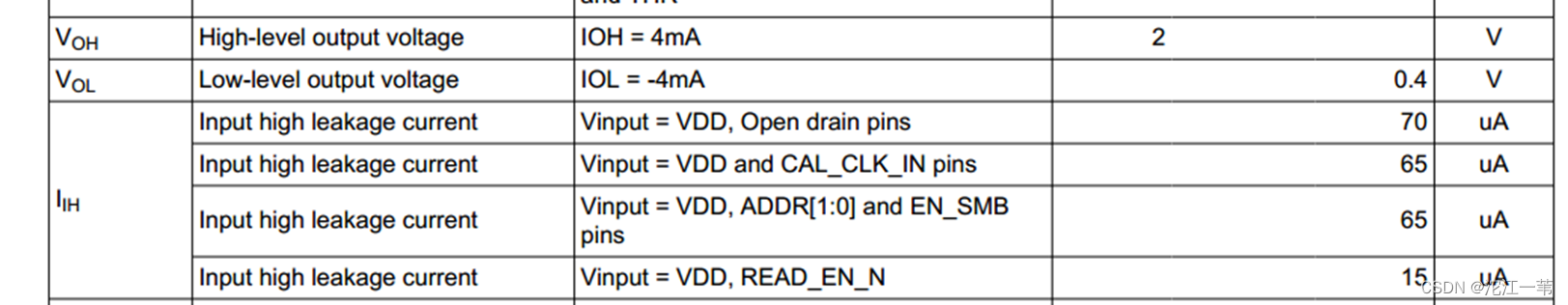

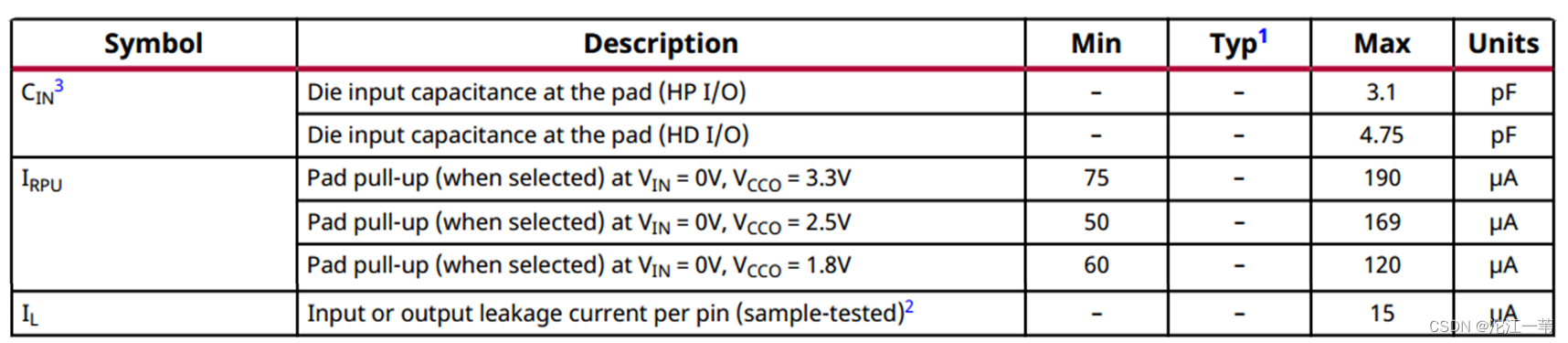

查找Retimer 和 FPGA芯片的Datasheet, 得到其他参数取值

I oh = 70uA, I ol = 4mA

I ih = 60uA, I il = 15uA

将上述参数带入到公式中,可以得到 1.31KΩ ≥ RL ≥ 316Ω

因此上拉电阻 RL 建议选择0402封装的1K电阻,可以保证INT_N 信号驱动能力满足要求。

5. 参考

[1] TI,Choosing an Appropriate Pull-up/Pull-down Resistor for Open Drain Outputs

[2] 清华大学电子学教研组,数字电子技术(第六版)

本文详细介绍了上拉电阻和下拉电阻的概念、作用,以及在TTL与COMS电路、OC/OD门电路、单片机驱动、总线协议和复位电路等场景中的应用。选型时需考虑驱动能力、功耗和信号速率等因素,文中通过具体实例展示了如何计算OD门上拉电阻的阻值。

本文详细介绍了上拉电阻和下拉电阻的概念、作用,以及在TTL与COMS电路、OC/OD门电路、单片机驱动、总线协议和复位电路等场景中的应用。选型时需考虑驱动能力、功耗和信号速率等因素,文中通过具体实例展示了如何计算OD门上拉电阻的阻值。

439

439

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?