1. 问题背景

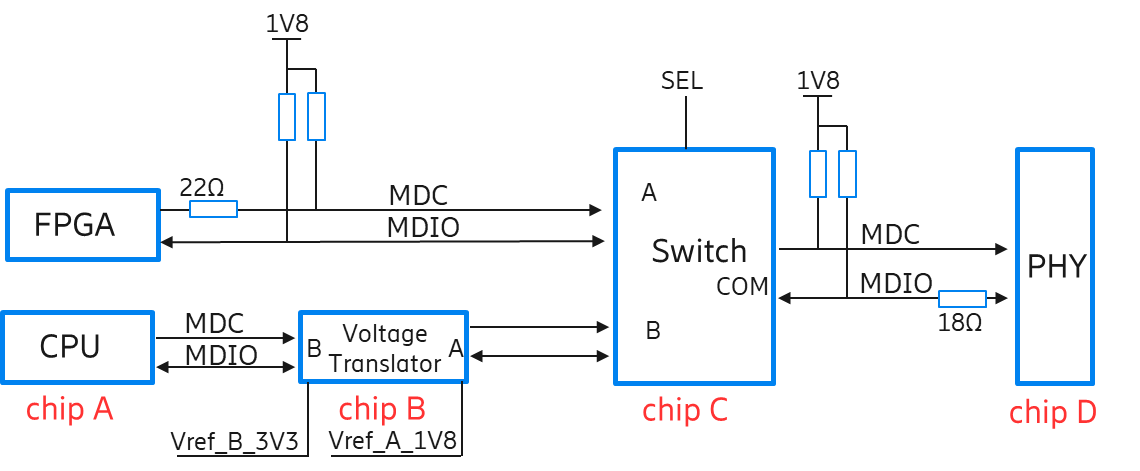

任务来源:在某单板硬件电路上,MDIO topology如图所示。主芯片CPU与FPGA都可以作为总线Master去驱动作为Slaver的PHY芯片,链路中采用Switch 去选通CPU 或者FPGA。由于CPU与PHY的工作电平不匹配,需要在CPU与Switch 之间使用电平转换芯片,将3V3转成1V8。当下由于供货原因,在对Voltage Translator 进行选型时,将之前使用TI LSF01系列替换成PCA93系列。在替换之后,当CPU作为MDIO Master时,测量PHY芯片的MDIO Pin管脚处发现有信号过冲,初步分析是由于整个链路阻抗不匹配导致,需要添加一个串阻,试问串阻应该加在什么地方?

分析:

将有SI问题的传输链路上的经过的芯片分别用chip A,B,C,D表示。MDIO 信号由chip A的MAC Controller 发出,经过chip B 和 chip C, 到达chip D输入侧。

1,对于Switch, 因为FPGA的MDC/MMDIO信号同样经过Switch 没有SI问题,可以认为Switch 芯片对于信号来讲没有阻抗作用,通过分析datasheet, 该芯片的模型是一个电荷泵+CMOS传输门,没有re-driver能力,Ron非常小,可以认为信号是bypass通过。

2,如果A→B→C→D可以看做一条阻抗平坦的信号链路,则只需要在信号的发送端串联一个电阻即可,由于MDIO信号是双向的,PHY侧已经做好阻抗匹配,这样只需要在chipA侧串接电阻进行阻抗匹配。

3,如果信号在经过每一个器件后被重构,则需要分别保证A-B,B-C-D链路阻抗匹配正确,在这种情况下,Chip D 的input Pin测量到overshoot 过冲,串阻应该加在chip B 的output处。

4,因此,对于chip B: Voltage Translator 来讲,信号/过冲 能否直接通过电压转换器进行传输,换句话说,电压转换器是否将输入信号的overshoot消平钳位然后传输,就成为一个关键问题。

2.电压转换器工作原理

2.1 电压转换需求

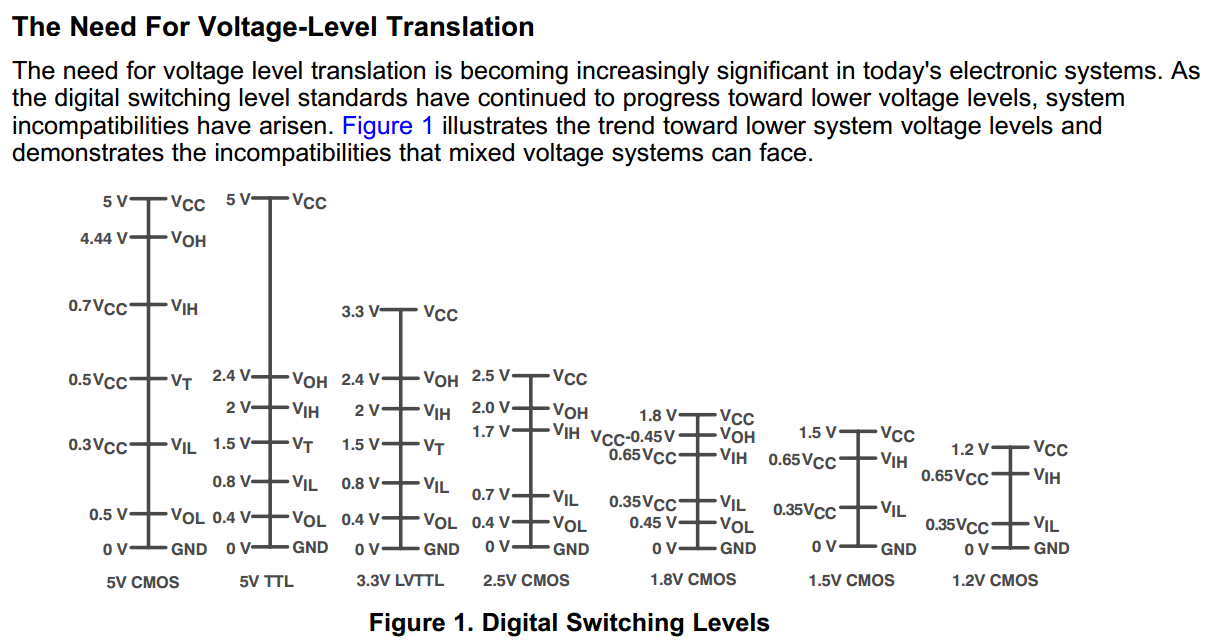

在当下的电路设计中,电压电平转换的需求正变得越来越重要。 随着数字开关电平标准不断向较低的电压电平发展,电平之间不兼容性出现。 这时,就需要电压转换器将电平进行正确匹配。

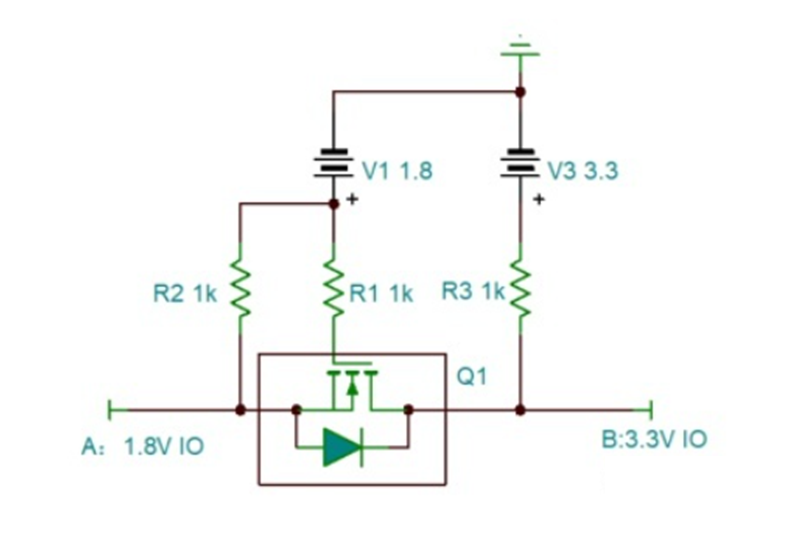

2.2 单个NMOS电路

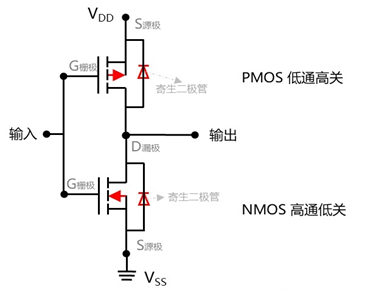

要分析 Voltage Translator 电压转化器的工作原理,先来复习下单个NMOS设计的最简单的双向逻辑电平转换电路(一般使用PMOS管作信号开关电路,NMOS做电平转换电路),如图所示

工作原理,图中Q1为N型增强型MOS管,当Vgs >Vth(gs)时,MOS管导通

A端(MOS管S极)接1V8信号,B端(MOS管D极)接3V3信号:

A→B:当A端为1V8高电平时,Q1截止,B端被上拉至3V3高电平

当A端为0V低电平时, Q1导通,B端为低电平

B→A:当B端为3V3高电平时,Q1截止,A端被上拉至1V8高电平

当B端为0V低电平时, MOS管内体二极管导通,A端电压下降,当下降至

Vgs>Vth(gs)时,Q1导通,A端为低电平

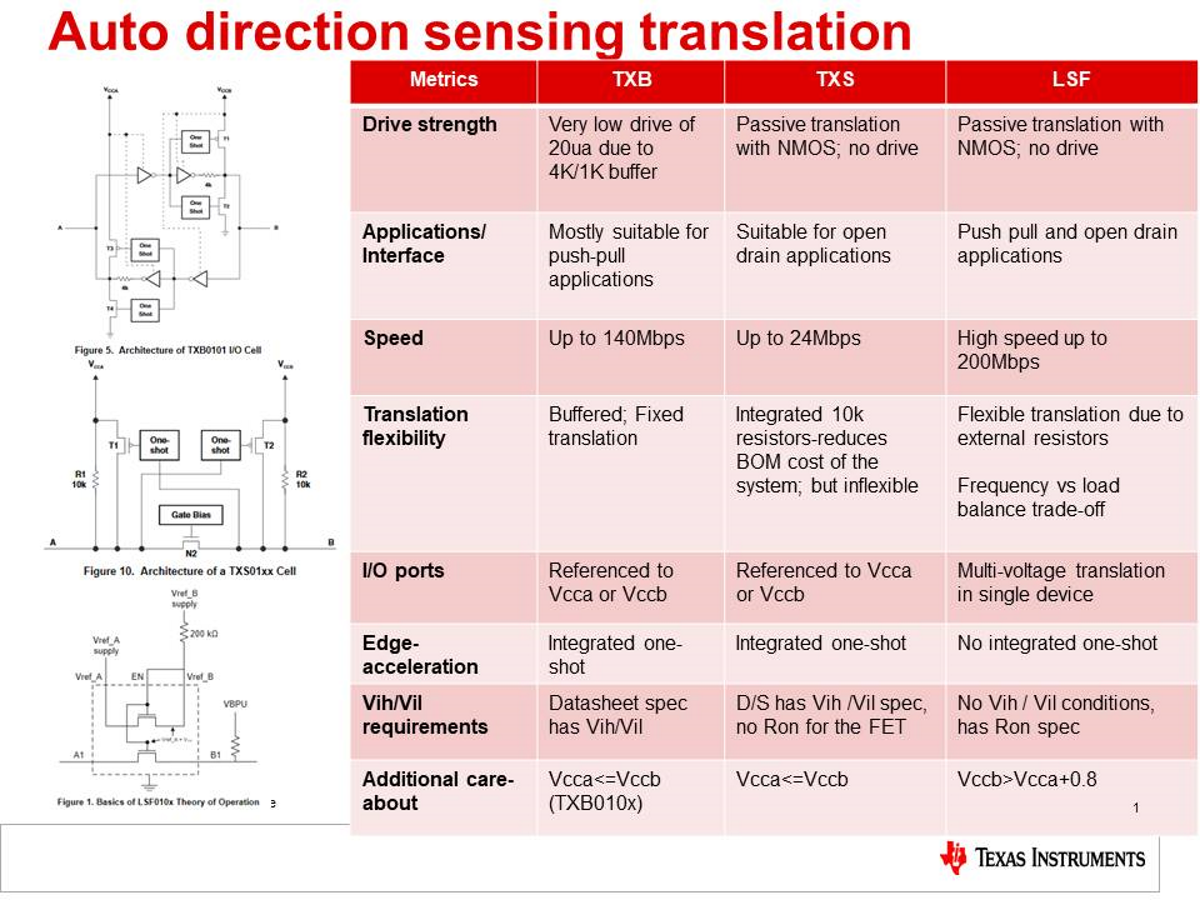

2.3 IT Voltage Translator 家族

单个NMOS管组成的电压转换电路,适用于简单的push-pull 电路与OD门电路(需要加上PD)。但是要考虑到信号转换时的动态特性足够好,需要使用到专业的电压转换芯片,IT公司生产的bidirectional voltage translator 大致分为三类

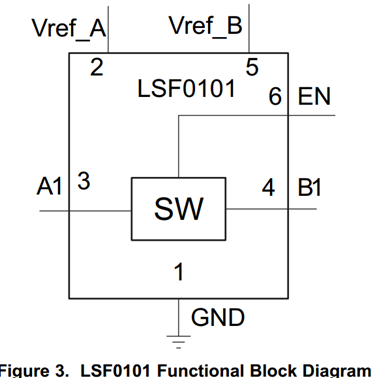

查看LSF01xx 系列的datasheet,内部框图如下图所示

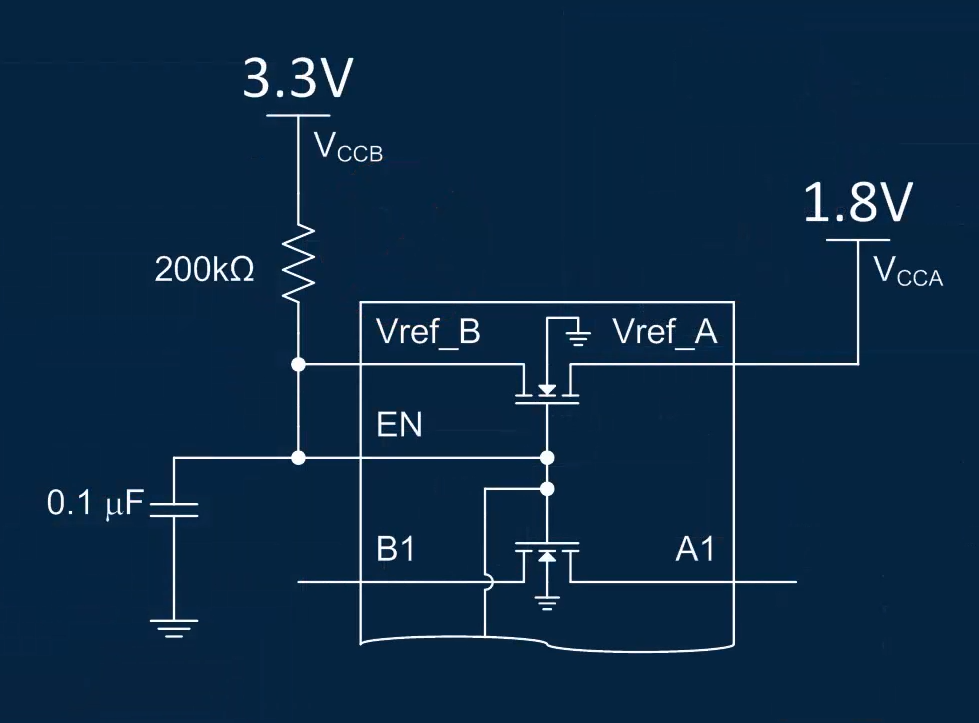

通过TI官网再次查看该芯片的使用指南,其芯片内部模型如下图所示,使用了两个衬极接地的NMOS管,其D极与S极可以互换,是一个完全对称的MOS。

工作原理,从图中的上部分MOS管可知,EN脚的电压为Vcca加上V(gsth), EN 信号又作为下部分MOS管的Vgs。考察信号切换时的响应过程

A→B,

(1)当A from Vcca to 0,V(gs)逐渐大于导通门限V(gsth),MOS管开始导通,B→0,AB之间的Ron = 1/∞

(2)当A from 0 to Vcca , 由于初始B=0,MOS管导通,A端从0上拉至Va,B端开始上拉至Vcca,MOS管关断,B端继续上拉至Vb。

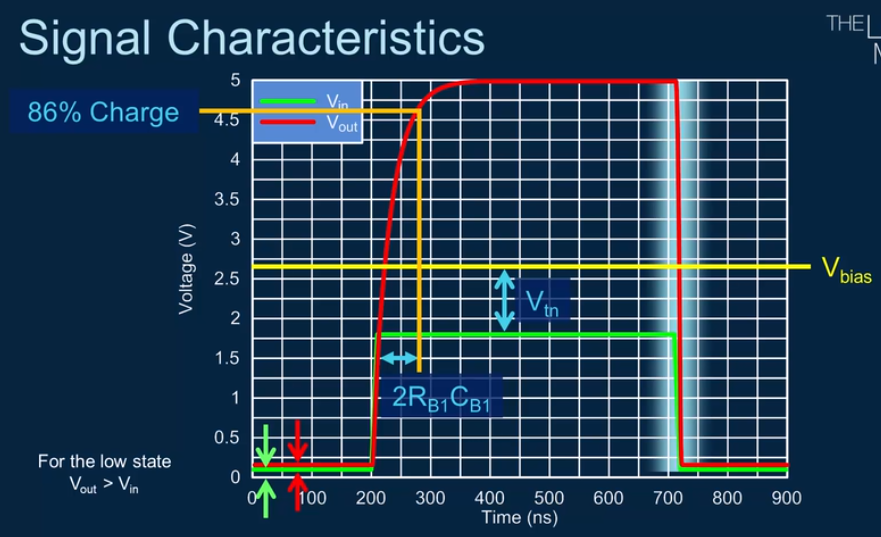

信号的输出-输入曲线如下图所示

B→A,分析过程与A→B相同

3. 传输线长度与过冲

在分析完电压转换器的工作原理之后,回头再来看一下信号过冲相关知识。

信号在传输的过程中,往往不是标准的矩形波信号,尤其在高速信号中,保证信号的完整性是十分重要的,而影响信号完整性最主要的因素之一,就是阻抗不匹配,通常表现在传输线上,而阻抗不匹配直接导致信号的反射,反射信号量与原始信号叠加,就会产生过冲、回沟、台阶等信号完整性问题。信号的反射量,如果作用在信号的上升爬坡阶段,则容易产生回沟或者台阶;如果叠加在上升高电平或者低电平处,表现为信号的过冲或振铃。

当我们评估过冲,主要考虑的因素是:过冲的最大幅值、过冲的持续时间、过冲的发生频率。

当我们谈及信号的反射,主要考虑的是反射量的大小、反射发生的时间、反射发生的次数。

根据反射模型,信号第一次反射量的大小与传输线的长度无关,只与反射系数相关。而反射发生的时间与反射发生的次数,都与传输线长度有关。

我们用示波器在传输线末端进行测量,其测量值是信号传播到传输线末端的幅值与当前反射幅值的叠加。如果源端没有做好阻抗匹配,反射会发生多次,如果源端做好阻抗匹配,信号从源端出来以半幅值输出,全反射只会在末端发生一次。末端测量的就是信号传输值与全发射的叠加(这里提前是需要信号线上升时间 or 信号周期与传输线的长度在同一尺度, 即信号一次电平翻转爬升,与信号在传输线上走的时间正好同时达到)。

因此,如果传输线特别短(或者信号上升时间特别长),在末端测量到的就是就是信号传播值与多次反射的叠加。如图4-64所示Td=40ps,此时也就不需要考虑加源端阻抗匹配了。对应的就是chip B: Translator 到chip C: Switch 这一段。

4. Translator 与过冲

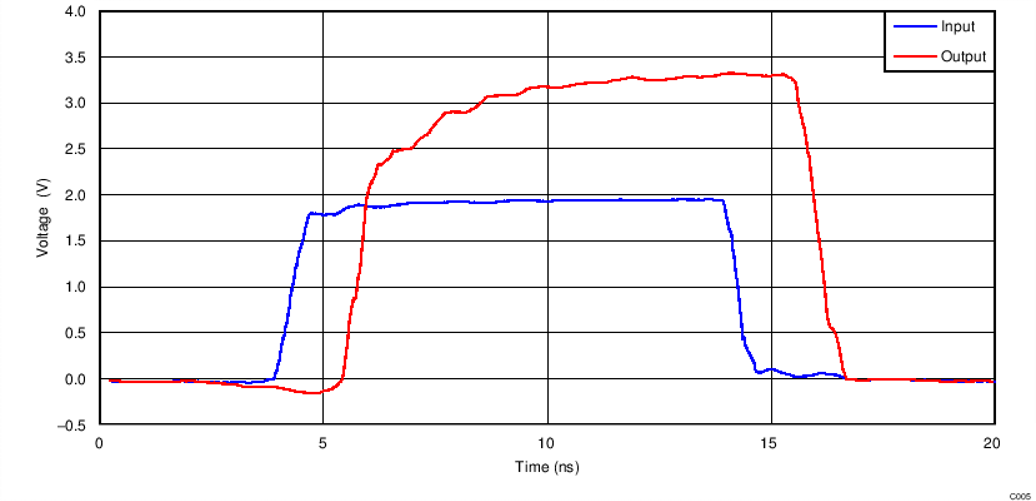

Translator 有它自己的动态参数,上升下降时间的典型值与输入的信号动态参数并不匹配,它是一个有源器件,不能被当做一个小电阻看待。器件的输出曲线与输入曲线并不完全一致,输出的上升沿消除了高频分量,因此在后续链路上的串扰的产生,应该由Translator 承担一部分责任。

但是,从传输线的长度与过冲这个因素考虑,chip A 到chip B的传输距离是301mm,在FR4板材上走线对应的信号延迟是2ns;而chip B 到 chip C的传输距离只有10mm,对应信号传输延迟是66ps。 而MDIO信号以最大频率125M计算,上升时间一般取周期的10%则是800ps。因此chipA到chipB这一段的走线长度对信号振铃的影响应该重点考虑,则串阻应该加在chipA的输出端。

复习知识点1.芯片的静态特性与动态特性

芯片静态特性:当器件处于稳定状态时,输入输出曲线

动态特性:当器件处于转换状态时,传输延时、交流噪声容限,动态功耗等参

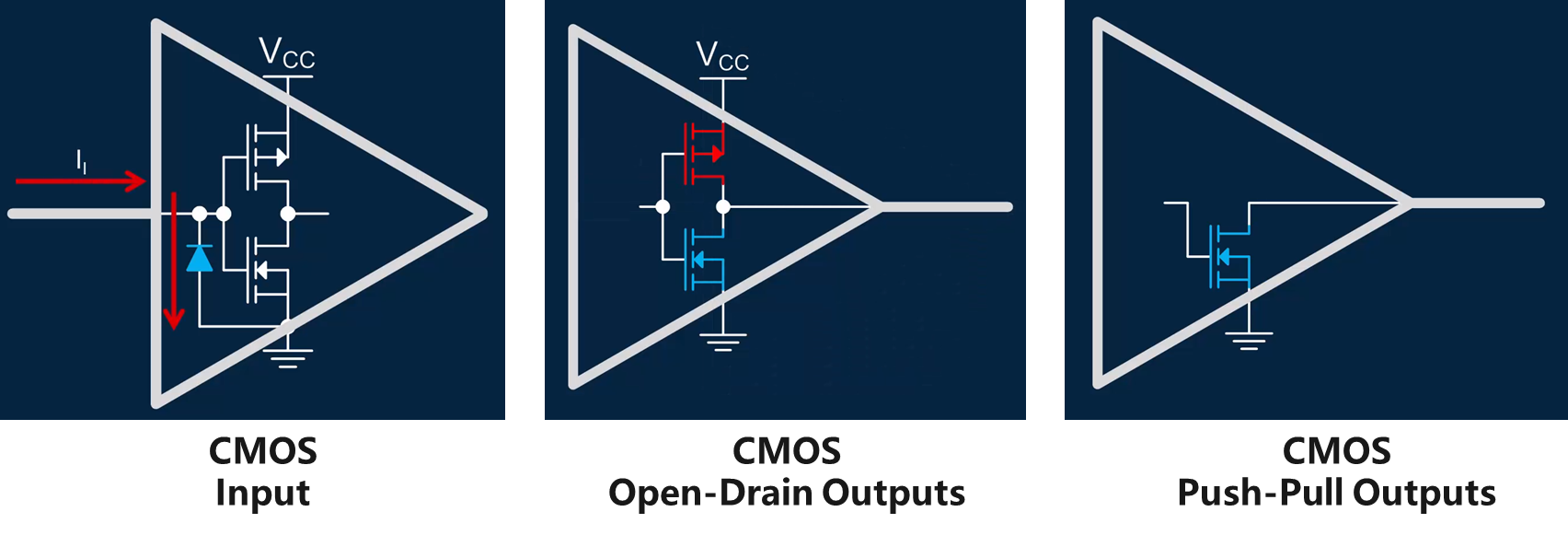

复习知识点2. CMOS门电路

注释2 CMOS门电路、CMOS 输入与输出

CMOS输入与输出的示意图

复习知识点3. 开漏输出与IIC总线

推挽输出是不可以“线与“的,”开漏输出可以线与,只要任意一个开漏门信号为低电平,总线就是低电平,电流通过上拉电路经过打开的开漏门流进到地。所有门全部为高电平时,总线为高电平,当一个门为低电平时,总线为低电平。

这也解释了IIC的电平逻辑,Master 可以通过IIC总线和通过线与逻辑挂载的多个IIC Slaver进行通信。一开始SDA总线为高电平,此时所有的IIC slave 都是等待状态,SDA总线为高。然后IIC Master 将SDA线拉低,第一个bit 为0,接着写某一个7位或者10位的IIC slave 地址,然后后释放SDA总线,电平又被拉高,再跟一个读写位0写/1读,当被选中的器件在确认是自己的地址后,在第9个bit把SDA拉低,这个应答信号做为响应,单片机接收到后,就可以开始传输数据了。

复习知识点4. 改善过冲的另一种方法:调节输出能力

5 参考文献

TI. 电压电平转换指南 http://www.ti.com/voltageleveltranslation

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?